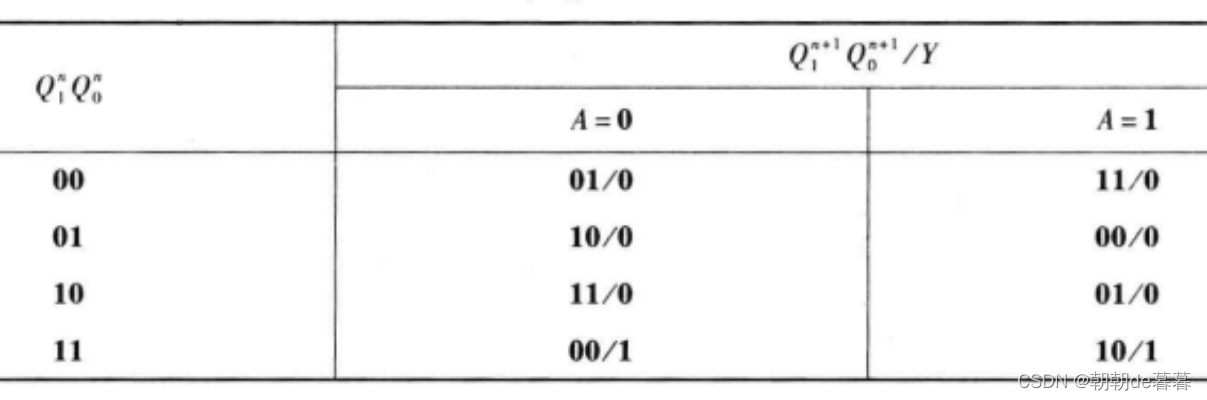

VL21 根据状态转移表实现时序电路:某同步时序电路转换表如下,请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

reg q0, q1;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

q0 <= 1'b0;

q1 <= 1'b0;

end

else begin

q1 <= A^q1^q0;

q0 <= ~q0;

end

end

assign Y = q1&q0;//拆分三个真值表

VL22 根据状态转移图实现时序电路:

某同步时序电路的状态转换图如下,→上表示“C/Y”,圆圈内为现态,→指向次态。

请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

parameter state0 = 2'b00, state1 = 2'b01, state2 = 2'b10, state3 = 2'b11;

reg y;

reg [1:0] curr_state, next_state;

always @(*)begin

case(curr_state)

state0: begin

y <= 1'b0;

next_state <= C?state1:state0;

end

state1: begin

y <= 1'b0;

next_state <= C?state1:state3;

end

state2: begin

y <= C?1'b1:1'b0;

next_state <= C?state2:state0;

end

state3: begin

y <= 1'b1;

next_state <= C?state2:state3;

end

endcase

end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

curr_state <= state0;

next_state <= state0;

end

else

curr_state <= next_state;

end

assign Y = y;

VL23 ROM的简单实现:实现一个深度为8,位宽为4bit的ROM,数据初始化为0,2,4,6,8,10,12,14。可以通过输入地址addr,输出相应的数据data。

reg [3:0] data0;

always @(*)begin

if(!rst_n)

data0 <= 4'b0;

else begin

case(addr)

8'b0000_0000: data0 <= 4'd0;

8'b0000_0001: data0 <= 4'd2;

8'b0000_0010: data0 <= 4'd4;

8'b0000_0011: data0 <= 4'd6;

8'b0000_0100: data0 <= 4'd8;

8'b0000_0101: data0 <= 4'd10;

8'b0000_0110: data0 <= 4'd12;

8'b0000_0111: data0 <= 4'd14;

default: data0 <= 4'b0;

endcase

end

end

assign data = data0;//错误,存储类型声明错误!!

reg [3:0] rom_data [7:0];//存储器宽度为4bit深度为8

always @(posedge clk or negedge rst_n)begin

if(!rst_n) begin

rom_data[0] <= 4'd0;

rom_data[1] <= 4'd2;

rom_data[2] <= 4'd4;

rom_data[3] <= 4'd6;

rom_data[4] <= 4'd8;

rom_data[5] <= 4'd10;

rom_data[6] <= 4'd12;

rom_data[7] <= 4'd14;

end

else begin

rom_data[0] <= 4'd0;

rom_data[1] <= 4'd2;

rom_data[2] <= 4'd4;

rom_data[3] <= 4'd6;

rom_data[4] <= 4'd8;

rom_data[5] <= 4'd10;

rom_data[6] <= 4'd12;

rom_data[7] <= 4'd14;

end

end

assign data = rom_data[addr];

VL24 边沿检测:有一个缓慢变化的1bit信号a,编写一个程序检测a信号的上升沿给出指示信号rise,当a信号出现下降沿时给出指示信号down。

reg q0, q1;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

q0 <= 1'b0;

q1 <= 1'b0;

end

else begin

q0 <= a;

q1 <= q0;

end

endalways @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rise <= 1'b0;

down <= 1'b0;

end

else begin

rise <= q0&~q1;

down <= ~q0&q1;

end

end//无法处理X和Z值

reg q0;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

q0 <= 1'b0;

end

else begin

q0 <= a;

end

end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rise <= 1'b0;

down <= 1'b0;

end

else begin

rise <= ((a&~q0)===1)?1:0;//===相较于==可以识别X和Z

down <= ((~a&q0)===1)?1:0;

end

end

本文介绍了如何使用Verilog语言通过D触发器和逻辑门实现同步时序电路的转换表,并结合状态转换图实例。还展示了深度为8的ROM设计,包括边沿检测和数据寻址。涵盖了同步电路、状态机、触发器和内存设计的关键知识点。

本文介绍了如何使用Verilog语言通过D触发器和逻辑门实现同步时序电路的转换表,并结合状态转换图实例。还展示了深度为8的ROM设计,包括边沿检测和数据寻址。涵盖了同步电路、状态机、触发器和内存设计的关键知识点。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?