参考 原文链接:https://blog.youkuaiyun.com/weixin_45735391/article/details/127178704

T指{取指、间址、执行、中断}

中断周期CPU完成操作——保存断点、将中断向量送PC、关中断

系统并行性——在同一时刻或同一时间段内完成两个或两个以上性质相同或性质不同的功能,只要时间上存在相互重叠,就存在并行性

| 同时性 | 2或以上事件同一时刻发生 |

| 并发性 | 2或多个事件同一时间段发生 |

粗粒度并行和细粒度并行区别

| 粗 | 多个处理机上分别运行多个进程,由多台处理机合作完成一个程序,一般用算法(软件)实现 |

| 细 | 在处理机的指令级和操作级的并行性,硬件 |

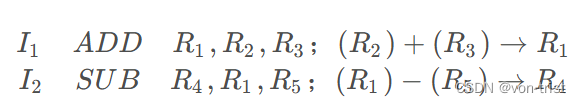

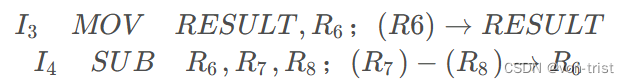

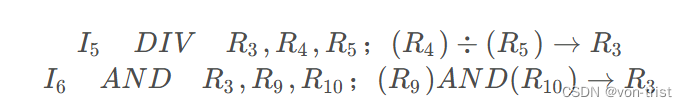

举例说明流水线几种数据相关

|

写后读相关(RAW) |

指令运算结果应先写入R1 ,然后在I2指令中读出R2

|

| 读后写 |

I3指令应先读出R6内容并存入存储器,I4指令中将运算结果写入R6

|

| 写后写 |

I6指令的与运算结果早于I5 指令的除法结果,变成I6指令在I5

|

在5个功能段的指令流水线中,设每个功能段执行时间分别是10ns、8ns、10ns、10ns和7ns,对于完成12条指令的流水线而言,加速比=?该流水线实际吞吐率——指单位时间内完成的指令数量=?

为让每个功能段都完成,取流水线各段时间——T时至少==10ns

不采用流水线=12×(10+8+10+10+7)=540ns

采用流水线=(12-1)×10+5×10=160ns

加速比=540/160

实际吞吐率=

中断系统中INTR、INT、EINT触发器作用

INTR——中断请求,每个中断源都对应一个 INTR,当其为“1”状态时,表示该中断源有请求

EINT——中断允许,CPU中的中断总开关。EINT=1,允许中断(开中断),EINT=0,禁止中断(关中断)。其状态可由开、关中断等指令设置。

INT——中断标记,INT=1时,进入中断周期,执行中断隐指令操作

中断隐指令——CPU响应中断之后,经过某些操作,转去执行中断服务程序,这些操作是由硬件直接实现的——指令系统中没有的指令由CPU在中断响应周期自动完成

中断隐指令功能?

(1)保存断点

(2) 暂不允许中断

(3) 引出中断服务程序

中断系统采用屏蔽技术作用——多重中断,可以改变优先等级,保证级别低的中断源不干扰级别高的中断处理过程,给程序控制带来更大灵活性

中断处理过程进行中断判优why——CPU 在某一时刻只能响应一个中断解决相响应的优先次序

多个中断源同时请求按优先级次序予以响应,两种实现方法:

(1)硬件实现(排队器): 组合逻辑电路实现

(2)软件实现(程序查询):程序按优先级别(从高到低)顺序查询各中断源。软件查询次序决定了优先级高低

改变原定的优先顺序措施——屏蔽技术

某机有五个中断源L0、L1、L2、 L3、L4,按中断响应的优先次序由高向低排序为L0->L1->L2->L3->L4,中断处理次序改为L1->L4->L2->L0->L3,写出各中断源屏蔽字

|

中断源 |

屏蔽字 | ||||

|

0 |

1 |

2 |

3 |

4 | |

|

I0 |

1 |

0 |

0 |

1 |

0 |

|

I1 |

1 |

1 |

1 |

1 |

1 |

|

I2 |

1 |

0 |

1 |

1 |

0 |

|

I3 |

0 |

0 |

0 |

1 |

0 |

|

I4 |

1 |

0 |

1 |

1 |

1 |

屏蔽位=1,屏蔽;屏蔽位=0,中断开放

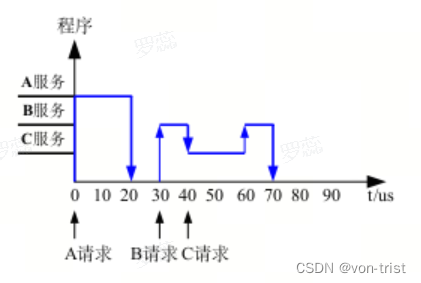

设某机配有A、B、C三台设备,其优先顺序按A->B->C降序排列,为改变中断处理次序,它们的中断屏蔽字设置如下:

|

设备 |

屏蔽字 |

|

A |

111 |

|

B |

010 |

|

C |

011 |

按下图所示时间轴给出的设备请求中断的时刻,画出CPU执行程序的轨迹

设A、B、C中断服务程序执行时间均=20µs

响应优先级为A->B->C,处理优先级为A->C->B

计算机组成原理精要

计算机组成原理精要

1189

1189

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?