一、NPC设计的基本思路

- 目前使用verilog编写npc,它的底层描述更为清晰,细节掌握更为具体。

- 采用模块化的设计,方便将来设计流水线,将指令存储器与数据存储器分开(但是在pmem中它们同属于一个数组中,Am采用linker.ld脚本将数据与指令的位置隔离开,这样我们在设计时就不需要考虑冲突的问题)。

- 对于控制信号的设计,采用了CPU设计实战对于loongarch指令译码出控制信号的设计思路(避免了case语句代码的重复性以及采用真值表设计的复杂性)。

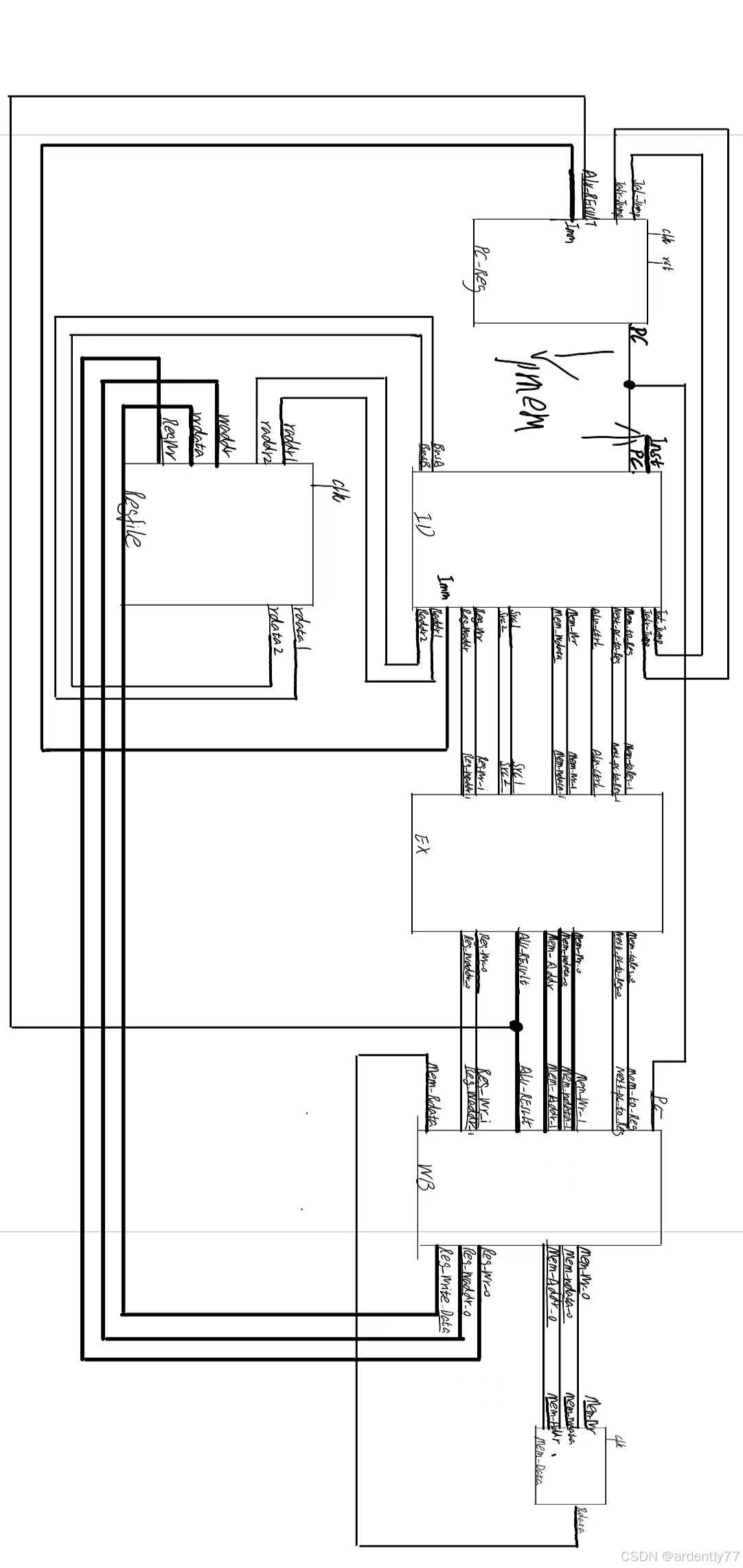

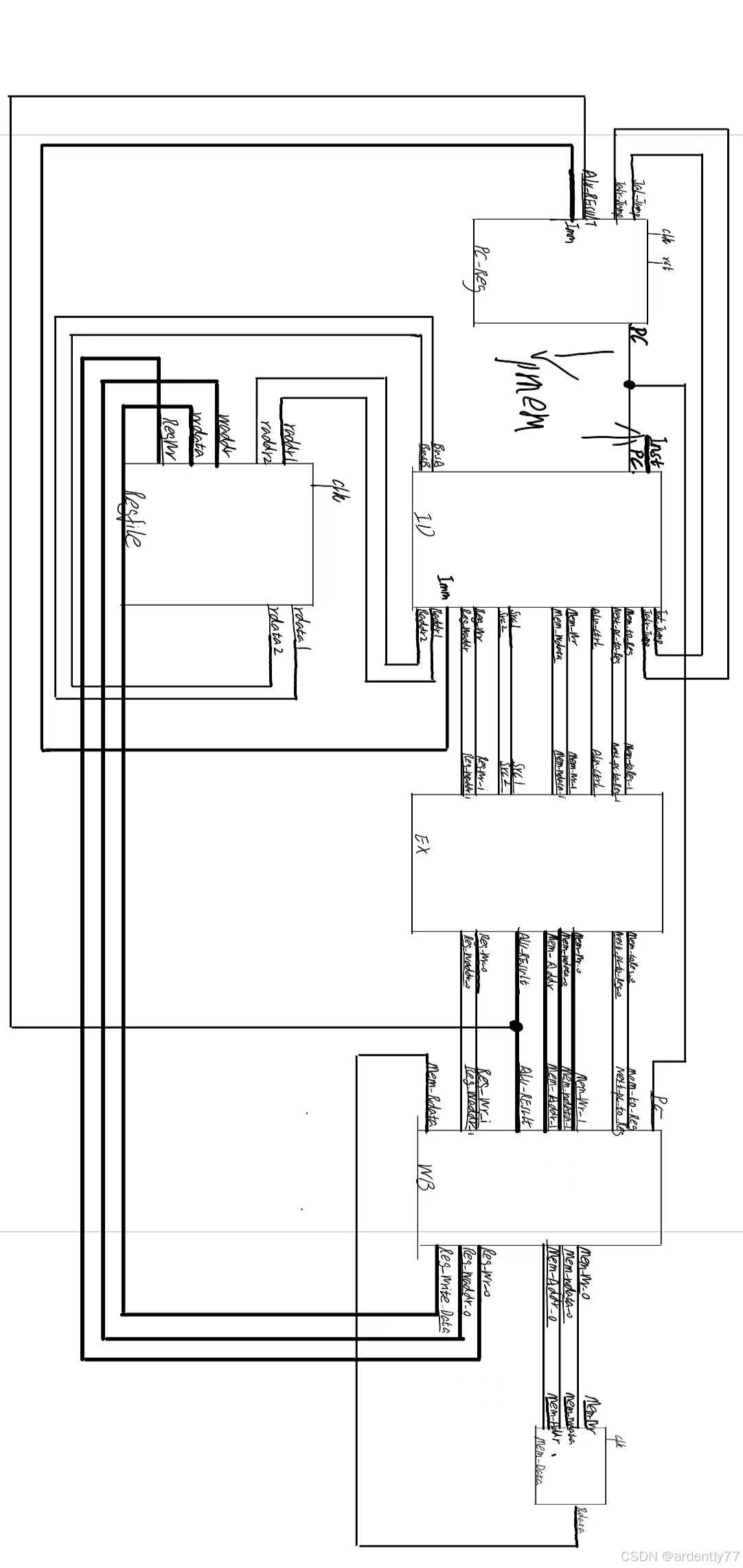

电路图如下:

控制信号译码模块代码:

`include "Define.v"

module ID(

input wire [`DataBus-1:0] Inst,

input wire [`DataBus-1:0] Pc,

output wire [`RegAddr-1:0] Raddr1,

input wire [`DataBus-1:0] BusA,

output wire [`RegAddr-1:0] Raddr2,

input wire [`DataBus-1:0] BusB,

output wire [`DataBus-1:0] Src1,

output wire [`DataBus-1:0] Src2,

output wire Reg_Wr,

output wire [`RegAddr-1:0] Reg_Waddr,

output wire Mem_Wr,

output wire [`MemAddr-1:0] Mem_Wdata,

output wire [`Ctrl_Alu_Ctrl-1:0] Alu_Ctrl,

output wire Mem_To_Reg,

output wire Next_Pc_To_Reg,

output wire Jal_Jump,

output wire Jalr_Jump,

output wire [`DataBus-1:0] Imm

);

wire Alu_Asrc_Is_Pc;

wire Alu_Bsrc_Is_Imm;

wire Alu_Bsrc_Is_4;

wire [`OpBus-1:0] op;

wire [`Funct3-1:0] funct3;

wire [`Funct7-1:0] funct7;

wire [`RegAddr-1:0] rs1, rs2, rd;

assign op = Inst[6:0];

assign funct3 = Inst[14:12];

assign funct7 = Inst[31:25];

assign rs1 = Inst[19:15];

assign rs2 = Inst[24:20];

assign rd = Inst[11:7];

Ctrl ctrl(

.Inst(Inst),

.op(op),

.funct3(funct3),

.funct7(funct7),

.Alu_Asrc_Is_Pc(Alu_Asrc_Is_Pc),

.Alu_Bsrc_Is_Imm(Al

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2846

2846

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?