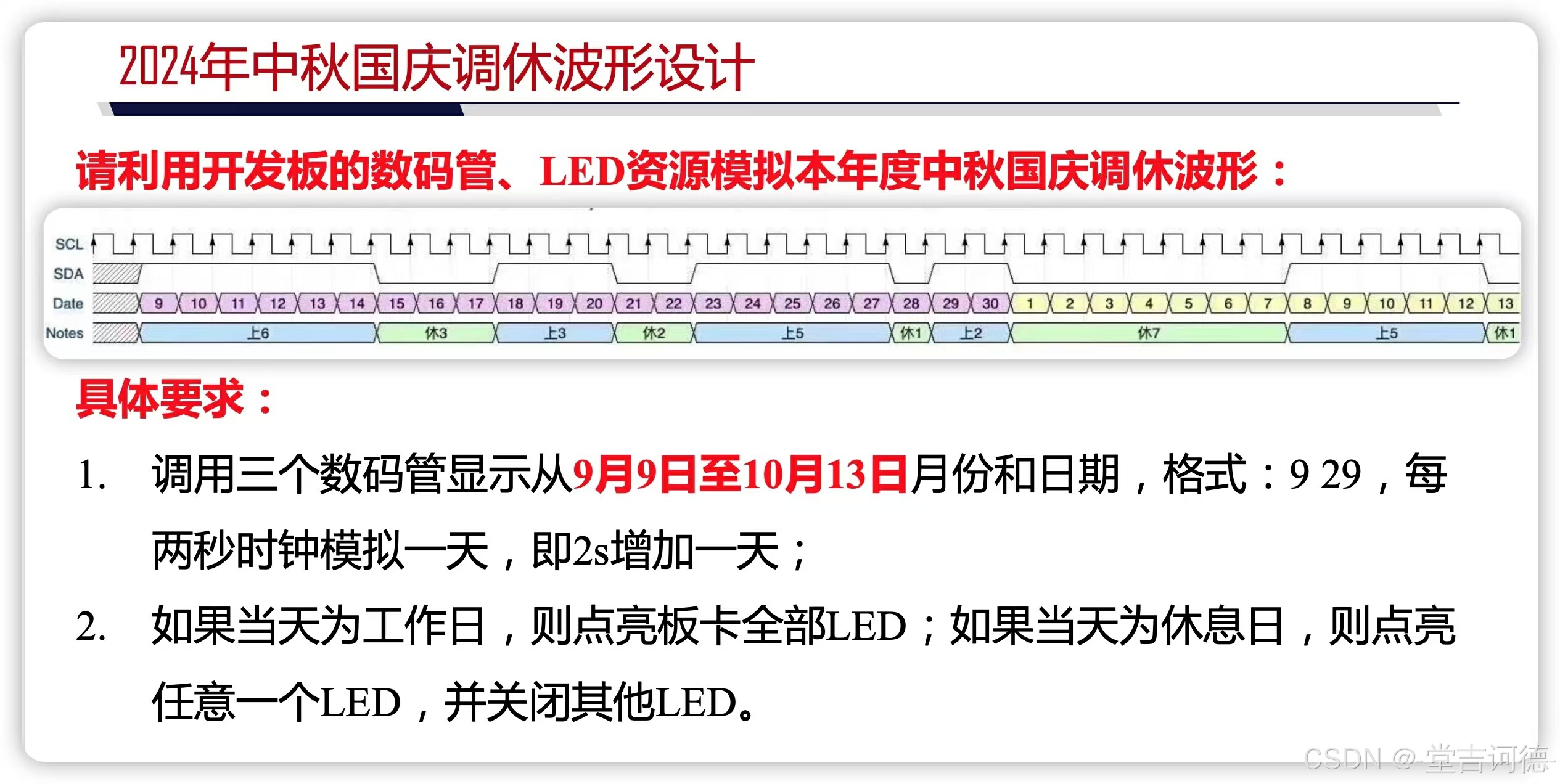

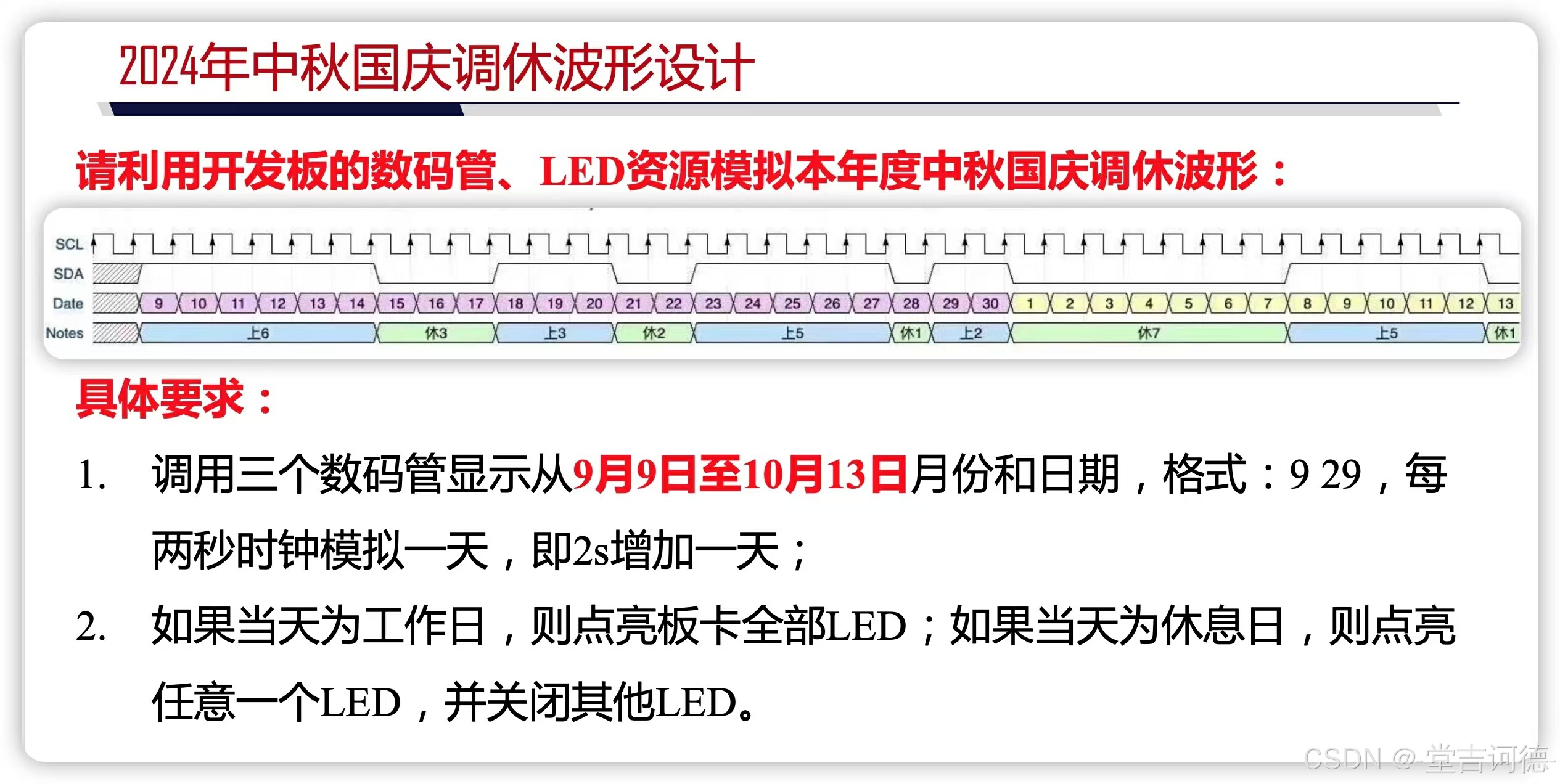

一、要求

二、Verilog代码实现

module date_display(

input rst, // 异步置位-低电平起效

input en, // 使能

input clk,

output reg [6:0] SG0, // 数码管

output reg [6:0] SG1,

output reg [6:0] SG2,

output reg [6:0] SG3,

output reg [6:0] SG4,

output reg [6:0] cnt_count,

output reg [9:0] led

);

// 日期

wire [3:0] sw1; // 十位

wire [3:0] gw1; // 个位

// 月份

wire [3:0] sw2; // 十位

wire [3:0] gw2; // 个位

wire [34:0] date; // 1为上班,0为休息

reg [5:0] index; // 修改为 reg 类型并适当调整位宽

assign date = 35'b01111100000001101111100111000111111;

assign sw1 = cnt_count % 100 / 10;

assign gw1 = cnt_count % 10;

assign sw2 = mouth / 10;

assign gw2 = mouth % 10;

reg [30:0] cnt;

reg [7:0] mouth;

reg clk1;

// 分频器

always @(posedge clk) begin

cnt <= cnt + 1;

if (cnt > 99999999) begin

clk1 <= 1'b1;

cnt <= 0;

end else

clk1 <= 1'b0;

end

// 计数

always @(negedge clk1 or negedge rst) begin

if (!rst) begin

mouth <= 7'd9;

cnt_count <= 7'd9;

index <= 0; // 初始化 index

end else if (en) begin

if (cnt_count < 7'd30) begin // 当日期小于30时,加一计数

cnt_count <= cnt_count + 7'd1;

if (index < 34) begin

index <= index + 1; // 在这里更新 index

end else begin

index <= 0;

end

if (mouth == 7'd10 && cnt_count == 7'd13) begin // 当计数到10月13日时,复位

mouth <= 7'd9;

cnt_count <= 7'd9;

index <= 0;

end

end else if (mouth == 7'd9 && cnt_count == 7'd30) begin // 当计数到9月30日时,变为10月1日

cnt_count <= 7'd1;

mouth <= 7'd10;

end

end

end

// 数码管显示

always @(posedge clk1 or negedge rst) begin

if (!rst) begin

SG0 <= 7'b0010000;

SG1 <= 7'b1000000;

SG2 <= 7'b0010000;

SG3 <= 7'b1000000;

end else begin

// 显示个十位数字

case (gw1)

0: SG0 <= 7'b1000000; 1: SG0 <= 7'b1111001;

2: SG0 <= 7'b0100100; 3: SG0 <= 7'b0110000;

4: SG0 <= 7'b0011001; 5: SG0 <= 7'b0010010;

6: SG0 <= 7'b0000010; 7: SG0 <= 7'b1111000;

8: SG0 <= 7'b0000000; 9: SG0 <= 7'b0010000;

default: SG0 <= 7'b1111111;

endcase

case (sw1)

0: SG1 <= 7'b1000000; 1: SG1 <= 7'b1111001;

2: SG1 <= 7'b0100100; 3: SG1 <= 7'b0110000;

default: SG1 <= 7'b1111111; // 添加 default 情况以防止未定义行为

endcase

case (gw2)

0: SG2 <= 7'b1000000; 9: SG2 <= 7'b0010000;

default: SG2 <= 7'b1111111;

endcase

case (sw2)

0: SG3 <= 7'b1000000; 1: SG3 <= 7'b1111001;

default: SG3 <= 7'b1111111;

endcase

SG4 <= 7'b1111111;

end

end

// 日期判定

always @(*) begin

led = date[index] ? 10'b1111111111 : 10'b0000000001; // 使用 index 进行日期判定

end

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?