记录时钟分频器的Verilog代码编写,主要掌握分频器设计思路

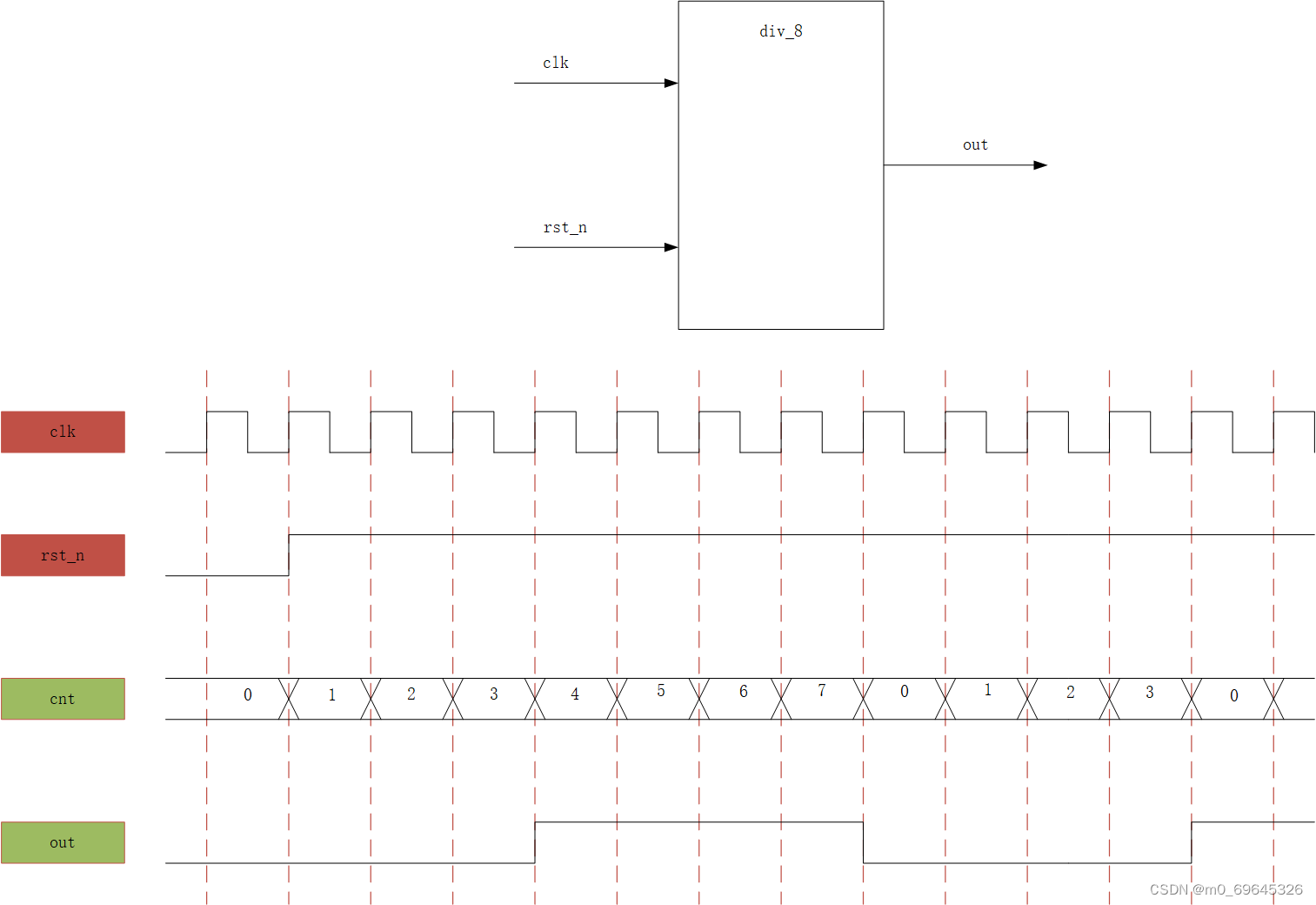

VISIO作图,计数器cnt从0计数到7,计数到7清零从新开始计数。

0-3输出为低电平,4-7输出为高电平。

时钟频率为50MHZ,周期为20ns,八分频即周期扩大八倍,周期为160ns

下面是verilog写的程序代码,包含几种不同的写法,包含组合逻辑,时序逻辑同步与异步

module div_8(

input wire clk,

input wire rst_n,

output reg out1 ,

output wire out2 ,

output reg out3 ,

output reg out4 ,

output reg out5 ,

output reg out6 ,

output reg out7 ,

output reg out8 ,

output reg out9 ,

output reg out10

);

reg[4:0] cnt;

always@(posedge clk or negedge rst_n)

begin

if(~rst_n)

cnt<=4'b0;//8fenp,

else if(cnt==4'd7)

cnt<=4'b0;

else

cnt<=cnt

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1471

1471

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?