1、基本单元

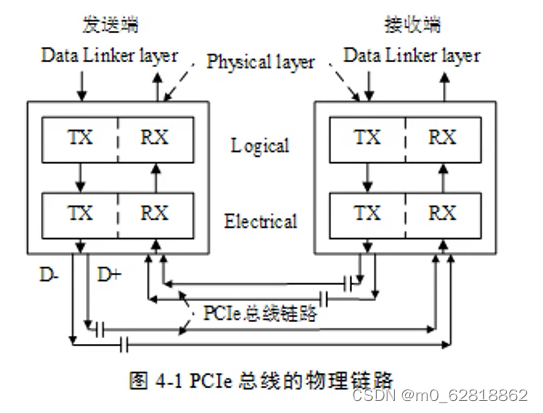

PCIE与接收设备互为发送端

最小单元最两组差分对,4根线组成,称为一个lane,常用的X1、X2、X4、X8、X16、X32

发送端接AC耦合电容(通常高速线在接收端接入AC耦合电容,PCIE为个例,一方面因为PCIE大多为板对板接口,一方面数据手册要求)

信号接收端通过判断PCIE两个信号的差值判断是0或者1

差分信号布线:等长、等宽、贴近、同层

编码方式:10的位有8位有效位,另外两个是掩码;

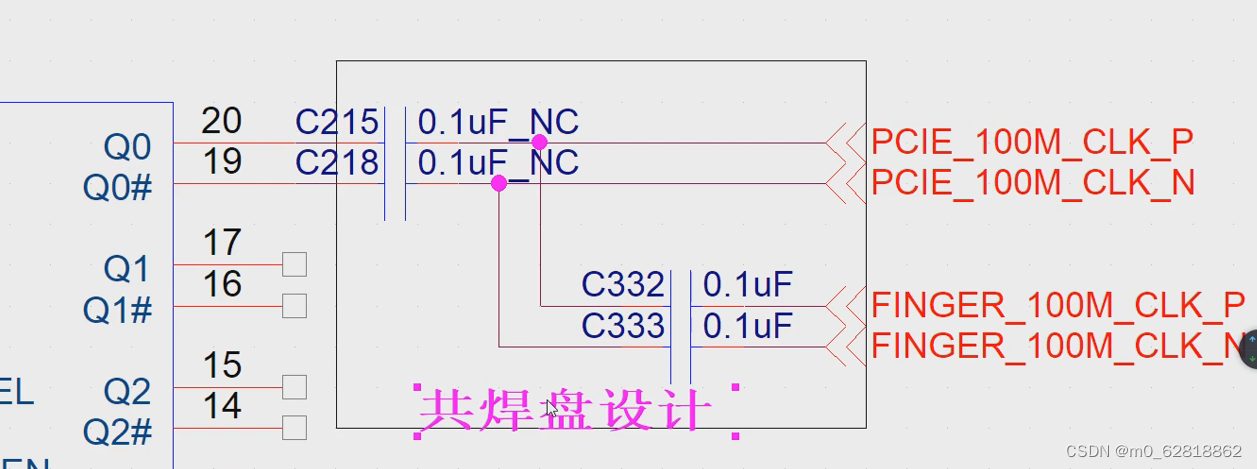

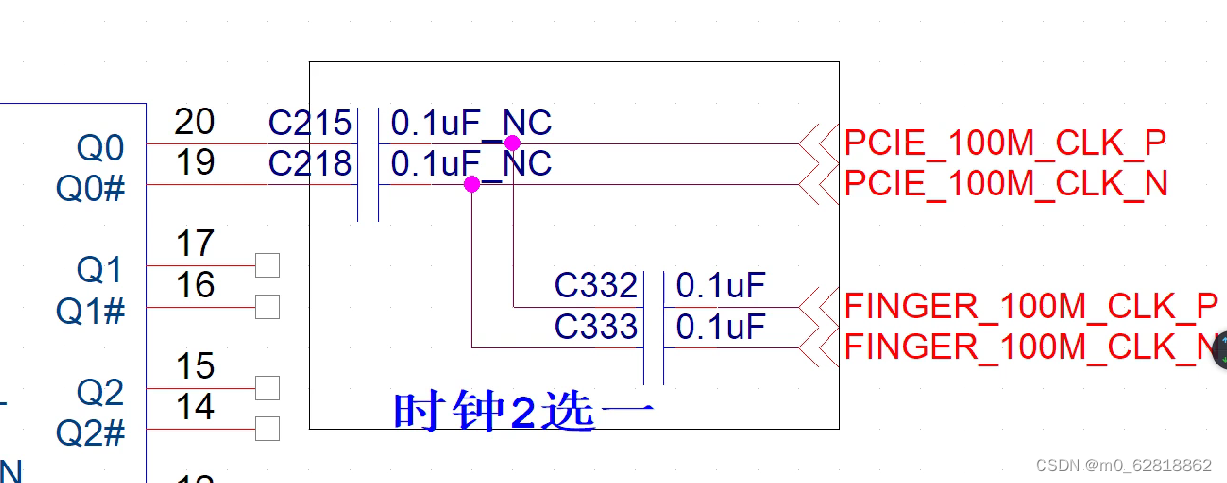

时钟:自带CDR(clock data recovery)用于同步输出信号,并行输出;同意配置100M时钟,用于和其他PCIE进行时钟同步;

热插拔:点对点连接

时钟二选一,时钟线尽可能短

本文详细介绍了PCIe(PeripheralComponentInterconnectExpress)技术中的关键要素,如lane结构、差分信号处理、AC耦合电容的应用、10位编码方式、内置CDR的时钟同步以及支持热插拔的点对点连接特点。

本文详细介绍了PCIe(PeripheralComponentInterconnectExpress)技术中的关键要素,如lane结构、差分信号处理、AC耦合电容的应用、10位编码方式、内置CDR的时钟同步以及支持热插拔的点对点连接特点。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?