top顶层文件

//`include "global_define.v"

module TOP(

inout wire [14:0] DDR_addr,

inout wire [2:0] DDR_ba,

inout wire DDR_cas_n,

inout wire DDR_ck_n,

inout wire DDR_ck_p,

inout wire DDR_cke,

inout wire DDR_cs_n,

inout wire [3:0] DDR_dm,

inout wire [31:0] DDR_dq,

inout wire [3:0] DDR_dqs_n,

inout wire [3:0] DDR_dqs_p,

inout wire DDR_odt,

inout wire DDR_ras_n,

inout wire DDR_reset_n,

inout wire DDR_we_n,

inout wire FIXED_IO_ddr_vrn,

inout wire FIXED_IO_ddr_vrp,

inout wire [53:0] FIXED_IO_mio,

inout wire FIXED_IO_ps_clk,

inout wire FIXED_IO_ps_porb,

inout wire FIXED_IO_ps_srstb,

//misc

//input wire key,

output wire led1,

output wire led2,

output wire led3,

input wire uart_rx,

output wire uart_tx

);

// assign led1 = ~vout_lvds_mmcm_locked;

// assign led2 = ~led_b;

wire clk_axi;

design_1 u_bd(

.DDR_addr (DDR_addr ),

.DDR_ba (DDR_ba ),

.DDR_cas_n (DDR_cas_n ),

.DDR_ck_n (DDR_ck_n ),

.DDR_ck_p (DDR_ck_p ),

.DDR_cke (DDR_cke ),

.DDR_cs_n (DDR_cs_n ),

.DDR_dm (DDR_dm ),

.DDR_dq (DDR_dq ),

.DDR_dqs_n (DDR_dqs_n ),

.DDR_dqs_p (DDR_dqs_p ),

.DDR_odt (DDR_odt ),

.DDR_ras_n (DDR_ras_n ),

.DDR_reset_n (DDR_reset_n ),

.DDR_we_n (DDR_we_n ),

.FIXED_IO_ddr_vrn (FIXED_IO_ddr_vrn ),

.FIXED_IO_ddr_vrp (FIXED_IO_ddr_vrp ),

.FIXED_IO_mio (FIXED_IO_mio ),

.FIXED_IO_ps_clk (FIXED_IO_ps_clk ),

.FIXED_IO_ps_porb (FIXED_IO_ps_porb ),

.FIXED_IO_ps_srstb (FIXED_IO_ps_srstb ),

.UART_rxd (uart_rx ),

.UART_txd (uart_tx ),

.clk_axi (clk_axi ),

.rstn_axi ( )

);

//--------------------------------led----------------------------------

//led 顶层文件例化

led led_breath(

.clk (clk_axi ),

.led (led_b )

);

assign led1 = led_b;

assign led2 = led_b;

assign led3 = led_b;

endmodule

led呼吸灯闪烁程序:

注意:vivado版本问题,注释存在乱码,但不影响编译。我用的是2018.3

module led(

input wire clk, // 杈撳叆鏃堕挓

output reg led // led 杈撳嚭(楂樼數骞虫湁鏁�)

);

localparam MAX_DELAY_CNT = 100000,

CYCLE_NUMBER = 100; //鍗犵┖姣斿垎涓�0~100涓骇鍒�

reg myclk;

reg [23:0] delay_cnt;

reg [7:0] current_cycle;

reg flag;

reg [7:0] cycle;

//--------------------------------------------------------

// myclk鍒嗛

always@(posedge clk) begin

if(delay_cnt < MAX_DELAY_CNT)

delay_cnt <= delay_cnt + 1'b1;

else begin

delay_cnt <= 24'd1;

myclk <= ~myclk;

end

end

//--------------------------------------------------------

// 0鐨勬椂鍊欙紝鍗犵┖姣旀渶灏忥紝杩欎釜鏃跺�欑洿鎺ュ畬鍏ㄨ緭鍑洪珮鐢靛钩锛宭ed鐏渶浜�

// 100鐨勬椂鍊欙紝鍗犵┖姣旀渶澶э紝杩欎釜鏃跺�欑洿鎺ュ畬鍏ㄨ緭鍑轰綆鐢靛钩锛宭ed绛夌唲鐏�

always@(posedge myclk) begin

if(flag == 0) begin // 鍗犵┖姣旈�掑

if(current_cycle < CYCLE_NUMBER)

current_cycle <= current_cycle + 1'b1;

else

flag <= ~flag;

end

else begin // 鍗犵┖姣旈�掑噺

if(current_cycle > 0)

current_cycle <= current_cycle - 1'b1;

else

flag <= ~flag;

end

end

//--------------------------------------------------------

// 杞 0~100涓骇鍒殑鍗犵┖姣�

always@(posedge clk)

if(cycle < CYCLE_NUMBER)

cycle <= cycle + 1'b1;

else

cycle <= 1'b1;

//--------------------------------------------------------

// cycle灏忎簬current_cycle鐨勬椂鍊欐槸浣庣數骞�

// cycle澶т簬current_cycle骞朵笖灏忎簬CYCLE_NUMBER鐨勬椂鍊欐槸楂樼數骞�

always@(posedge clk)

if((cycle == CYCLE_NUMBER) && (current_cycle != 0))

led <= 1'b0;

else if(cycle < current_cycle)

led <= 1'b0;

else

led <= 1'b1;

endmodule

xdc文件:

#pin 引脚约束:

#KEY

set_property PACKAGE_PIN G14 [get_ports key]

set_property IOSTANDARD LVCMOS33 [get_ports key]

#LED

set_property PACKAGE_PIN H15 [get_ports led1]

set_property IOSTANDARD LVCMOS33 [get_ports led1]

set_property PACKAGE_PIN G15 [get_ports led2]

set_property IOSTANDARD LVCMOS33 [get_ports led2]

set_property PACKAGE_PIN N15 [get_ports led3]

set_property IOSTANDARD LVCMOS33 [get_ports led3]

#UART

set_property PACKAGE_PIN N20 [get_ports uart_tx]

set_property IOSTANDARD LVCMOS33 [get_ports uart_tx]

set_property PACKAGE_PIN U20 [get_ports uart_rx]

set_property IOSTANDARD LVCMOS33 [get_ports uart_rx]

#EEPROM

set_property PACKAGE_PIN P16 [get_ports eeprom_scl]

set_property IOSTANDARD LVCMOS33 [get_ports eeprom_scl]

set_property PACKAGE_PIN P15 [get_ports eeprom_sda]

set_property IOSTANDARD LVCMOS33 [get_ports eeprom_sda]

#GPIO

set_property PACKAGE_PIN K19 [get_ports gpio1]

set_property IOSTANDARD LVCMOS33 [get_ports gpio1]

set_property PACKAGE_PIN F20 [get_ports gpio2]

set_property IOSTANDARD LVCMOS33 [get_ports gpio2]

set_property PACKAGE_PIN J18 [get_ports gpio3]

set_property IOSTANDARD LVCMOS33 [get_ports gpio3]

set_property PACKAGE_PIN L20 [get_ports gpio4]

set_property IOSTANDARD LVCMOS33 [get_ports gpio4]

set_property PACKAGE_PIN L17 [get_ports gpio5]

set_property IOSTANDARD LVCMOS33 [get_ports gpio5]

set_property PACKAGE_PIN M17 [get_ports gpio6]

set_property IOSTANDARD LVCMOS33 [get_ports gpio6]

set_property PACKAGE_PIN K18 [get_ports gpio7]

set_property IOSTANDARD LVCMOS33 [get_ports gpio7]

set_property PACKAGE_PIN L16 [get_ports gpio8]

set_property IOSTANDARD LVCMOS33 [get_ports gpio8]

#set_property BITSTREAM.CONFIG.UNUSEDPIN Pullup [current_design]

#timing:

#不需要分别创建两个xdc文件

set_property BITSTREAM.GENERAL.COMPRESS true [current_design]

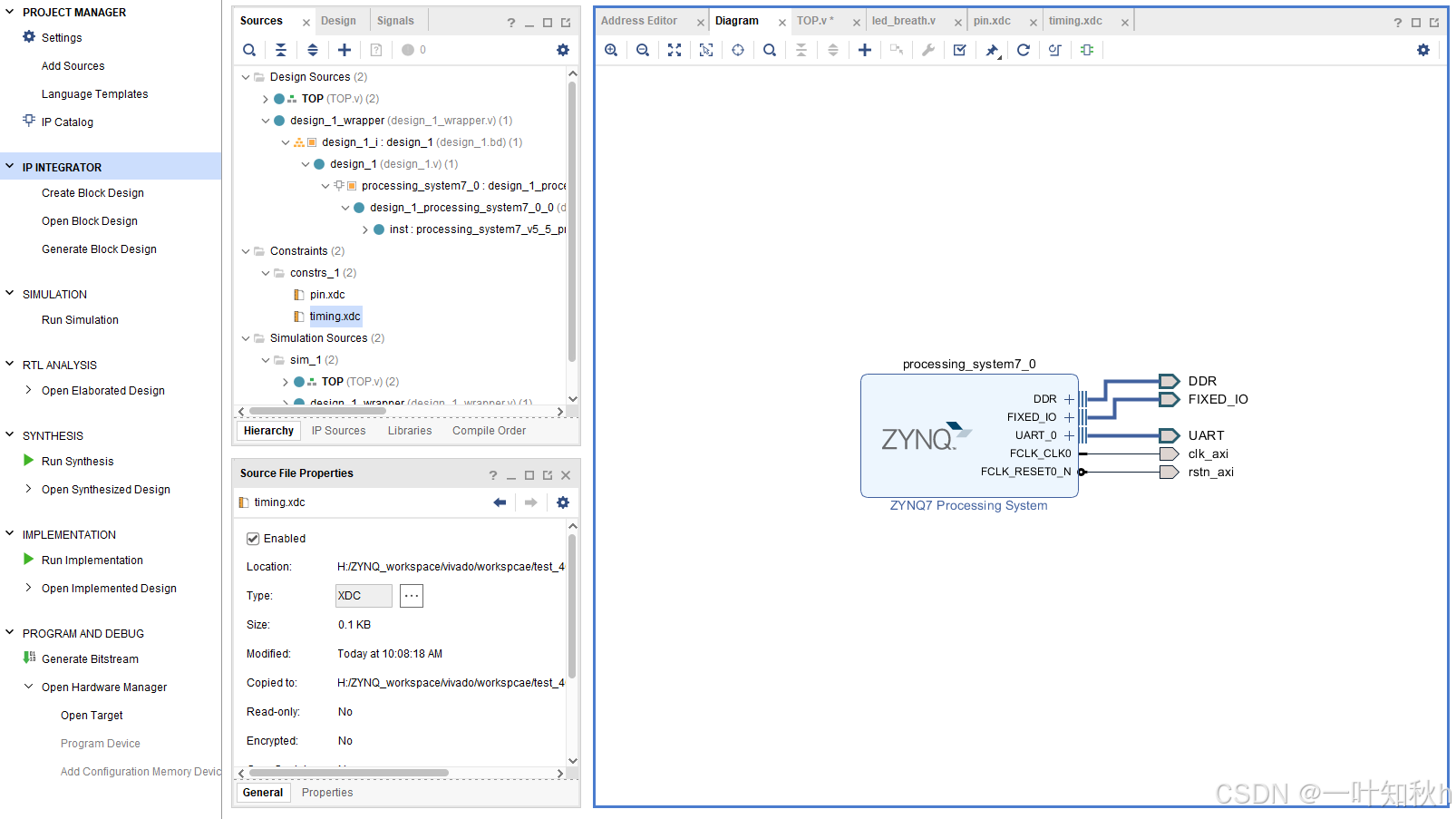

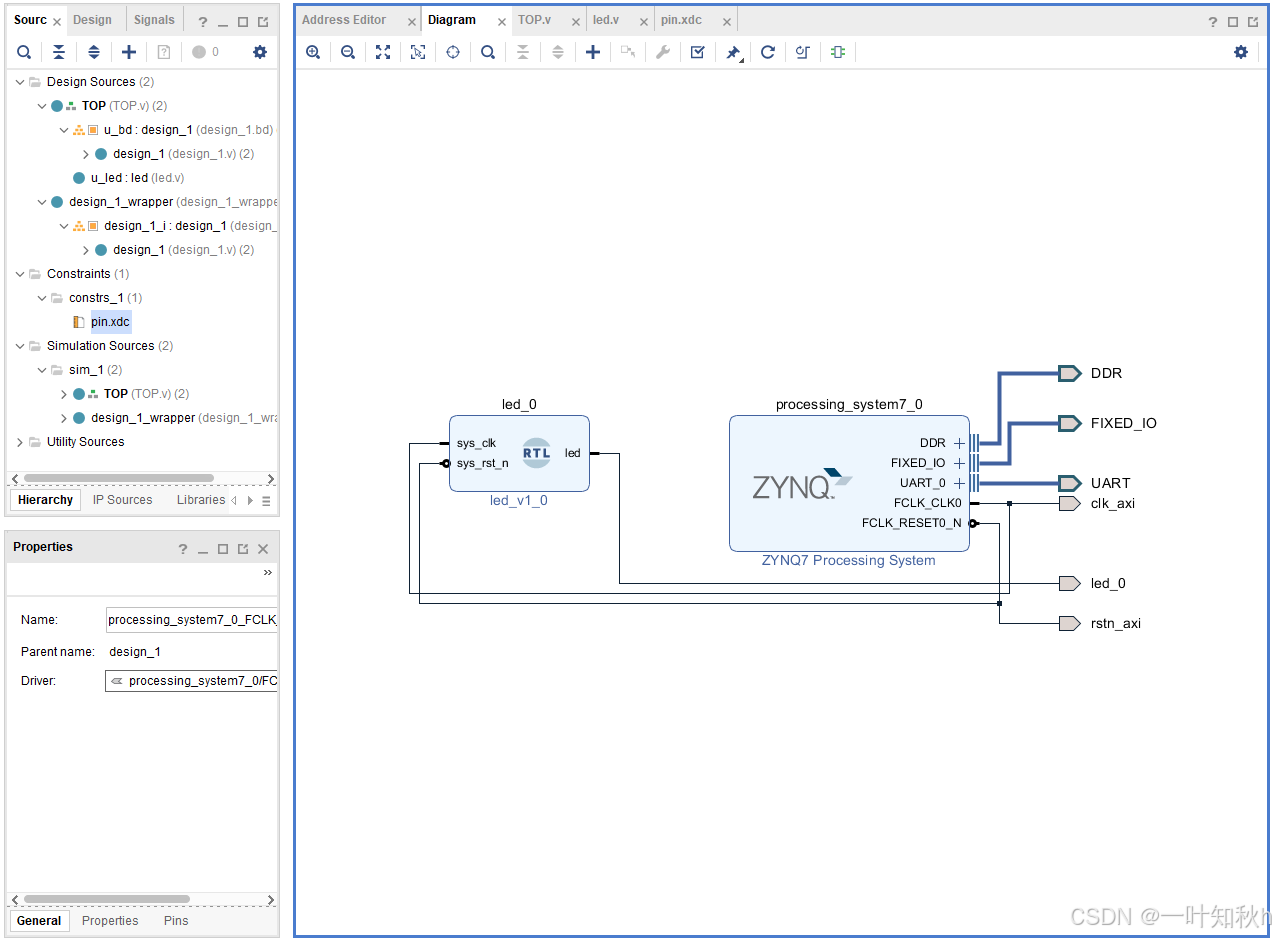

block_design:

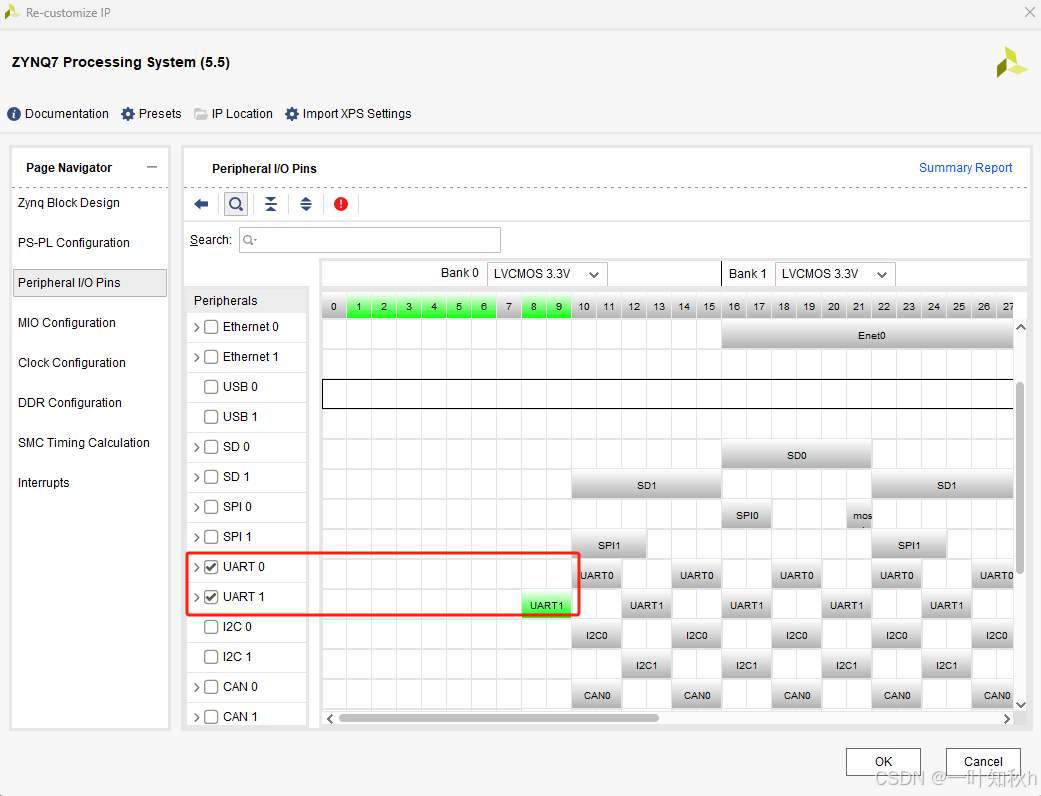

另外还需要注意在创建Block Design时, 选择IOPin的过程,如果想zynqPS块出现对应的uart、IIC等引脚,需要做如下选择(以uart为例)当然还需要确保引脚不冲突:

注意arm端(sdk)的调用,不然没有时钟,这里可以参考以下连接:

ZYNQ初识2(zynq_7010)基于vivado,从PL端调用PS端的时钟_fpga ps pl时钟-优快云博客

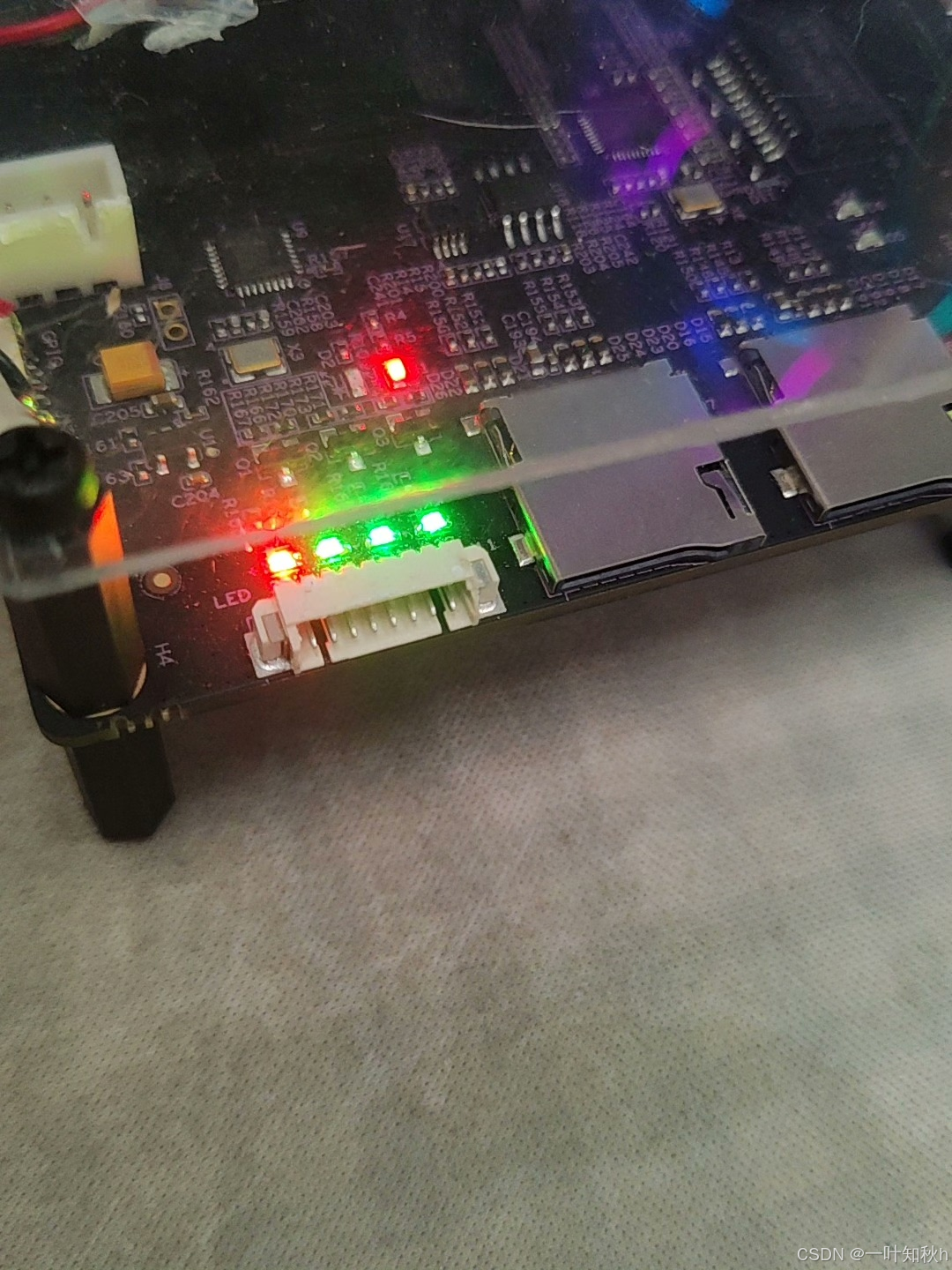

效果图:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?