目录

一、硬件部分设计

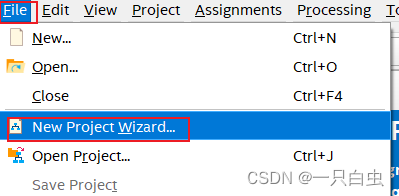

1、创建新项目

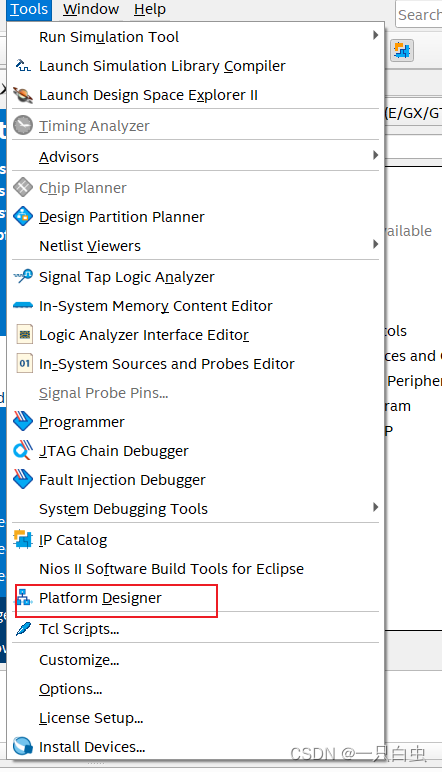

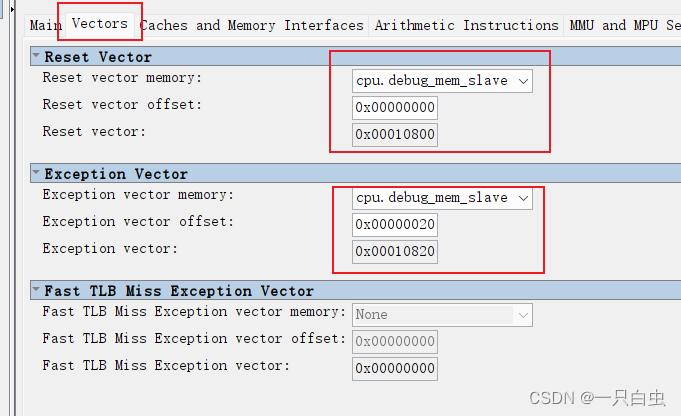

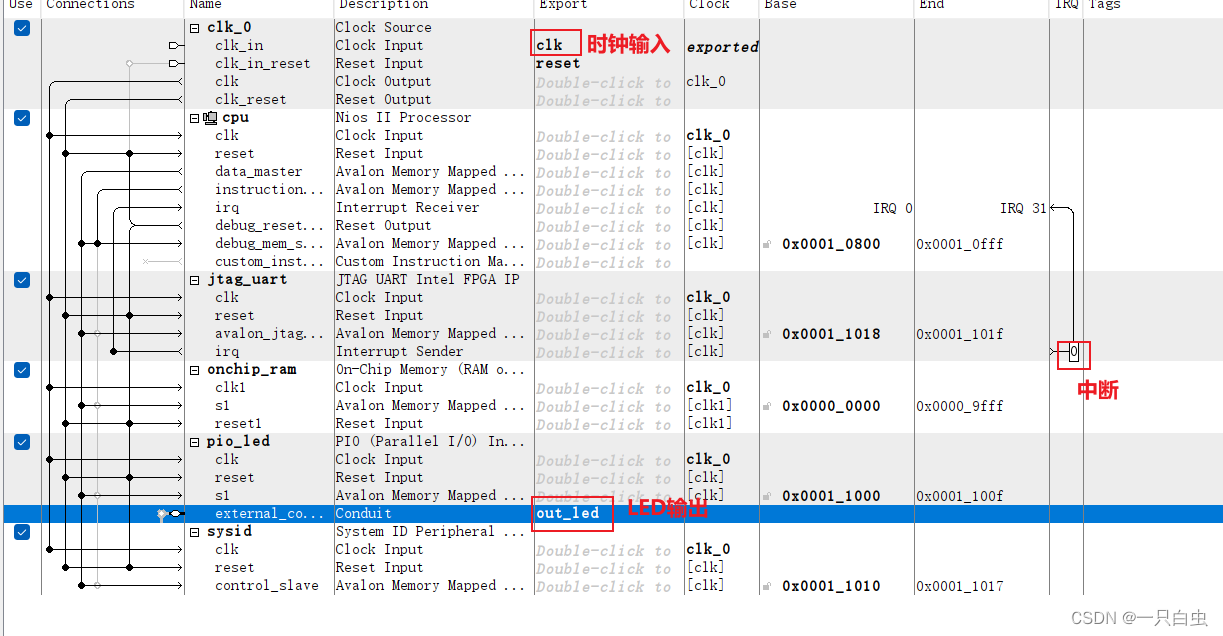

2、进行Qsys系统设计

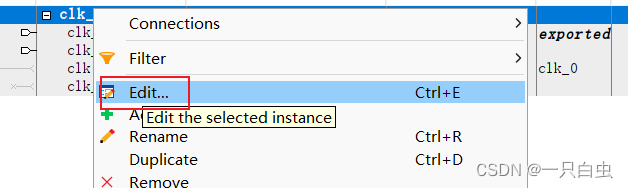

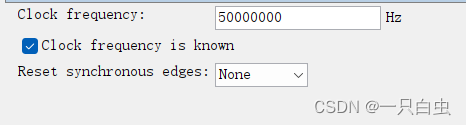

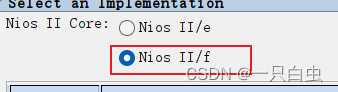

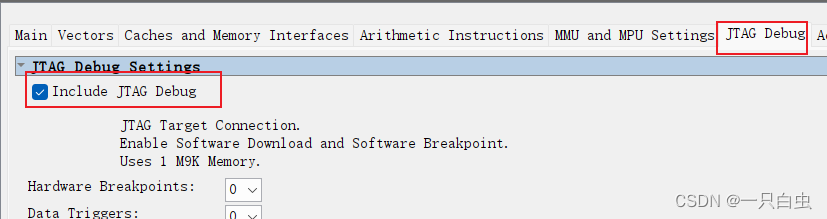

添加 Nios II 32-bit CPU

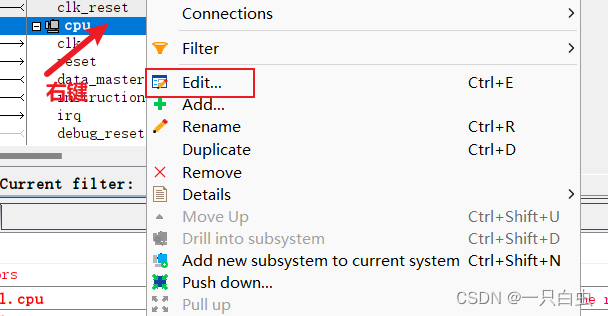

将 nios2_qsys_0 重命名为 cpu,点击”Rename”即可重新命名

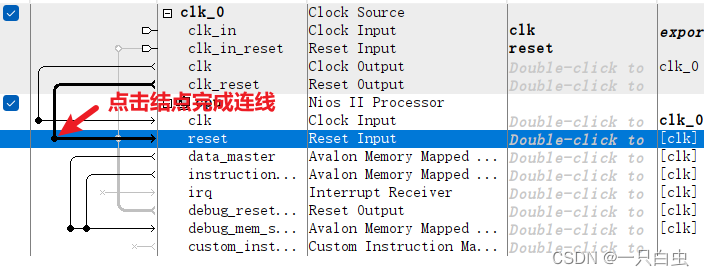

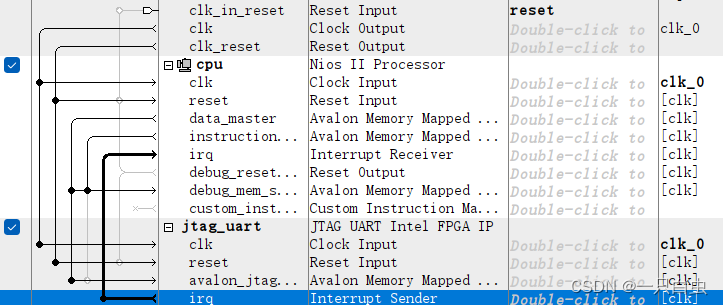

将 cpu 的 clk 和 reste_n 分别与系统时钟 clk_0 的 clk 和 clk_reset 相连

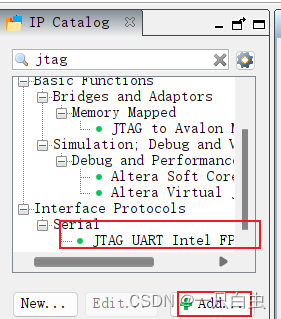

添加 jtag uart 接口。

在 JTAG UART-jtag-uart_0 的设置向导中保持默认选项,点击 Finish,将 jtag-uart_0 重命名为 jtag-uart。

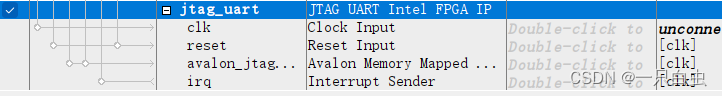

进行 clk、reset 以及 master-slave 的连线,进行中断 irq 连线

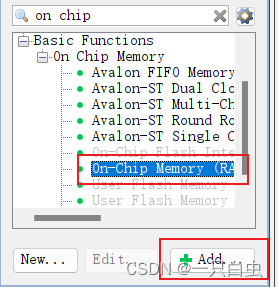

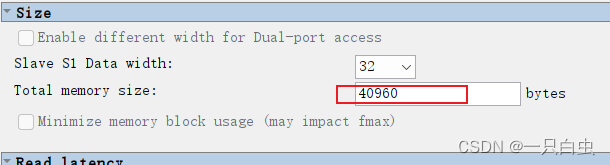

添加片上存储器 On-Chip Memory(RAM)核

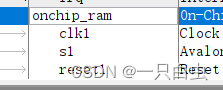

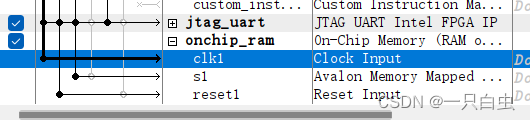

将 onchip_memory2_0 改名为 onchip_ram

进行时钟、数据端口、指令端口的连接

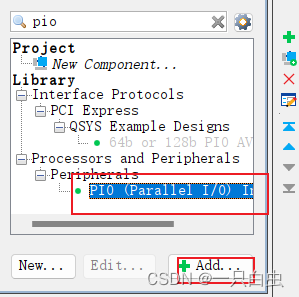

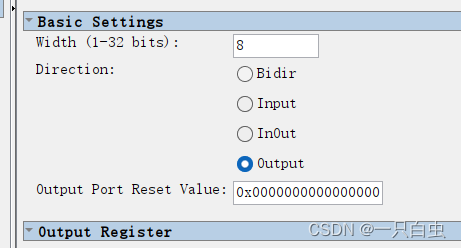

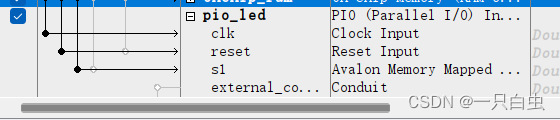

添加 PIO 接口

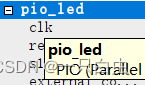

将pio_0 改名为 pio_led

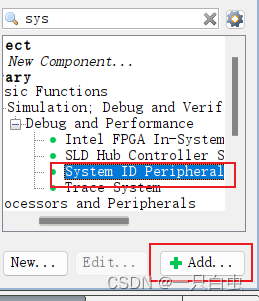

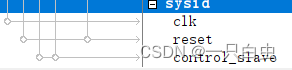

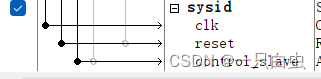

添加片 System ID Peripheral 核

进行时钟、数据端口的连接

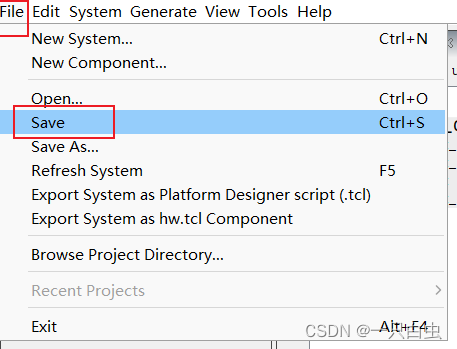

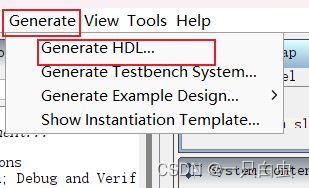

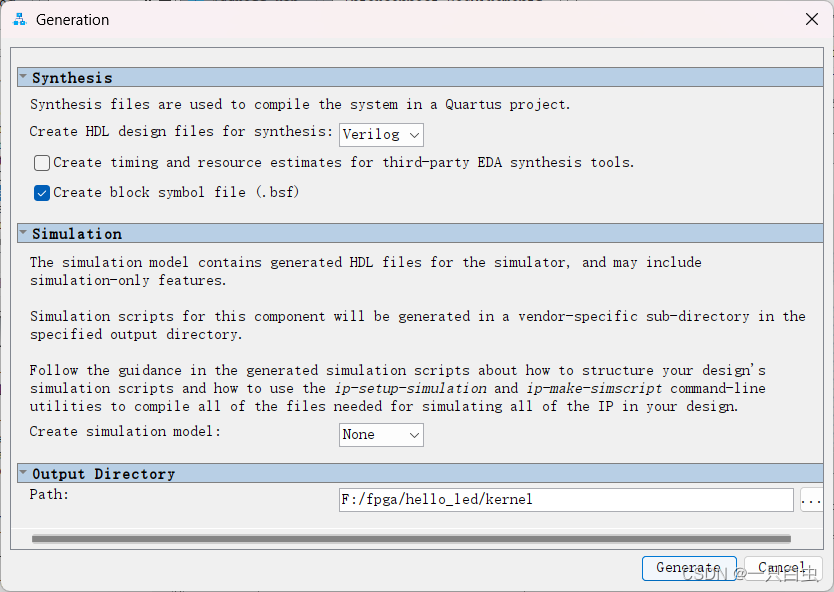

3、完成 Qsys 设计的后续工作

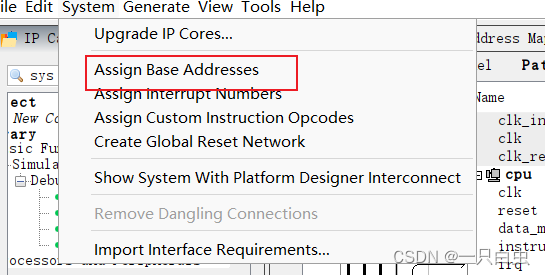

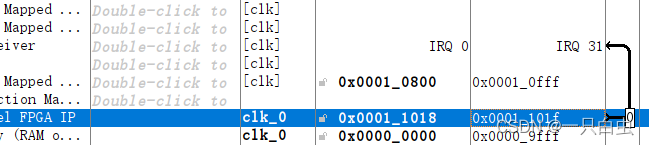

基地址分配(完成后”Base”栏将出现不会重复的具体的地址)

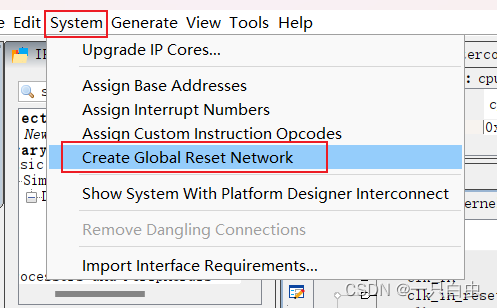

分配中断号

最终完成的连接图

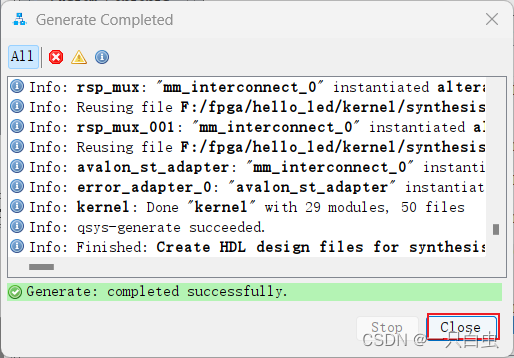

点击Close 后关闭窗口后,再关闭Platform Designer主界面

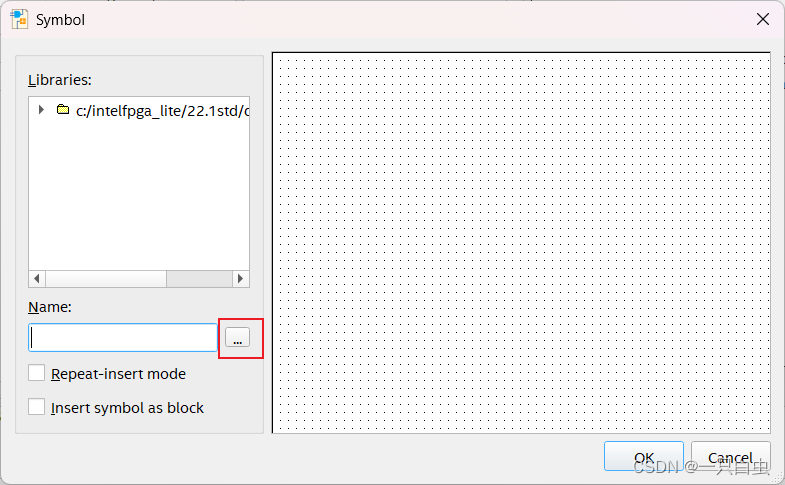

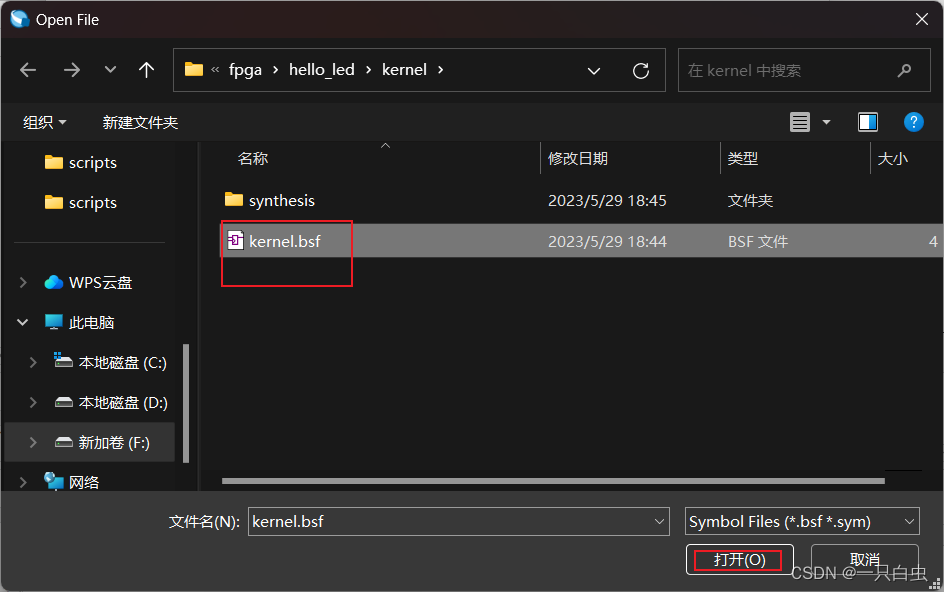

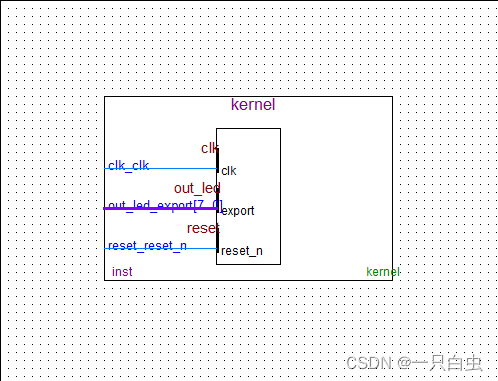

在原理图(BDF)文件中添加PD生成的系统符号

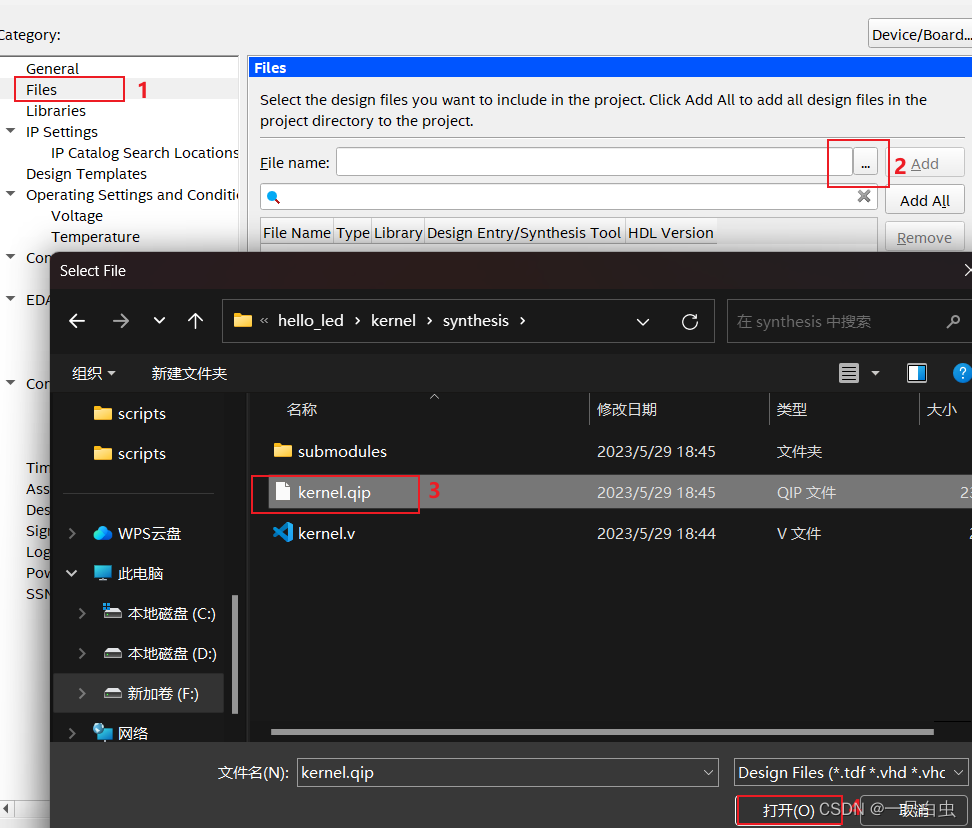

加入Quartus II IP File 文件

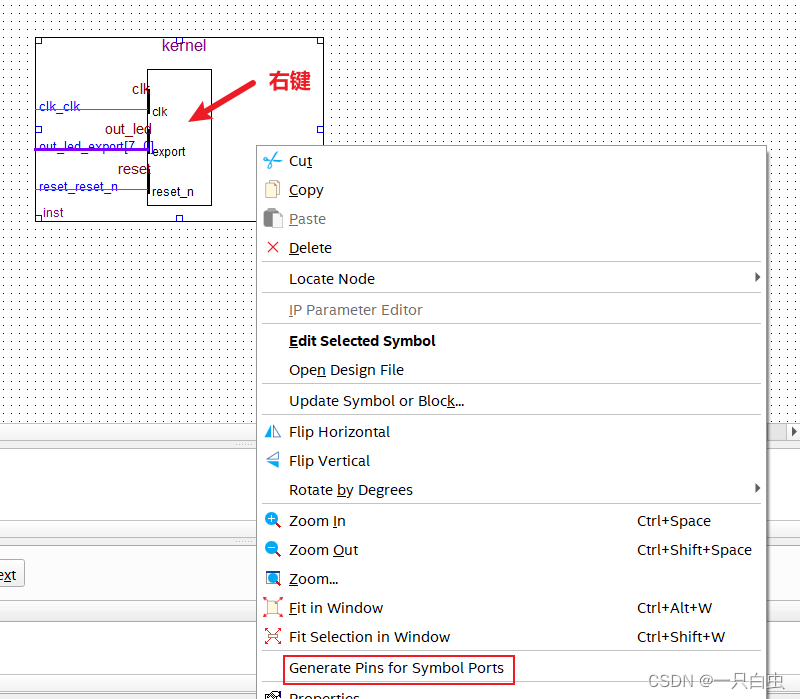

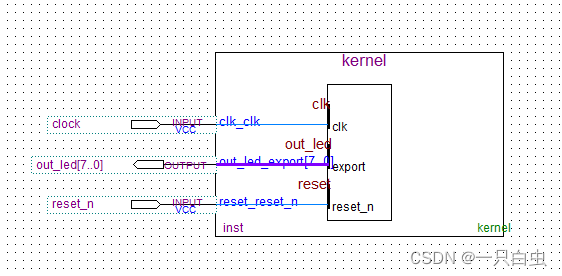

3、 进行逻辑连接和生成管脚

生成管脚

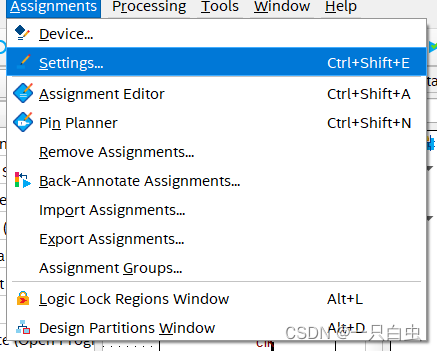

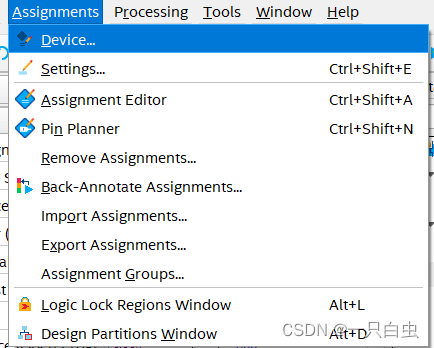

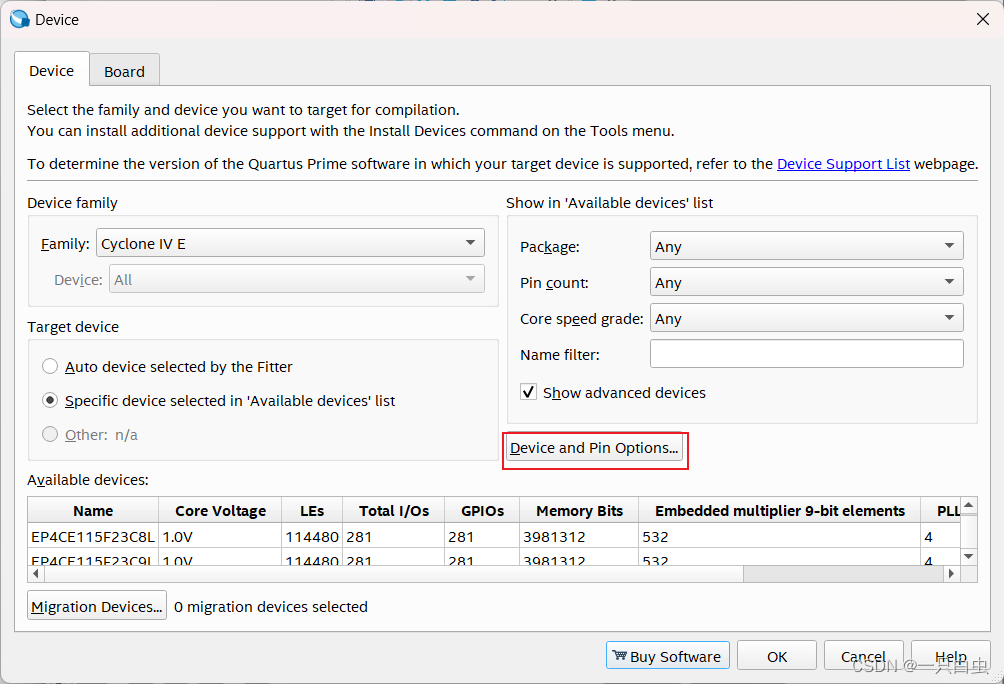

5、 芯片引脚设置

进行unused pin设置,可能会收到外部信号的干扰,将未用引脚设置为Asinput tri-stated。

进行unused pin设置,可能会收到外部信号的干扰,将未用引脚设置为Asinput tri-stated。

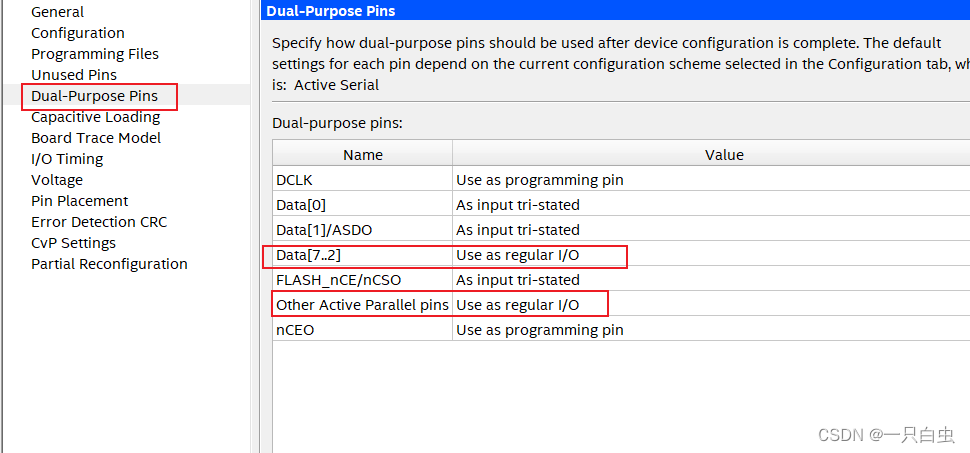

特殊引脚设置,设置为常规引脚

6、编译工程

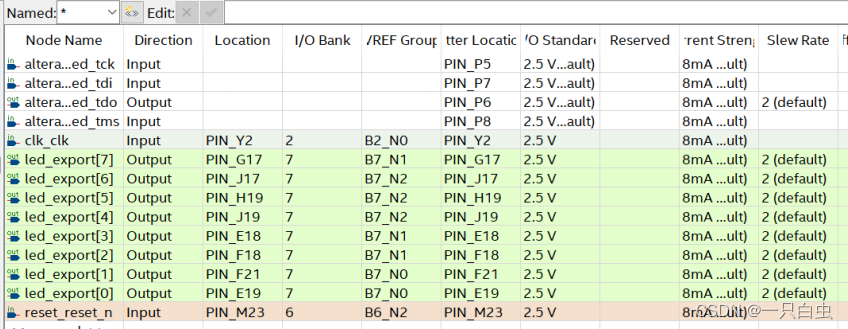

7、分配物理针脚

二、软件部分设计

二、软件部分设计

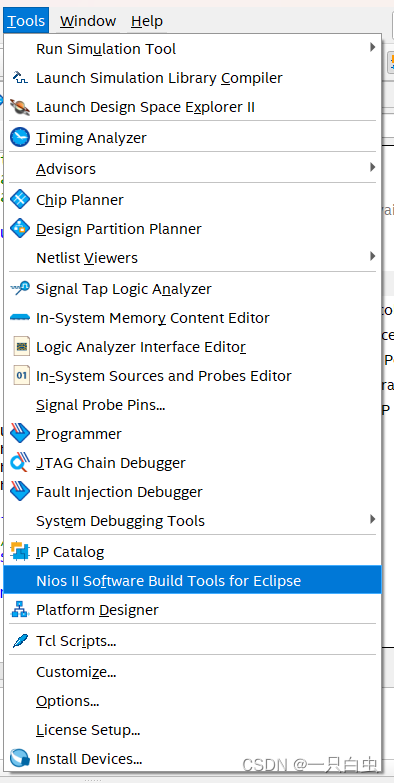

1、启动Nios II SBT

启动Workspace 选择当前的项目目录,点击OK

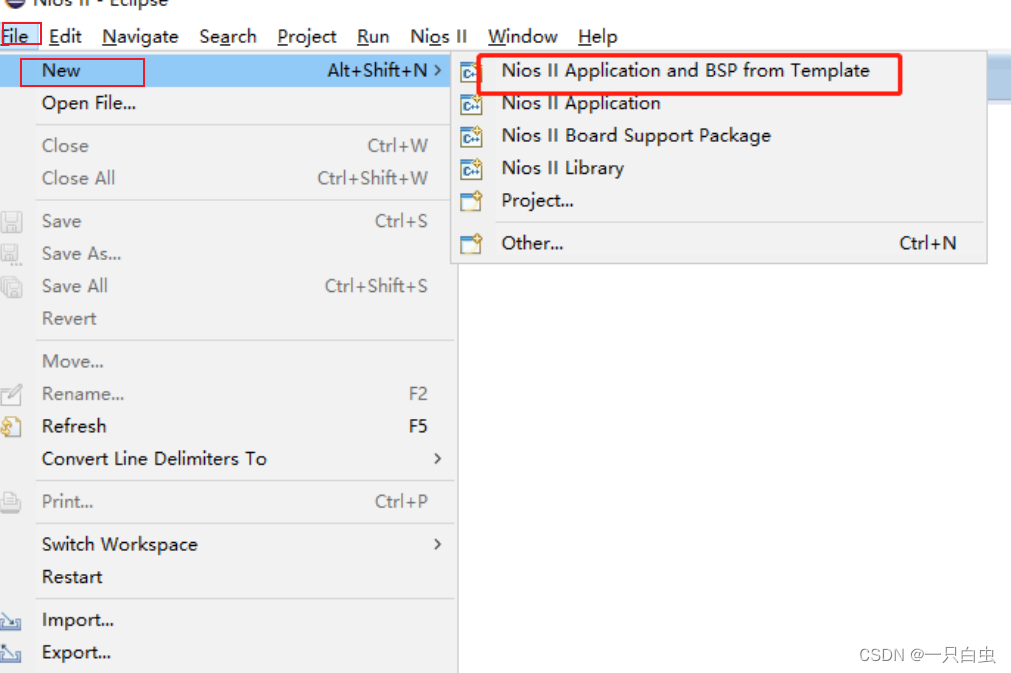

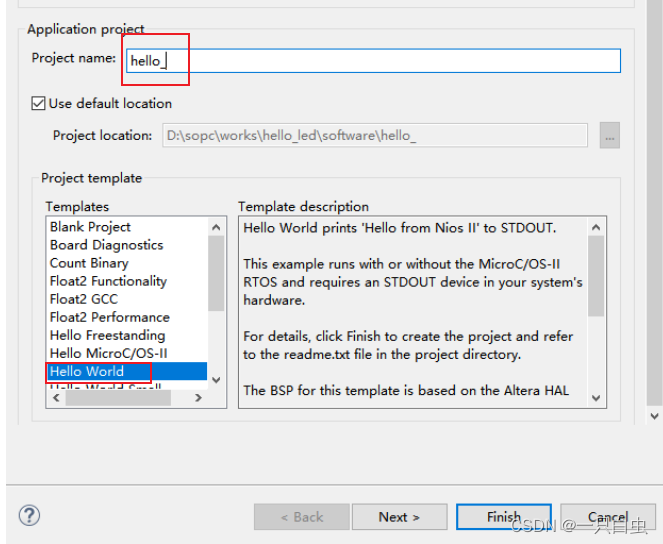

2、创建工程

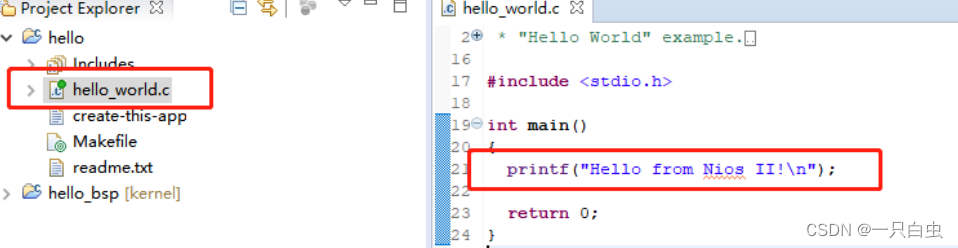

系统会自动生成一个打印“hello_world”的软件工程,在 hello_world.c 中我们可以看到相应代码

4、修改程序

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

const alt_u8

led_data[8]={0x01,0x03,0x07,0x0F,0x1F,0x3F,0x7F,0xFF};

int main (void)

{

int count=0;

alt_u8 led;

volatile int i;

while (1)

{ if (count==7)

{count=0;}

else

{count++;}

led=led_data[count];

IOWR_ALTERA_AVALON_PIO_DATA(PIO_LED_BASE, led);

i = 0;

while (i<500000)

i++;

}

return 0;

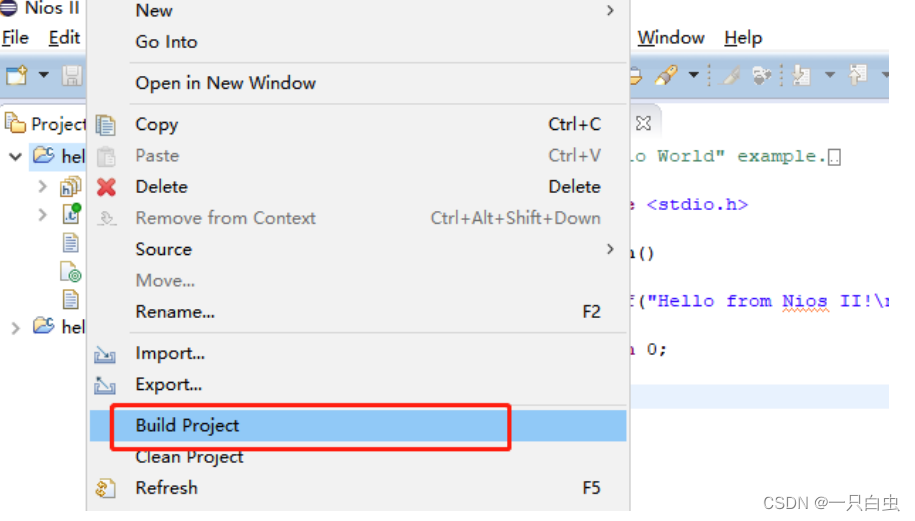

}5、编译工程

三、运行项目

三、运行项目

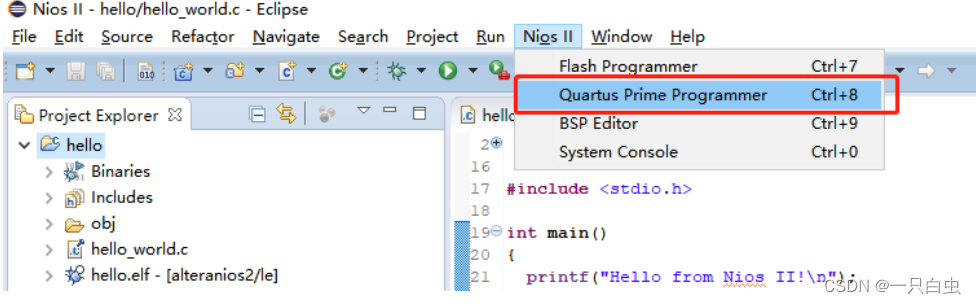

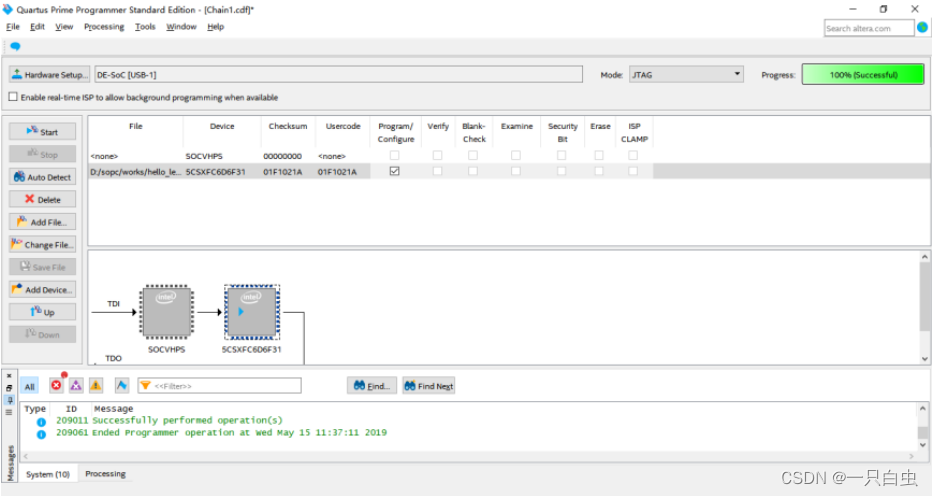

1、配置FPGA

添加下载文件,然后点击 Start 开始下载

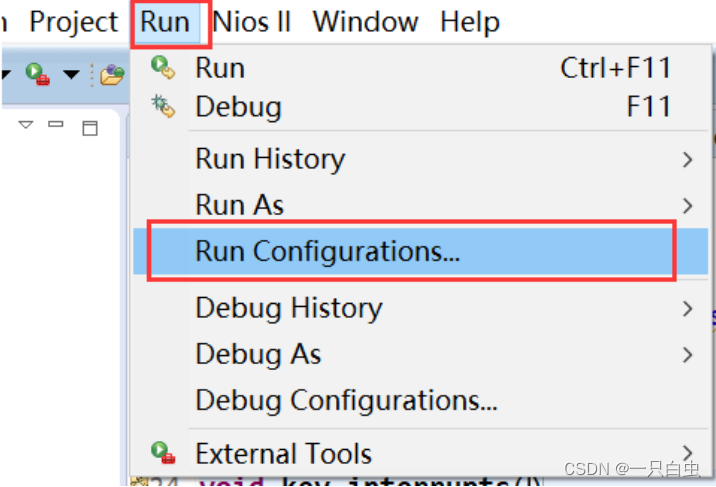

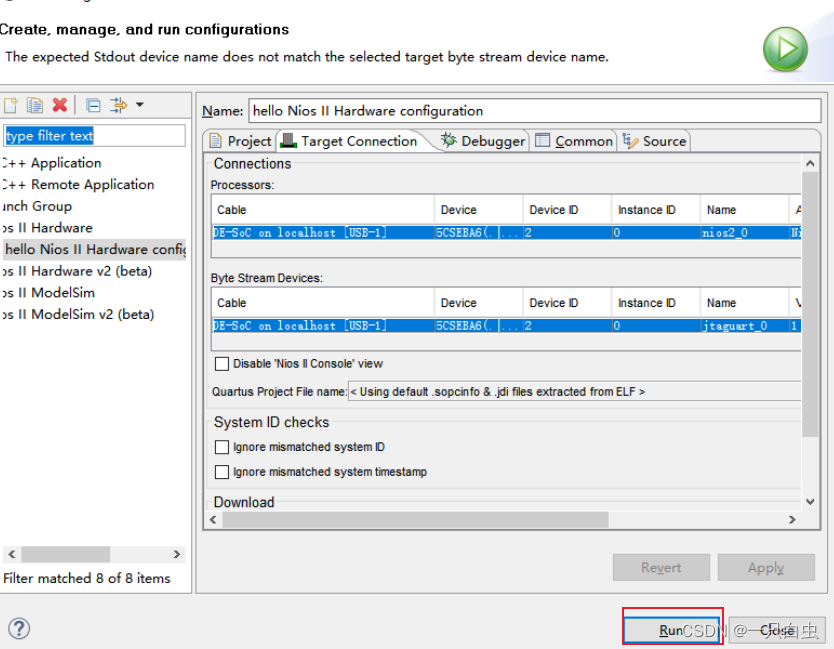

2、运行/调式程序

配置 Run Configurations

1364

1364

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?