摘 要:

本实验通过Quartus软件完成对十六选一数据选择器的四种VHDL程序,分别为if;case;when else;when select四种方式,实现波形图的生成。同时,加深对VHDL语言的理解和使用多种方式完成任务的能力,提高实验操作能力。

关键词:Quartus;VHDL

引言

随着数字电路技术的迅猛进步,VHDL已成为硬件描述语言中的关键利器。利用VHDL,工程师能够精准地描绘电路逻辑,并通过仿真工具验证设计的准确性,进而生成对应的波形图。在本文中,我们将依据十六选一数据选择器的原理,采用Quartus软件编写四种VHDL代码,以直观地展示并生成所需的波形图,这样的工作流程使得电路设计、验证与仿真更加高效、精确。

一、电路分析

1、JK触发器

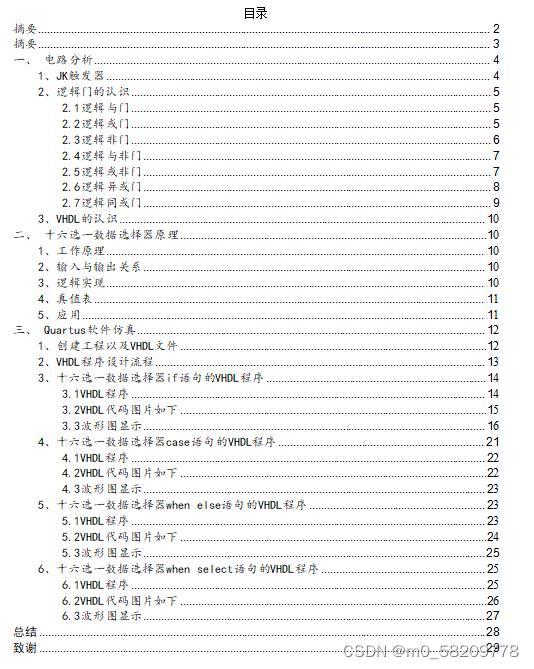

1.1电路结构

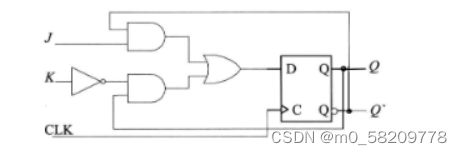

1.2 图形符号

1.3 真值表

1.4 逻辑表达式

![]()

1.5 边沿JK触发器的特点

1、CLK的上升沿或下降沿触发。

2、抗干扰能力极强,工作速度很高,在触发沿瞬间,按 Q*=J`Q+`KQ的规定更新状态。

3、功能齐全,有保持、置0、置1、翻转功能,使用方便。

2、逻辑门的认识

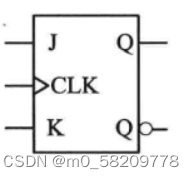

2.1、逻辑与门(AND):

2.1.1 图形符号:

2.1.2 逻辑符号

2.1.3 真值表:

| 输入 |

输出 |

|

| A |

B |

Y |

| 0 |

0 |

0 |

| 0 |

1 |

0 |

| 1 |

0 |

0 |

| 1 |

1 |

1 |

2.1.4 逻辑表达式:

Y=AB

2.1.5 两输入与门的功能:

与门是实现逻辑“乘”运算的电路,有两个以上输入端,一个输出端(一般电路都只有一个输出端,ECL电路则有二个输出端)。只有当所有输入端都是高电平(逻辑“1”)时,该电路输出才是高电平(逻辑“1”),否则输出为低电平(逻辑“0”)。

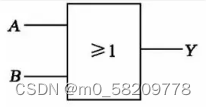

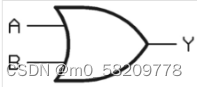

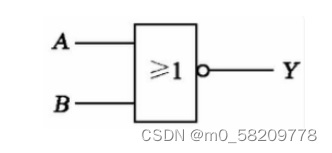

2.2、逻辑或门(OR):

2.2.1 图形符号:

2.2.2 逻辑符号:

2.2.3 真值表:

| 输入 |

输出 |

|

| A |

B |

Y |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

1 |

2.2.4 逻辑表达式:

Y=A+B

2.2.5 两输入或门功能:

或门是实现逻辑加的电路,又称逻辑和电路,简称或门。此电路有两个以上输入端,一个输出端。只要有一个或几个输入端是 “1”,或门的输出即为 “1”。而只有所有输入端为 “0”时,输出才为 “0”。

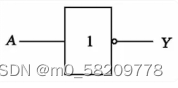

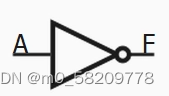

2.3 逻辑非门(NOT):

2.3.1 图形符号:

2.3.2 逻辑符号:

2.3.3 真值表:

| 输入 |

输出 |

| A |

Y |

| 0 |

0 |

| 1 |

1 |

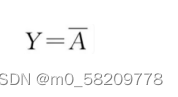

2.3.4 逻辑表达式:

2.3.5 非门功能:

实现逻辑代数非的功能,即输出始终和输入保持相反。当输入端为高电平(逻辑“1”)时,输出端为低电平(逻辑“0”);反之,当输入端为低电平(逻辑“0”)时,输出端则为高电平(逻辑“1”)

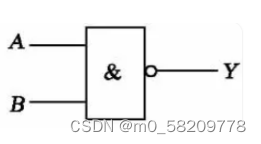

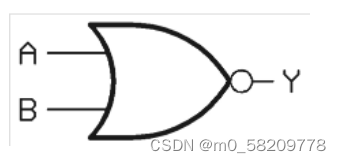

2.4 逻辑与非门(NAND):

2.4.1 图形符号:

2.4.2 逻辑符号:

2.4.3 真值表:

| 输入 |

输出 |

|

| A |

B |

Y |

| 0 |

0 |

1 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

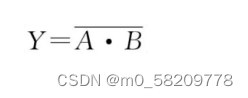

2.4.4 逻辑表达式:

2.4.5 两输入与非门功能:

与非门则是当输入端中有1个或1个以上是低电平时,输出为高电平;只有所有输入是高电平时,输出才是低电平。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1014

1014

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?