计组课后作业复习资料合集

- 定量分析n体交叉存储器连续读取n个字所需要的时间

2、(指导教材,例题4.10)设某机器主存容量为16MB,缓存容量为16KB,每字块有8个字,每个字32位,设计一个4路组相连映射,要求:

(1)画出主存地址字段中各段的位数

(2)设缓存初始状态为空,CPU依次从主存第0、1、2、…、99号单元读出100个字(主存一次读出一个字),重复8次,问命中率多少?

(3)若缓存速度是主存6倍,有缓存和无缓存相比,速度提升了多少倍?

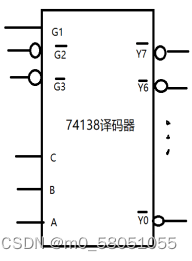

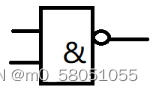

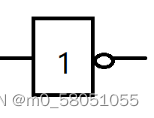

- (指导教材,习题32)设CPU共有16根地址线和8根数据线,并用作为访存控制信号(低电平有效),作为读/写命令信号(高电平读,低电平写)。现有下列存储芯片:1K*4位RAM,4K*8位RAM,2K*8位ROM,以及74138译码器和各种门电路,如下图所示。画出CPU和存储芯片的连接图。要求

- 主存地址空间分配:8000H~87FFH为系统程序区;8800H~8BFFH为用户程序区,

- 合理选用上述存储芯片,说明各选几片

- 详细画出存储芯片的片选逻辑

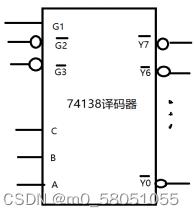

- (指导教材,习题33)设CPU共有16根地址线和8根数据线,并用作为访存控制信号(低电平有效),作为读/写命令信号(高电平读,低电平写)。现有下列存储芯片:1K*4位RAM,4K*8位RAM,2K*8位ROM,以及74138译码器和各种门电路,如下图所示。画出CPU和存储芯片的连接图。要求

(1)主存地址空间分配:A000H~A7FFH为系统程序区;A800H~AFFFH为用户程序区

(2)合理选用上述存储芯片,说明各选几片

(3)详细画出存储芯片的片选逻辑

5.(课本,习题5.4)试比较程序查询方式、程序中断方式、DMA方式对CPU工作效率的影响

6.(课本,习题5.20)试比较单重中断和多重中断服务程序的处理流程,说明有何不同

7.(习题集,问答题14)DMA方式有没有中断请求?为什么?

8.(习题集,问答题33)CPU对DMA请求和中断请求的响应时间是否一样?为什么?

9.设机器数字长为8位(含一位符号位在内),写出对应下列真值的原码、补码和反码:

-13/64 , 29/128, 100, -87

10.当十六进制数9BH和FFH分别表示原码、补码、反码和无符号数时,所对应的十进制数各为多少(设机器数采用1位符号位)

11、写出51/128,-86.5所对应的机器数,要求:

(1)阶码5位,含1位阶符,尾数11位,含1位数符,阶码和尾数均为原码

(2)阶码5位,含1位阶符,尾数11位,含1位数符,阶码和尾数均为补码

(3)IEEE 754单精度浮点数格式

12、设浮点数长度位32位,欲表示+/-6万间的十进制数,在保证数的最大精度的条件下,除阶符、数符各取一位外,阶码和尾数各取几位?

13、已知二进制数x=0.1010,y=-0.0110,要求:

(1)用原码一位乘法计算[xy]原

(2)用补码一位乘法计算[xy]补

14、已知二进制数x=0.10110,y=0.11111,要求:

(1)用原码加减交替法计算[x/y]原

(2)用补码一位除法计算[x/y]补

15、推导出四位并行加法的并行进位链的进位表达式,并画出对应的逻辑图(即图6.21)。

16、(课本习题7.7)设指令字长为16位,采用扩展操作码技术,每个操作数的地址为6位。如果定义了13条二地址指令,试问还可以安排多少条一地址指令?

17、(课本习题7.19)CPU内有32个32位的通用寄存器,设计一种能容纳64种操作的指令系统。假设指令字长等于机器字长,回答:

(1)如果主存可以直接或间接寻址,采用寄存器-存储器型指令,能直接寻址的最大存储空间是多少?画出指令格式并说明各字段含义。

(2)在满足(1)的前提下,如果采用通用寄存器作为基址寄存器,则上述寄存器-存储器型指令的指令格式有何特点?画出指令格式并指出这类指令可访问多大的存储空间。

18、假设指令流水线分为取指(IF)、译码(ID)、执行(EX)、回写(WR)四个过程,共有10条指令连续输入此流水线。

(1)画出指令流程图

(2)画出非流水线时空图

(3)画出流水线时空图

(4)假设时钟周期为100ns,求流水线的实际吞吐率

(5)求该流水线的加速比

(6)求该流水线的效率

19、设机器有4个中断源1、2、3、4,其硬件排序优先次序按1->2->3->4降序排序,各中断源的服务程序中所对应的屏蔽字如表所示

| 中断源 | 屏蔽字 | |||

| 1 | 2 | 3 | 4 | |

| 1 | 1 | 1 | 0 | 1 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 1 | 1 | 1 | 1 |

| 4 | 0 | 1 | 0 | 1 |

(1)给出上述4个中断源的中断处理次序

(2)若4个中断源同时有中断请求,画出CPU执行程序的轨迹

20.什么是指令周期、机器周期、时钟周期?三者有何关系?

21.设CPU内部结构如图9.4所示,此外设有R1~R44个寄存器,它们各自的输入和输出都与内部总线相通,并分别受控制信号控制,要求从取指令开始,写出完成下列指令所需的全部微操作和控制信号:

ADD R2,@R4 ((R2)+((R4)))→R2

22.写出完成下列指令的微操作及节拍安排(包括取指阶段)

ADD R1,X 将R1寄存器的内容和主存X单元的内容相加结果存于R1的操作。

1729

1729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?