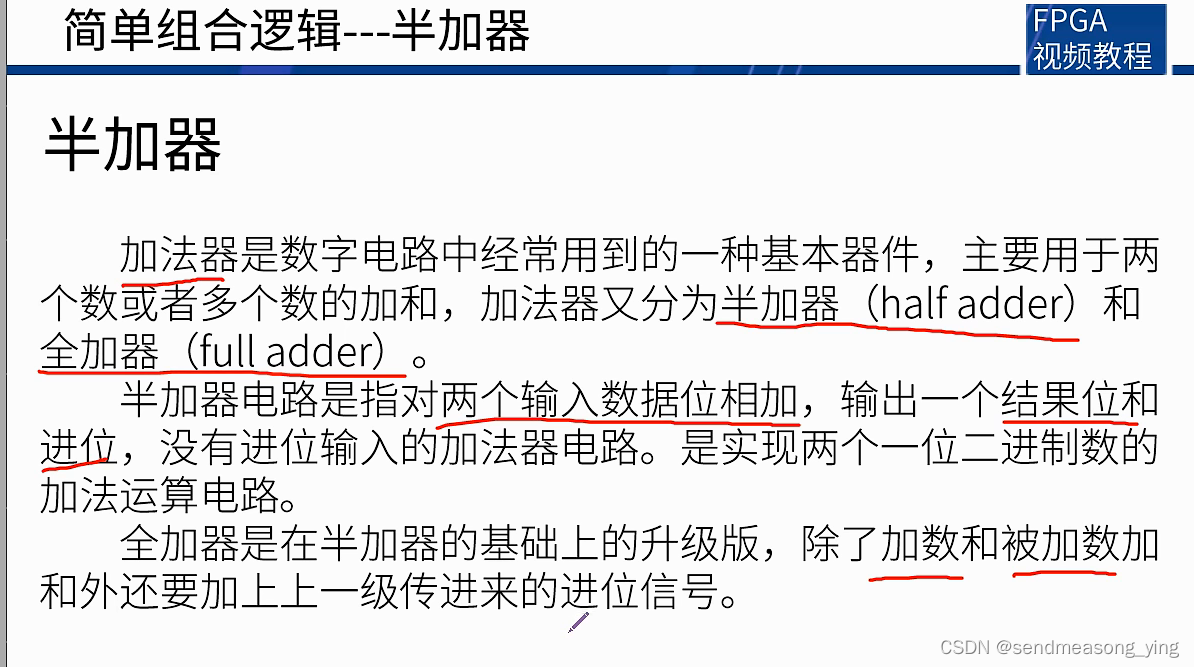

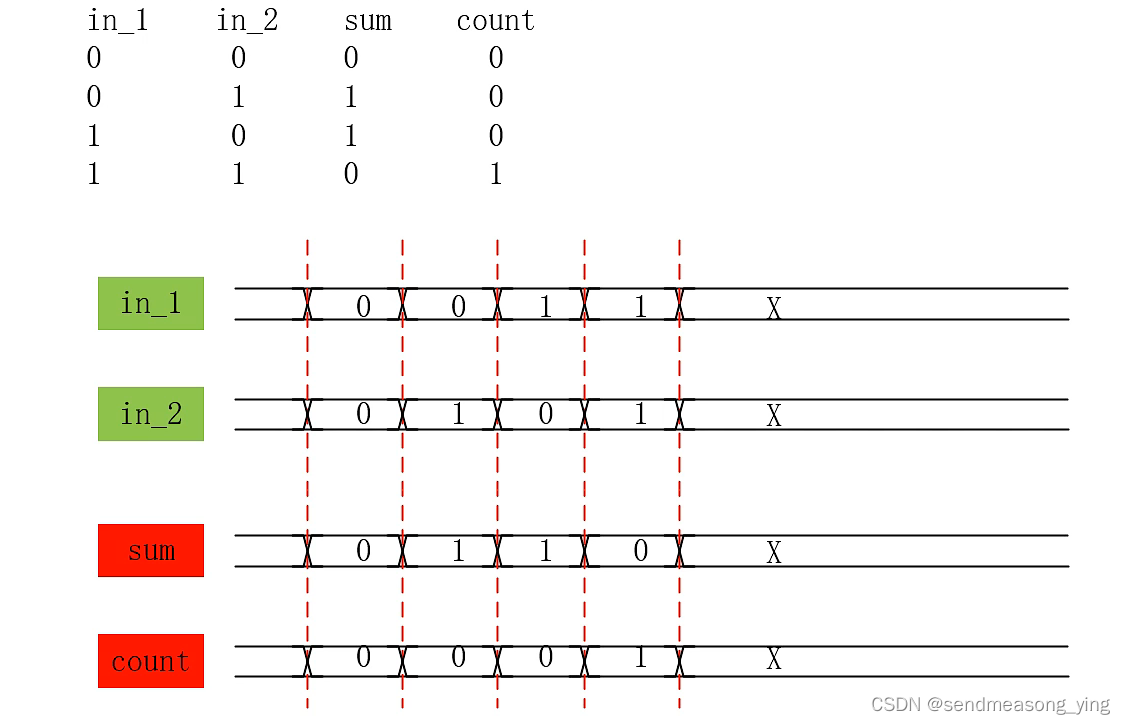

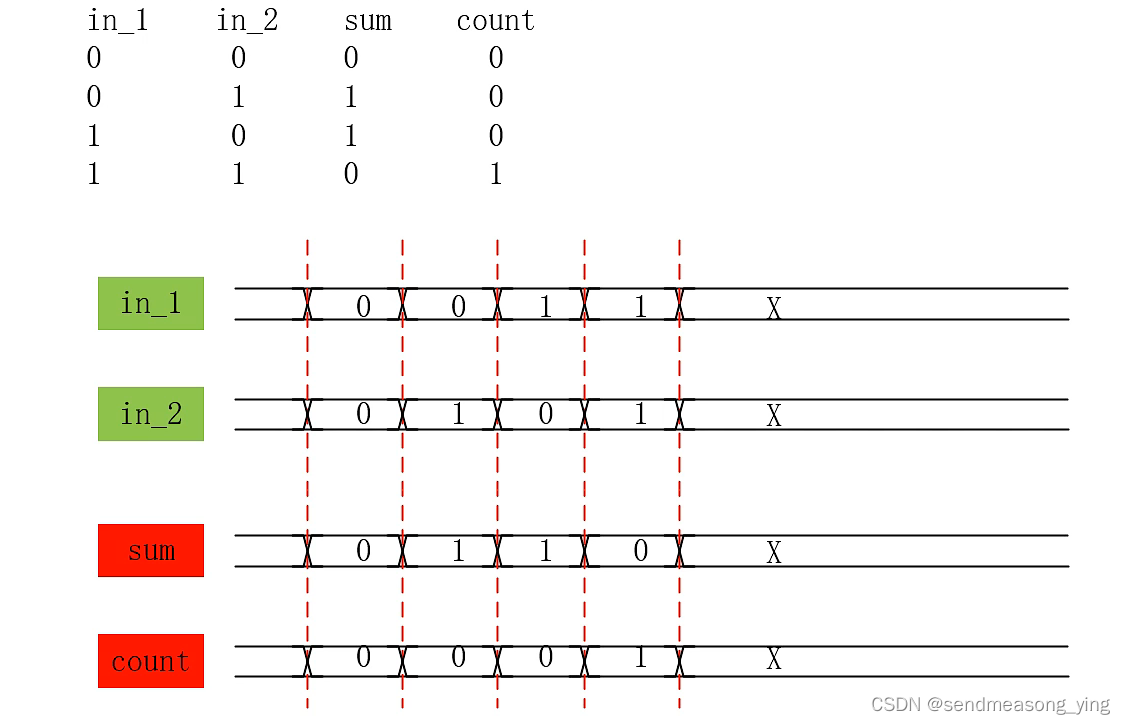

1.原理

2.代码

2.1 half_adder.v

module half_adder

(

input wire in_1 ,

input wire in_2 ,

output wire sum ,

output wire count

);

assign {count,sum}=in_1+in_2;

endmodule

2.2 tb_half_adder.v

`timescale 1ns/1ns

module tb_half_adder();

reg in_1;

reg in_2;

wire sum;

wire count;

initial

begin

in_1<=1'b0;

in_2<=1'b0;

end

always# 10 in_1={$random}%2;

always# 10 in_2={$random}%2;

initial

begin

$timeformat(-9,0,"ns",6);

$monitor("@time %t:in_1=%b,in_2=%b,sum=%b,count=%b",$time,in_1,in_2,sum,count);

end

half_adder half_adder_inst

(

.in_1 (in_1),

.in_2 (in_2),

.sum (sum),

.count (count)

);

endmodule

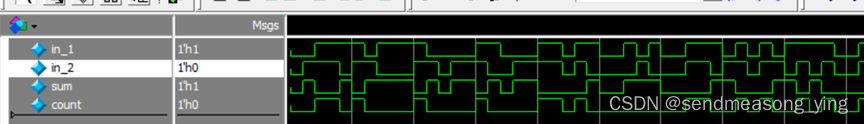

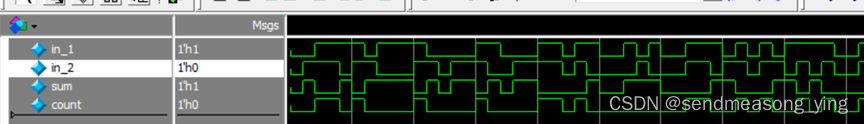

本文详细介绍了使用Verilog语言编写的半加器模块(half_adder.v),以及其测试脚本(tb_half_adder.v),展示了如何定义输入、输出并进行时序仿真。

本文详细介绍了使用Verilog语言编写的半加器模块(half_adder.v),以及其测试脚本(tb_half_adder.v),展示了如何定义输入、输出并进行时序仿真。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?