目录

一、理论部分

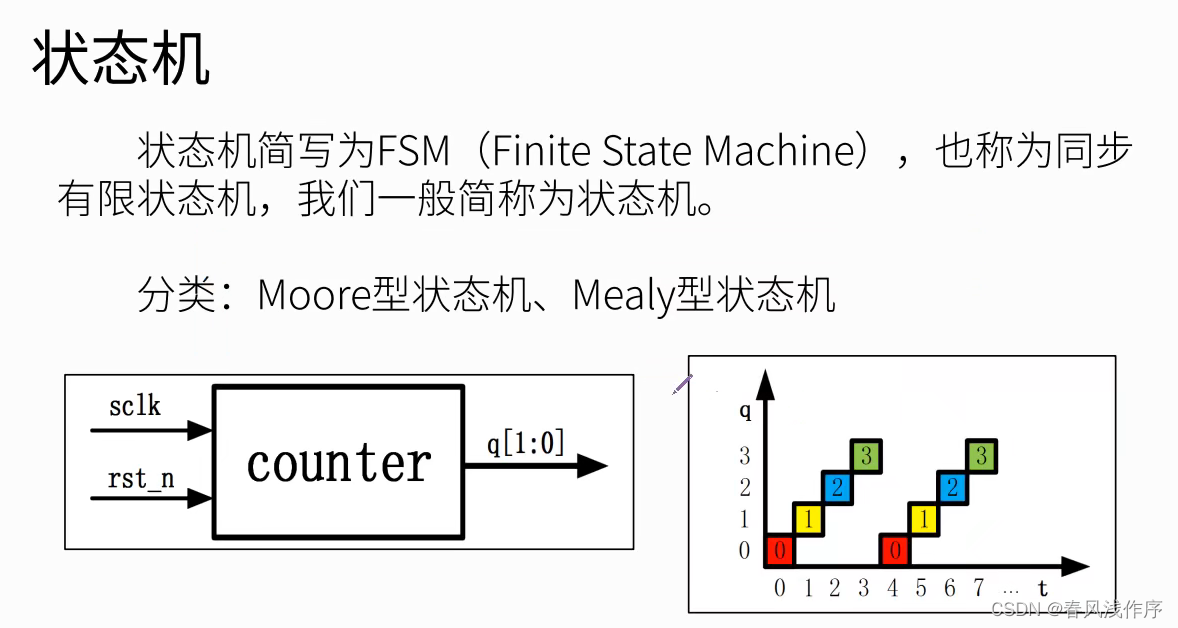

状态机的作用:FPGA为并行执行的,若想处理具有前后顺序的事件,则需要用到状态机。

Moore型状态机:输出只与当前状态有关,而与输入无关。

Mealy型状态机:输出与当前状态、输入均有关。

共同点是状态的跳转都只和输入有关。

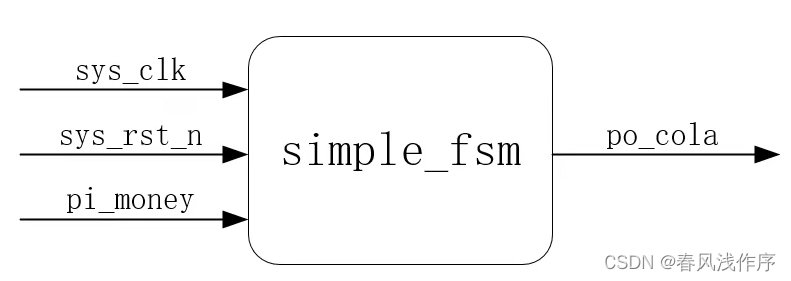

二、模块框图

包含三个输入信号:系统时钟(sys_clk)、复位信号(sys_rst_n)以及投币信号(pi_money)。

一个输出信号:输出可乐(po_cola)。

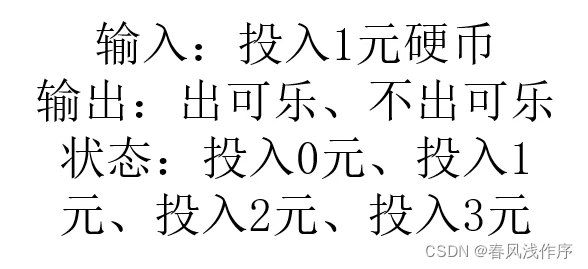

三、状态转移图

(一次投币信号算作投币一元,故每三次投币信号才能输出一个可乐)

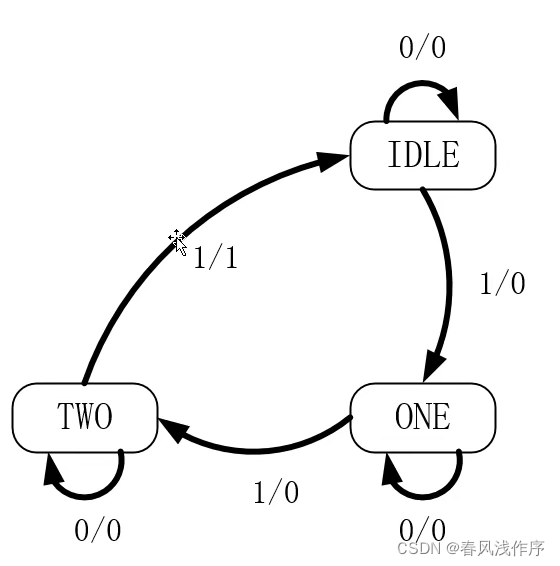

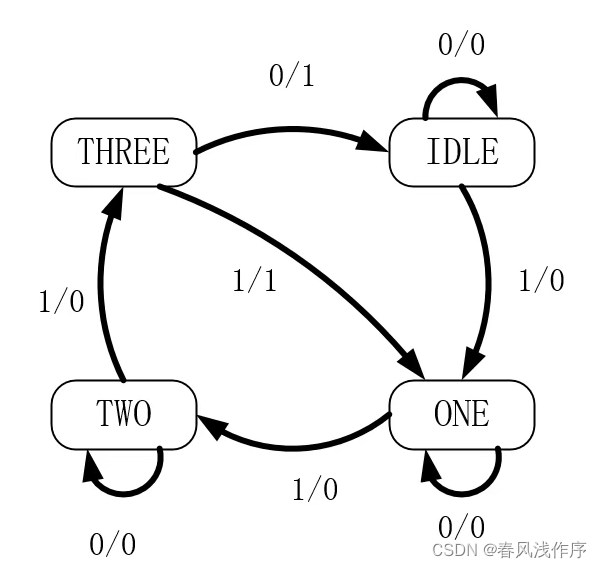

“/”左边为输入,右边为输出。

Mealy型状态机状态转移图:

Moore型状态机状态转移图:

因Mealy型状态机更节省逻辑资源,故使用Mealy型状态机完成本实验。

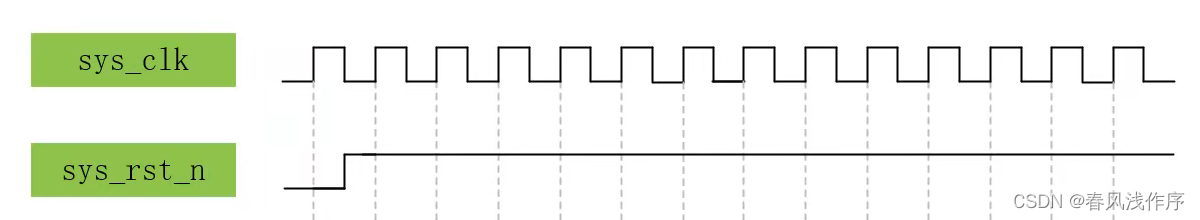

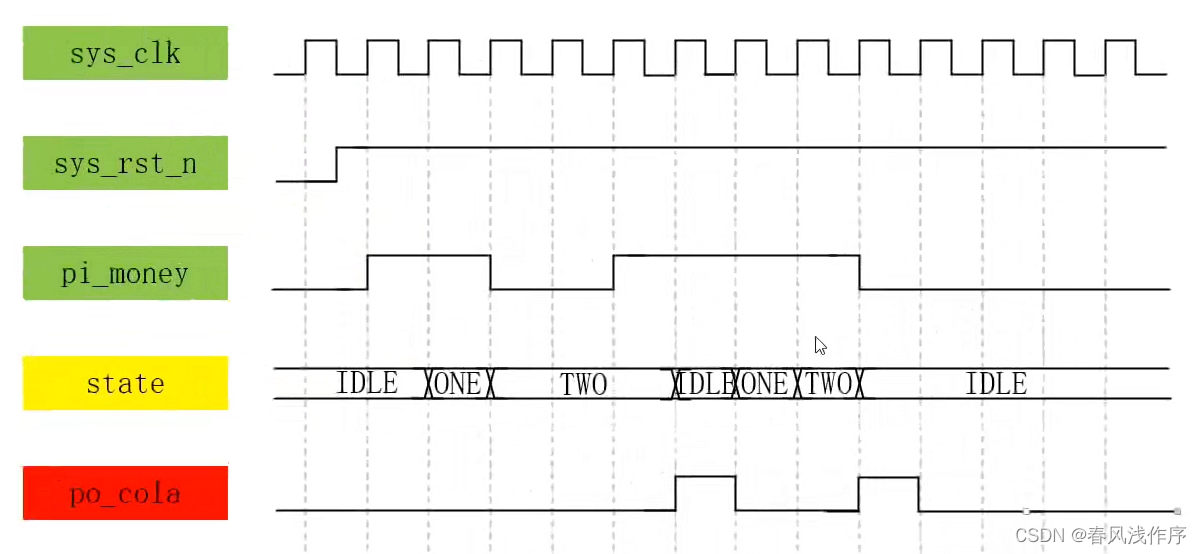

四、波形图

1、时钟与复位信号

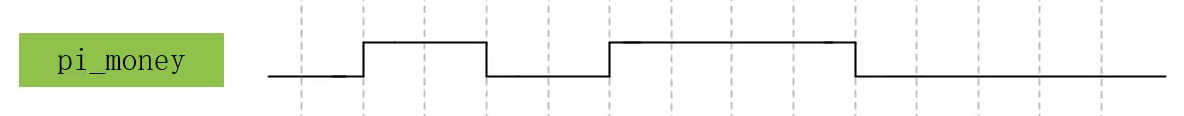

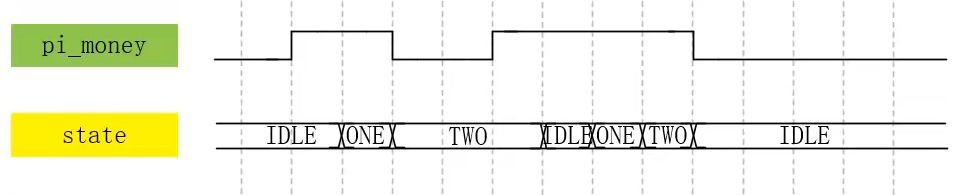

2、投币信号

(随机画出)

3、状态信号

4、输出信号

五、代码部分

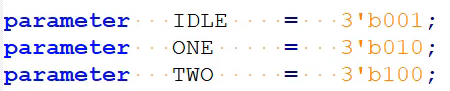

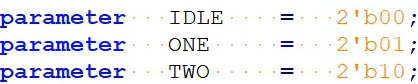

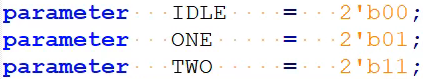

1、三种码型

独热码:

综合时节省组合逻辑的资源,但位宽较长。

二进制码:

位宽少,因此减少了寄存器资源的使用,但综合器综合时无法进行比较器的优化,因此使用的组合逻辑资源较多。

格雷码(相邻参数只有一个比特不同,例如00与01,01与11):

状态数较多(位宽较大)时使用,寄存器资源使用较少,组合逻辑资源使用较多,

以上三种编码均可,因FPGA中组合逻辑资源较少,相对来说寄存器资源较多,所以使用独热码较好,此实验采用独热码。

总结:

低速系统中,如果状态机状态的个数小于四个,使用二进制码;

状态个数介于4~24个,使用独热码,

状态个数大于24个,使用格雷码。

高速系统中,无论状态个数是多少,最好都使用独热码。

2、状态机的三种写法

一段式:

在一段的状态机中使用时序逻辑,即描述状态的转移,又描述状态的输出。

较难表述大型状态机。

二段式:

分两段状态机,第一段状态机中使用时序逻辑描述状态的转移;在第二段状态机中使用组合逻辑描述数据的输出。

本文详细介绍了如何利用Mealy型状态机解决FPGA中的事件顺序控制问题,包括理论阐述、模块设计、状态转移图、波形分析以及Verilog代码实现。通过三种编码方式的比较,最后选择了独热码进行资源优化。还展示了状态机的三种写法和关键代码片段,以及仿真结果的验证。

本文详细介绍了如何利用Mealy型状态机解决FPGA中的事件顺序控制问题,包括理论阐述、模块设计、状态转移图、波形分析以及Verilog代码实现。通过三种编码方式的比较,最后选择了独热码进行资源优化。还展示了状态机的三种写法和关键代码片段,以及仿真结果的验证。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?