我们在进行寄存器模型的后门操作时,必须提前设置后门操作路径,以此RAL模型方能进行操作。

``

``

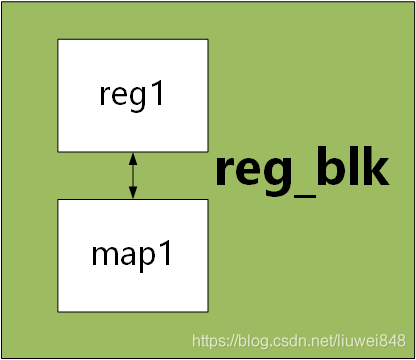

在上面这个RAL 模型中,当调用reg_blk.reg1.write(*),参数指定是后门操作(UVM_BACKDOOR),那么RAL模型时如何取得硬件rtl的绝对路径?

核心的方法是调用reg::get_full_hdl_path,下面来讨论一下,首先reg

的rtl路径有两部分组成,分别是(1)uvm_reg_block的基路径(我们叫做reg的base_path)(2)reg本身自己的相对路径(我们叫做reg的offset_path)。

首先是reg的base_path:这个path定义在reg所在的block中(也叫做block的路径),设置block的路径的方式有两种(uvm_reg_block中有两个变量用来存放block的路径)

(1) uvm_object_string_pool #(uvm_queue#(string)) hdl_paths_pool

(2) string root_hdl_paths[string]

其中对于hdl_paths_pool,形象的表示如下

当调用reg_blk.add_hdl_path(path)时会增加一个路径,如果调用4次,则会增加4次路径,如上图所示

对于root_hdl_paths,调用reg_blk.set_hdl_path_root(root_path)来设置路径

``

``

那么最终bloc

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6744

6744

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?