译码器

译码是编码的逆过程,在编码时,每一种二进制代码,都赋予了特定的含义,即都表示了一个确定的信号或者对象。把代码状态的特定含义翻译出来的过程叫做译码,实现译码操作的电路称为译码器。或者说,译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

译码器是一种多输入多输出组合逻辑电路器件,其可以分为:变量译码和显示译码两类

实例:3-8译码器

1、功能图

2、真值表

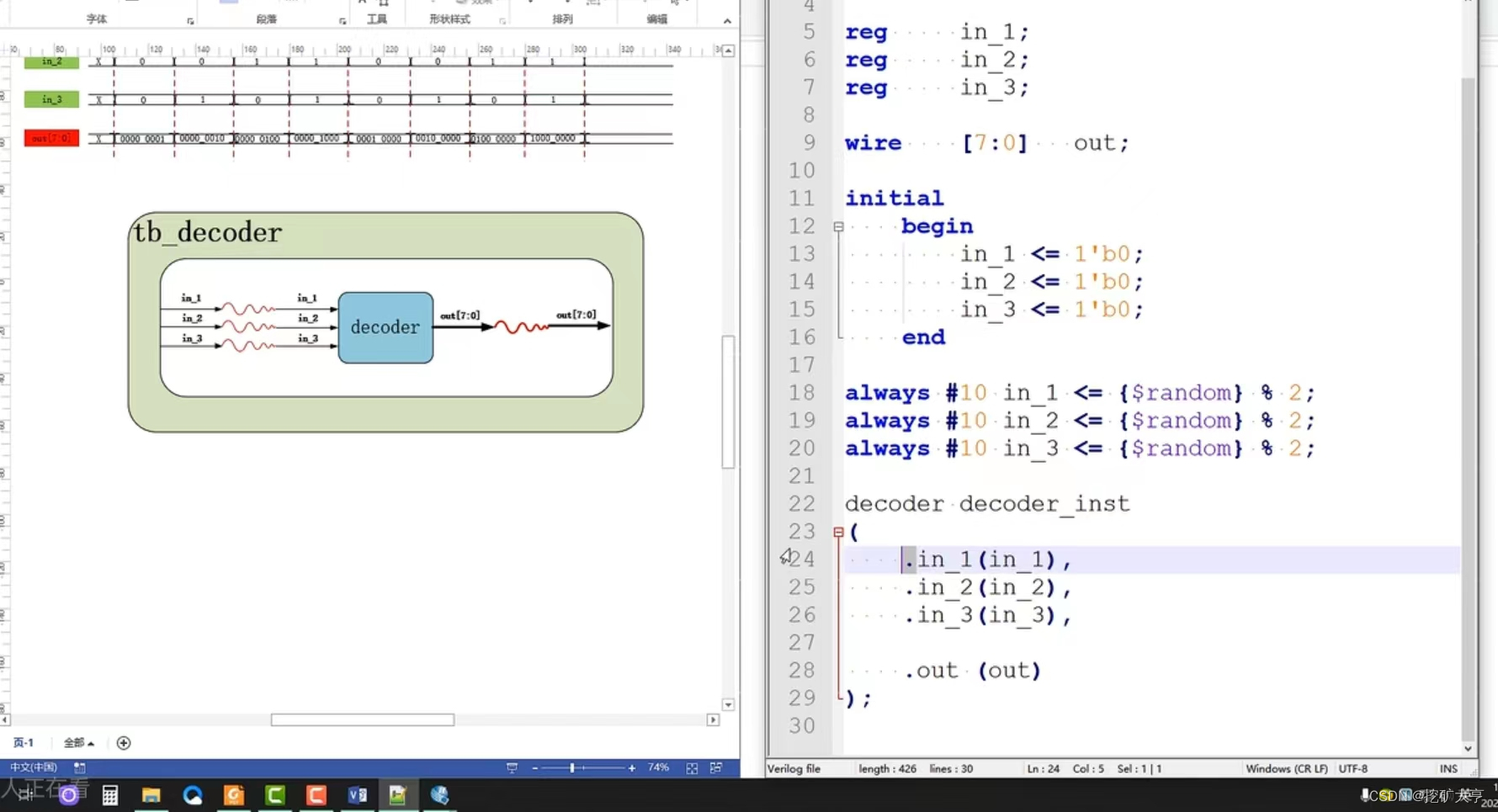

3、波形图

//trl目录下:

module decoder

(

input wire in_1,

input wire in_2,

input wire in_3,

output reg [7:0] out

);

always@(*)

if({in_1,in_2,in_3} == 3'b000)

out = 8'b0000_0001;

else if({in_1,in_2,in_3} == 3'b001)

out = 8'b0000_0010;

else if({in_1,in_2,in_3} == 3'b010)

out = 8'b0000_0100;

else if({in_1,in_2,in_3} == 3'b011)

out = 8'b0000_1000;

else if({in_1,in_2,in_3} == 3'b100)

out = 8'b0001_0000;

else if({in_1,in_2,in_3} == 3'b101)

out = 8'b0010_0000;

else if({in_1,in_2,in_3} == 3'b110)

out = 8'b0100_0000;

else if({in_1,in_2,in_3} == 3'b111)

out = 8'b1000_0000;

else

out = 8'b0000_0001;

endmodule

采用case条件分支语句的编写:

always@(*)

case({in_1,in_2,in_3})

3'b000:out = 8'b0000_0001;

3'b001:out = 8'b0000_0010;

3'b010:out = 8'b0000_0100;

3'b011:out = 8'b0000_1000;

3'b100:out = 8'b0001_0000;

3'b101:out = 8'b0010_0000;

3'b110:out = 8'b0100_0000;

3'b111:out = 8'b1000_0000;

default:out = 8'b0000_0001;

endcase

if-else和case分支语句,使用上面两种不同的代码编写方式,虽然它能够实现同样的功能,但是它们得到的RTL视图差别是比较大。

if-else写法存在优先级,它首先判断第一个if条件,如果它的条件满足,它就会执行这条语句,如果条件不满足,就会执行下一条语句,直到某个条件满足,执行完成之后就会跳出,如果所有条件不满足,就会执行else语句;然后case语句,任何时候都不存在优先级的问题,通过判断case中的条件,等于列表中的某一个条件,就执行后面的语句

/sim目录下

仿真文件的编写:

'timescale 1ns/1ns

module tb_decoder();

reg in_1; //只要使用always和initial赋值的一律是reg型,使用assign一律是wire型

reg in_2;

reg in_3;

wire [7:0] out;

initial

begin

in_1<= 1'b0;

in_1<= 1'b0;

in_1<= 1'b0;

end

always #10 in_1 <= {$random} % 2;

always #10 in_2 <= {$random} % 2;

always #10 in_3 <= {$random} % 2;

initial

begin

$timeformat(-9,0,"ns",6);//时间格式

$monitor("@time.%t:in_1=%b,in_2=%b,in_3=%b,out=%b",$time,in_1,in_2,in_3,out);

end

decoder decoder_inst

(

.in_1(in_1),

.in_2(in_2),

.in_3(in_3),

.out(out)

)

endmodule

实例化是什么意思??仿真同实际相连

前一个in_1是实例化里的in_1.

括号里的in_1同仿真模块里的名称一致,可以为其他名

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?