目录

1. 串行外设接口SPI简介

SPI接口(Serial Peripheral Interface,串行外设接口)是一种广泛应用于微控制器与外围设备之间的高速、全双工、同步串行通信协议。

2. SPI 主要特征

具有全双工和单工模式的主从操作;

16位宽度,独立的发送和接收缓冲区;

8位或16位数据帧格式;

低位在前或高位在前的数据位顺序;

软件和硬件NSS管理;

硬件CRC计算、发送和校验;

发送和接收支持DMA模式。

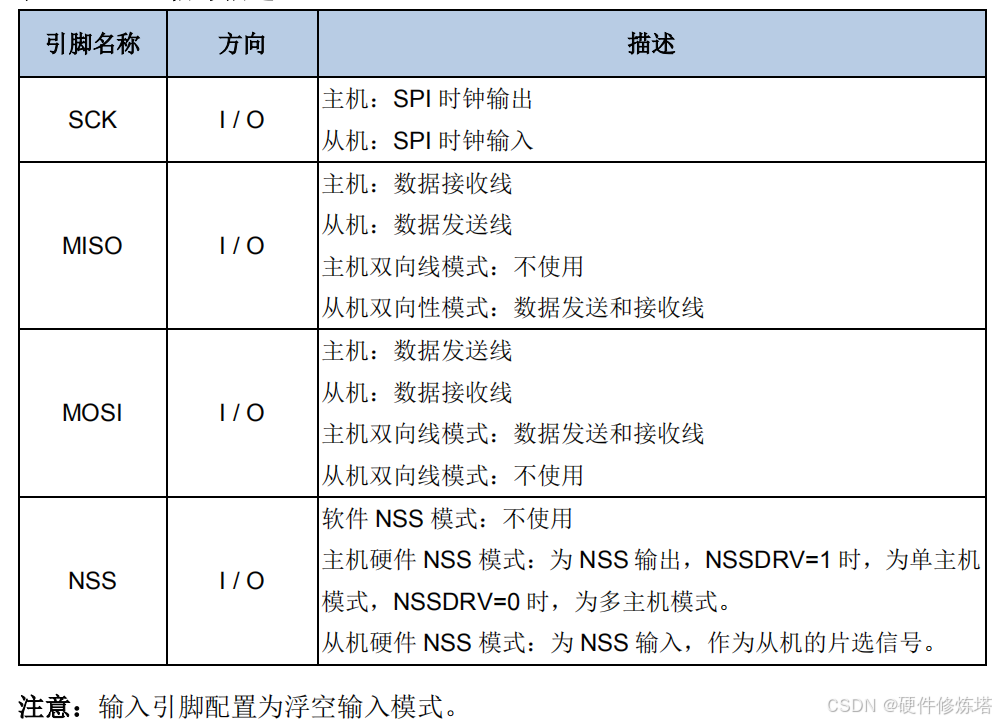

3. SPI接口引脚说明

SPI接口为4线制,下表中给出每个引脚的具体说明。

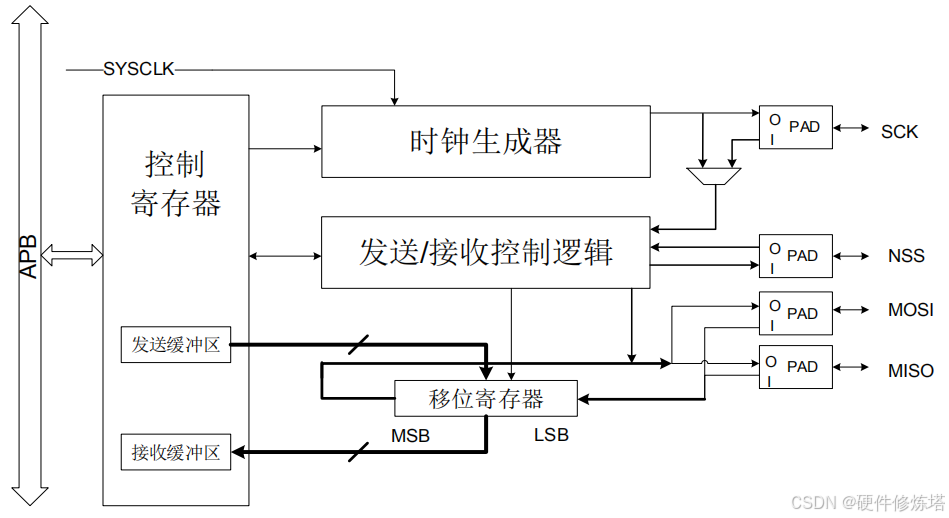

4. SPI功能说明

SCK功能:SPI 时序和数据帧格式

SPI_CTL0寄存器中的CKPL位和CKPH位决定了SPI时钟和数据信号的时序。CKPL位决定了空闲状态时SCK的电平,CKPH位决定了第一个或第二个时钟跳变沿为有效采样边沿。

在常规模式中,通过SPI_CTL0中的FF16位配置数据长度,当FF16=1时,数据长度为16位,否则为8位。

通过设置SPI_CTL0中的LF位可以配置数据顺序,当LF=1时,SPI先发送LSB位,当LF=0时,则先发送MSB位。

NSS片选功能

NSS也称(CS,chip select),即片选功能。

从机模式

当配置为从机模式(MSTMOD=0)时,在硬件NSS模式(SWNSSEN = 0)下,SPI从NSS引脚获取NSS电平,在软件NSS(SWNSSEN = 1)下,SPI根据SWNSS位得到NSS电平。只有当NSS为低电平时,发送或接收数据。在软件NSS模式下,不使用NSS引脚。

主机模式

在主机模式(MSTMOD=1)下,如果应用程序使用多主机连接方式,NSS可以配置为硬件输入模式(SWNSSEN=0, NSSDRV=0)或者软件模式(SWNSSEN=1)。一旦NSS引脚(在硬 件NSS模式下)或SWNSS位(在软件NSS模式下)被拉低,SPI将自动进入从机模式,并且产 生主机配置错误,CONFERR位置1。如 果 应 用 程 序 希 望 使 用 NSS 引 脚 控 制 SPI 从设备 , NSS 应 该 配 置 为 硬 件 输 出 模 式(SWNSSEN=0, NSSDRV=1)。使能SPI之后,NSS保持高电平,当发送或接收过程开始时,NSS变为低电平。

应用程序可以使用一个通用I/O口作为NSS引脚,以实现更加灵活的NSS应用。

通常硬件上会将NSS脚外接一个上拉电阻,因为在硬件NSS模式下,NSS引脚在发送数据完成后不会自动拉高,需要外接上拉电阻确保其能够正确回到高电平。另外SPI协议规定,当设备未被选中时,NSS引脚应保持高电平。上拉电阻可以确保在没有其他信号驱动时,NSS引脚维持高电平状态,避免因引脚悬空导致的不确定状态。

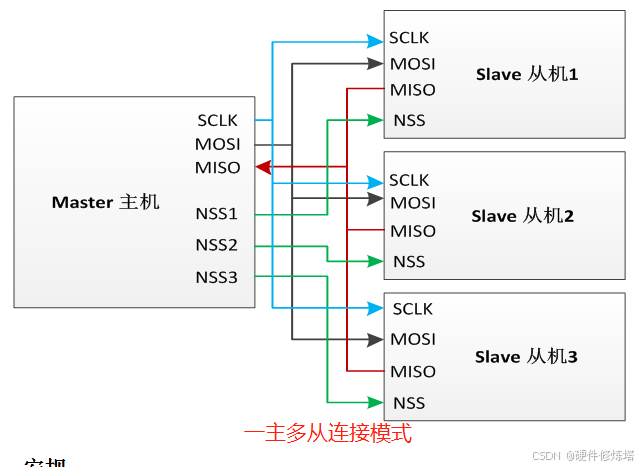

在一主多从机的SPI系统中,NSS引脚可以用一个普通的I/O口来替代。

5. SPI 基本发送和接收流程

发送流程

在完成初始化过程之后,SPI模块使能并保持在空闲状态。在主机模式下,当软件写一个数据通过APB总线将数据发送到缓冲区时,发送过程开始。在从机模式下,当SCK引脚上的SCK信号开始翻转,且NSS引脚电平为低,发送过程开始。所以,在从机模式下,应用程序必须确保在数据发送开始前,数据已经写入发送缓冲区中。当SPI开始发送一个数据帧时,首先将这个数据帧从数据缓冲区加载到移位寄存器中,然后开始发送加载的数据。在数据帧的第一位发送之后,TBE(发送缓冲区空)位置1。TBE标志位置 1,说明发送缓冲区为空,此时如果需要发送更多数据,软件应该继续写SPI_DATA寄存器。 在主机模式下,若想要实现连续发送功能,那么在当前数据帧发送完成前,软件应该将下一个数据写入SPI_DATA寄存器中。

接收流程

在最后一个采样时钟边沿之后,接收到的数据将从移位寄存器存入到接收缓冲区,RBNE(接收缓冲区非空)位置1。软件通过读SPI_DATA寄存器获得接收的数据,此操作会自动清除RBNE标志位。在MRU和MRB模式中,为了接收下一个数据帧,硬件需要连续发送时钟信号,而在全双工主机模式(MFD)中,当发送缓冲区非空时,硬件只接收下一个数据帧。

注意:当SPI处于从机模式,输入的时钟周期数不是8或16(配置的位宽决定)的整数倍个,片选关闭,此时SPI不会清除计数,片选使能后会再等相应数量的时钟周期后才收发新的数据。可以通过软件主动复位SPI模块来解决此问题。

框图中有一个很重要的总线:APB总线(Advanced Peripheral Bus)是AMBA(Advanced Microcontroller Bus Architecture)总线体系的一部分,主要用于低带宽、低功耗的外设连接。这里简单的介绍一下该总线的特点及应用:

6. APB总线的特点

低功耗:APB总线设计用于低功耗应用,适合连接低速外设。

非流水线设计:APB总线不是流水线式的,每次传输至少需要两个时钟周期。

简单性:APB总线的信号较少,接口设计简单,所有信号仅与时钟上升沿相关。

单主设备:APB总线通常只有一个主设备(如APB桥),其他设备均为从设备。

不支持高级功能:APB总线不支持burst传输、outstanding传输和读写同时传输。

7. APB总线的应用

低速外设连接:APB总线常用于连接低速外设,如UART、I2C、SPI、定时器等。

寄存器配置:APB总线也广泛用于配置各种IP模块的寄存器。

系统架构:在SoC设计中,APB总线通常通过桥接器连接到更高性能的总线(如AHB或AXI)

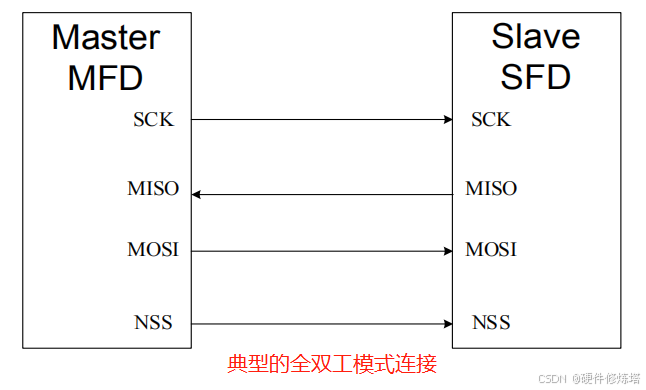

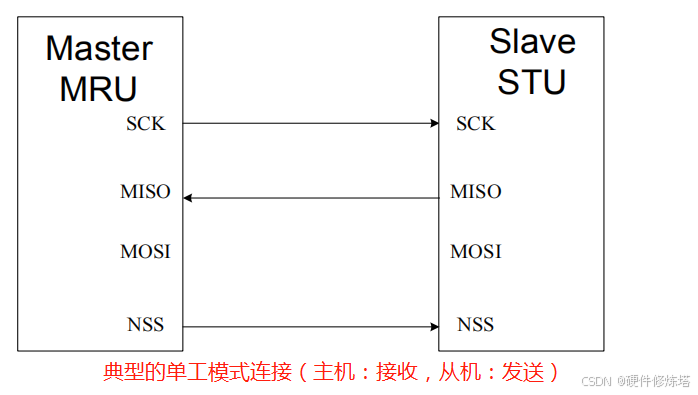

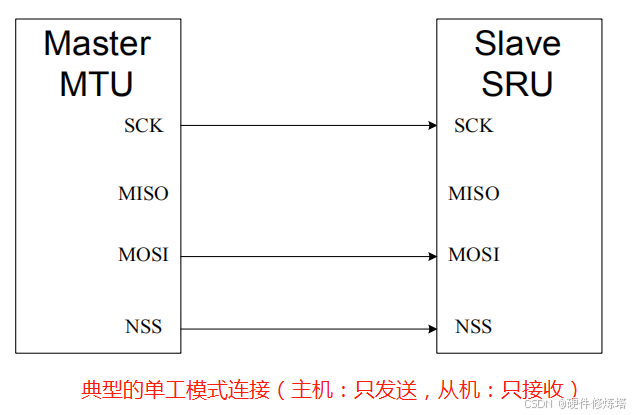

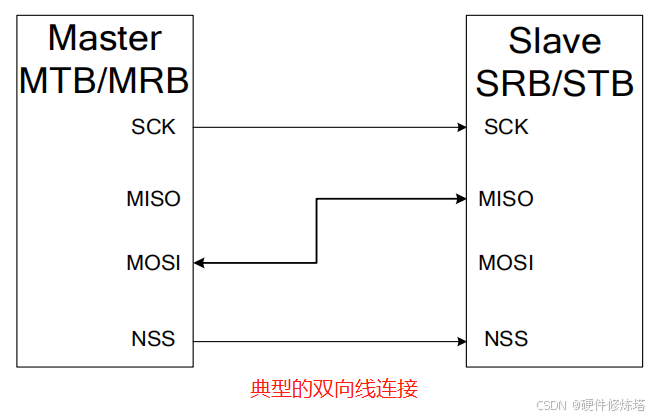

8. SPI典型工作模式

SPI有四种典型的工作模式:全双工模式,单工模式(主接收,从发送),单工模式(主发送,从接收),双向线模式。

全双工主机模式

简称主机属于MFD(Maximum Frame Duration 最大帧持续时间)模式,从机属于SFD(Start of Frame Delimiter帧起始分隔符)模式。如下图主机与从机的SCK,MIOS,MOSI,NSS四个引脚,一一对应连接。主机芯片的MOSI引脚表示主机发送,从机芯片的MOSI引脚表示从机接收。也就是说主机芯片MOSI引脚,我们看的是MO(Master Out)表示主机发送,从机芯片MOSI引脚,我们看的是SI(Slave Input)。

另外的其他几种工作模式与全双工模式类似,只需要搞清楚数据的收发流向正确,就好。

这里收集总结了一下SPI通信的优缺点:

一、优点

1). 高速数据传输

• SPI接口支持较高的时钟频率,数据传输速率通常可以达到几兆比特每秒(Mb/s),甚至更高。例如,在一些高性能的微控制器与外设通信中,SPI接口可以轻松实现10 Mb/s甚至50 Mb/s的数据传输速率。这种高速传输能力使其非常适合用于对实时性要求较高的应用场景,如高速数据采集系统、图像传感器数据传输等。

2). 全双工通信

• SPI接口支持全双工通信,即主机和从机可以同时发送和接收数据。这意味着在数据传输过程中,主机和从机可以高效地进行数据交互,而无需等待对方完成发送或接收操作。例如,在一些通信模块的应用中,主机可以通过SPI接口同时发送指令并接收从模块返回的状态信息,大大提高了通信效率。

3). 节省引脚资源

• SPI接口仅需四根线(SCLK、MOSI、MISO、CS)即可实现通信。相比其他一些通信协议(如并行通信),SPI接口大大减少了所需的引脚数量,这对于引脚资源有限的微控制器或系统芯片(SoC)来说是一个很大的优势。例如,在一些小型嵌入式设备中,微控制器的引脚数量可能非常有限,使用SPI接口可以有效节省引脚资源,为其他功能模块留出更多空间。

4). 硬件设计简单

• SPI接口的硬件设计相对简单,不需要复杂的电路支持。它不需要像其他一些通信协议(如USB)那样复杂的物理层电路,也不需要外部的时钟生成器或复杂的信号调理电路。这使得SPI接口在硬件设计和实现上更加容易,降低了硬件成本和设计难度。例如,在一些简单的传感器应用中,只需将传感器的SPI引脚与微控制器的对应引脚相连,并确保供电和地线连接正确即可实现通信。

5). 广泛支持和兼容性

• SPI接口得到了几乎所有主流微控制器和外设芯片厂商的广泛支持。无论是ARM Cortex系列微控制器、STM32系列,还是各种传感器、存储器、通信模块等外设芯片,几乎都提供了对SPI接口的支持。这种广泛的兼容性使得SPI接口在嵌入式系统中得到了广泛应用,开发人员可以轻松地找到支持SPI接口的芯片和模块,方便系统的设计和开发。

6). 可扩展性强

• SPI接口支持多从设备连接。通过添加额外的片选信号(CS),可以方便地将多个从设备连接到同一SPI总线上。这使得SPI接口在需要连接多个外设的系统中具有很强的可扩展性。例如,在一个复杂的嵌入式系统中,可能需要连接多个传感器、存储器和通信模块,使用SPI接口可以通过简单的片选信号扩展来实现这些设备的连接和通信。

二、缺点

1). 无应答机制

• SPI接口本身没有内置的应答机制。在数据传输过程中,主机无法直接确认从机是否正确接收到了数据,也无法判断从机是否已经准备好发送数据。这可能导致数据传输的可靠性降低,特别是在通信环境较差或从机出现故障的情况下。例如,在一些长距离通信或高噪声环境的应用中,数据传输可能会受到干扰,而SPI接口无法自动检测和纠正这些错误。

2). 单主设备限制

• 传统SPI接口仅支持单主设备。在一个SPI总线中,只能有一个设备作为主机,其他设备都必须作为从机。这限制了SPI接口在一些需要多主设备通信的场景中的应用。例如,在一些分布式系统中,可能需要多个设备作为主机与从设备进行通信,这种情况下SPI接口就无法满足需求。

3). 通信距离有限

• 由于SPI接口是一种高速同步串行通信协议,其通信距离相对较短。一般来说,SPI接口的通信距离通常不超过几米。这是因为高速信号在传输过程中容易受到电磁干扰和信号衰减的影响,导致数据传输错误。在一些需要长距离通信的应用中,如工业自动化中的远程传感器网络,SPI接口可能无法直接满足需求,需要通过额外的信号调理或中继设备来延长通信距离。

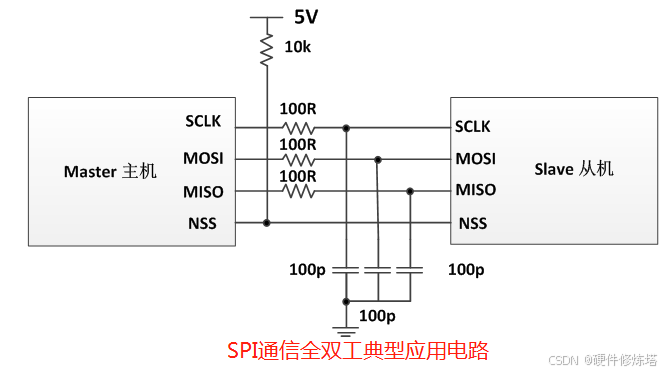

4). 总线负载能力有限

• SPI接口的总线负载能力相对有限。随着连接到SPI总线上的从设备数量增加,总线的负载会逐渐增大,这可能导致信号完整性问题,如信号反射、串扰等。这些问题会影响数据传输的可靠性,甚至导致通信失败。因此,在设计SPI总线系统时,需要合理控制从设备的数量,并采取适当的信号完整性措施,如添加终端电阻、优化布线等。以下是SIP通信典型全双工应用电路,SCLK、MOSI、MISO条根信号线增加RC滤波电路,可以对外界干扰有一定的抵抗能力。若两芯片的距离很近,PCBA空间和成本有要求,那么RC滤波电路可以省掉,两芯片引脚直接连接便可。

本博客持续更新中,欢迎大家收藏与关注,谢谢!

911

911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?