目录

6.2 DMA中断状态清除寄存器:DMA_LIFCR和DMA_HIFCR

6.6 DMA数据流x的存储器地址寄存器:DMA_SxMOAR和DMA_SxM1AR

1. 什么是DMA

DMA全称为:Direct Memory Access;即直接存储器访问。

DMA传输数据就是从地址A复制到地址B,地址A和地址B可以是外设和存储器之间,也可以是存储器和存储器之间。

单片机的核心是CPU,我们知道CPU无时无刻不在处理着大量的事务,其中包括转移数据、计算数据、控制程序转移等等。正如中断一样,CPU处理的事务也有轻重缓急之分,有些事情对于CPU来说并不是那么重要,比方说转移数据、存储数据、复制数据,如果通过其他功能去处理这些事,而让原本应该处理这些事件的CPU转而去处理更加重要、复杂的事务,是不是可以更好的利用CPU资源呢?

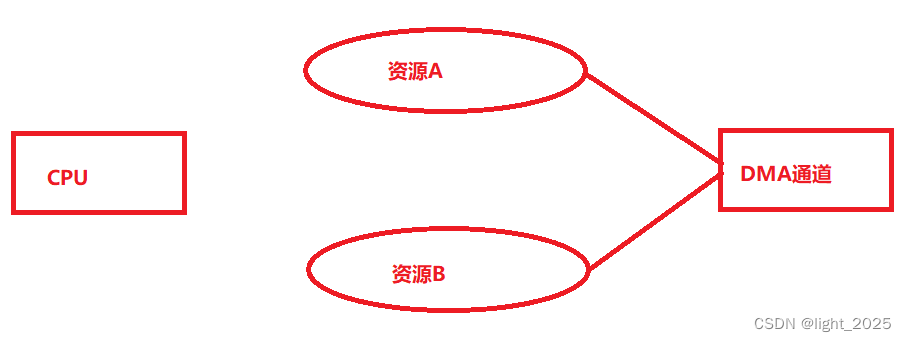

DMA就是基于这种设想而设计的,转移数据(特别是大量的数据费时费力)是可以不用CPU参与的,这部分CPU转而去处理更加复杂重要的事务,可以大大的增强CPU资源利用率。比方说我们希望资源 A 的数据复制到资源 B,是可以不用CPU参与的,只需要在资源 A 和资源 B 之间开辟一个DMA通道来复制数据即可。CPU可以转而去处理更加重要的事务。

DMA的作用就是为了解决大量数据转移过度消耗CPU资源的问题。有了DMA使得CPU更专注于更加重要实用的操作、计算、控制等。

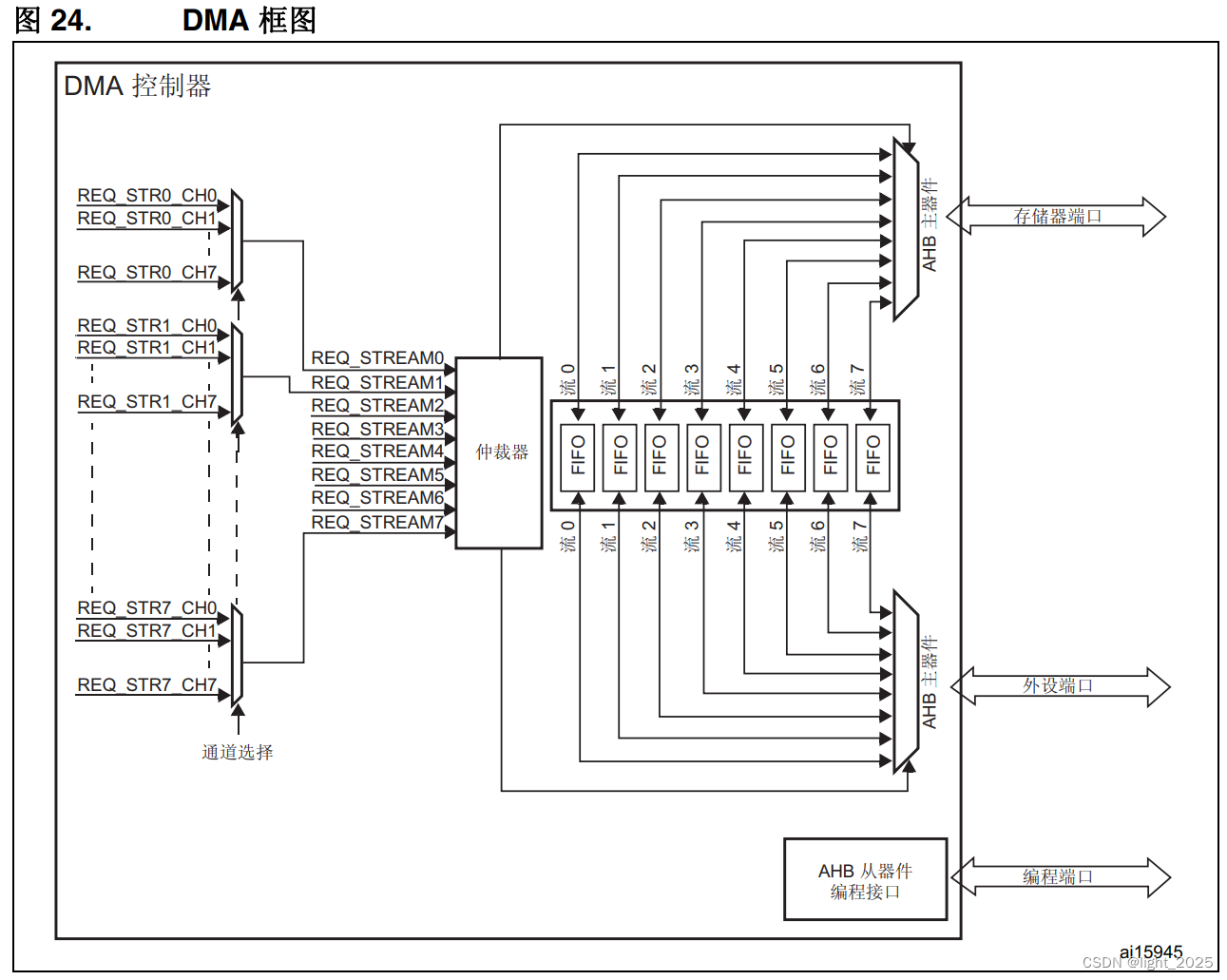

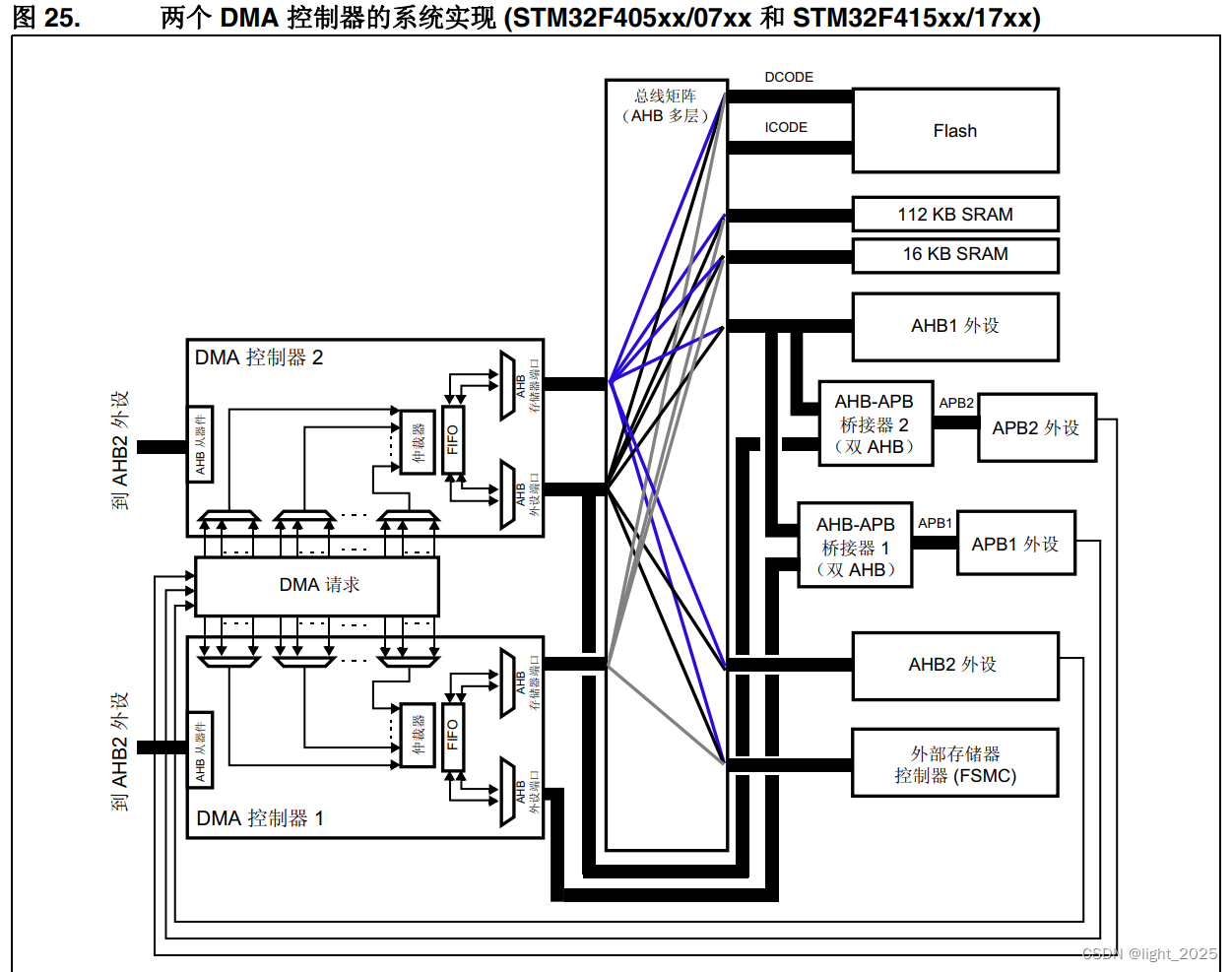

DMA控制器基于复杂的总线矩阵架构,将功能强大的双 AHB 主总线架构与独立的 FIFO 结合在一起,优化了系统带宽。两个DMA控制器总共有16个数据流(每个控制器8个),每一个DMA控制器都用于管理一个或多个外设的存储器访问请求。每个数据流总共可以有多达8个通道(或称请求)。每个通道都有一个仲裁器,用于处理DMA请求间的优先级(类似于中断中的NVIC)。

2. DMA的主要特性

- 双 AHB 主总线架构,一个用于存储器访问,另一个用于外设访问

- 仅支持 32 位访问的 AHB 从编程接口

- 每个DMA控制器有8个数据流,每个数据流有多达8个通道(或称请求)

- 每个数据流有单独的四级 32 位先进先出存储器缓冲区 (FIFO),可用于 FIFO 模式或直接模式

- 通过硬件可以将每个数据流配置为:

- —支持外设到存储器、存储器到外设和存储器到存储器传输的常规通道

- —也支持在存储器方双缓冲的双缓冲区通道

- 8 个数据流中的每一个都连接到专用硬件 DMA 通道(请求)

- DMA 数据流请求之间的优先级可用软件编程(4 个级别:非常高、高、中、低),在软件优先级相同的情况下可以通过硬件决定优先级(例如,请求 0 的优先级高于请求 1)

- 每个数据流也支持通过软件触发存储器到存储器的传输

3. DMA功能

3.1 DMA功能框图

DMA控制器执行直接存储器传输:采用AHB主总线,它可以控制AHB总线矩阵来启动AHB事务;

直接存储器执行的事务包括:外设到存储器的传输、存储器到外设的传输、存储器到存储器的传输。

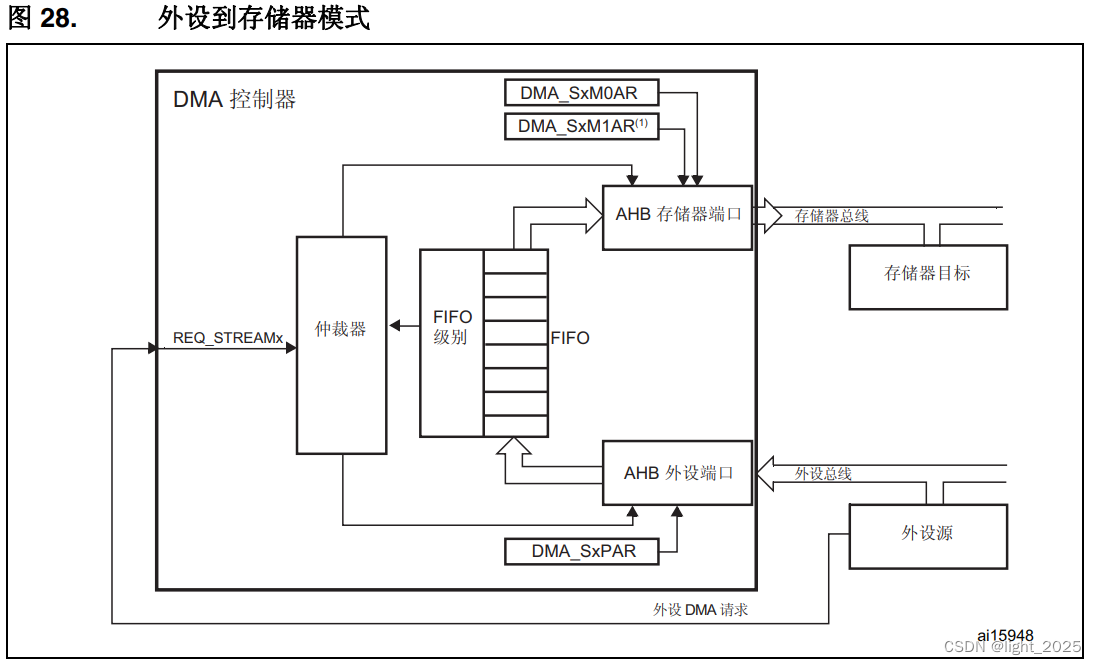

DMA控制器提供两个AHB主端口:AHB存储器端口(用于连接存储器)和 AHB外设端口(用于连接外设)。但是需要注意:当执行存储器与存储器之间的传输时,AHB外设端口必须也可以访问存储器。

3.2 DMA事务

DMA事务由给定数目的数据传输序列组成。要传输的数据项的数目及其宽度(8位、16位 或 32位)可由软件编程。

每个DMA传输包含三项操作:

- 通过 DMA_SxPAR 或 DMA_SxM0AR 寄存器寻址,从外设数据寄存器或存储器单元中加载数据。

- 通过 DMA_SxPAR 或 DMA_SxM0AR 寄存器寻址,将加载的数据存储到外设数据寄存器或存储器单元。

- DMA_SxNDTR 计数器在数据存储结束后递减,该计数器中包含仍需执行的事务数。

在产生事件后,外设会向DMA控制器发送请求信号。DMA控制器根据通道优先级处理该请求。只要DMA控制器访问外设,DMA控制器就会向外设发送确认信号。外设获得DMA控制器的确认信号后,便会立即释放其请求。一旦外设使请求变得失效,那么DMA控制器就会释放确认信号。如果有更多的请求,外设可以启动下一个事务。

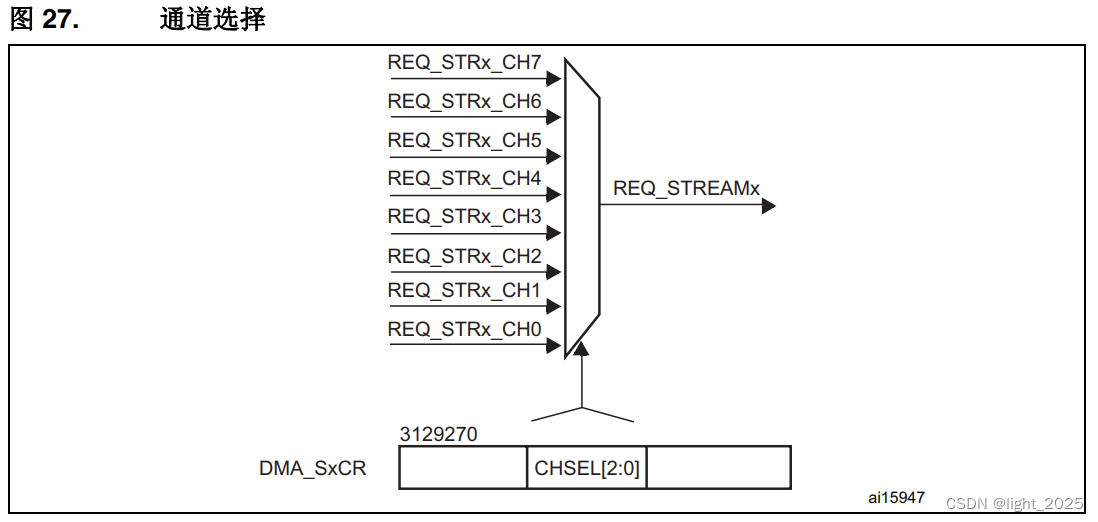

3.3 通道选择

每一个数据流都与一个DMA请求相关联,此DMA请求可以从8个可能的通道请求中选出。此选择由DMA_SxCR寄存器中的CHSEL[2:0]位控制。

3.4 仲裁器

仲裁器为两个AHB主端口(存储器和外设端口)提供基于请求优先级的 8 个DMA数据流请求管理,并启动 外设/存储器 访问序列。

优先级管理分为两个阶段:

- 软件:每个数据流优先级都可以在DMA_SxCR寄存器中配置。分为:非常高优先级、高优先级、中优先级、低优先级。

- 硬件:如果两个请求具有相同的软件优先级,则编号低的数据流优先于编号高的数据流。例如:数据流 2 的优先级高于数据流 4 的优先级。

3.5 DMA数据流

8个DMA控制器数据流都能提供源和目标(传输的双方)之间的单向传输链路。

每个数据流配置后都可以执行:

- 常规类型事务:存储器到外设、外设到存储器或存储器到存储器的传输。

- 双缓冲区类型事务:使用存储器的两个存储器指针的双缓冲区传输。

3.6 源、目标和传输模式

源传输和目标传输在整个 4GB 区域(也就是地址在0x0000 0000和0xFFFF FFFF之间)都可以寻址外设和存储器。

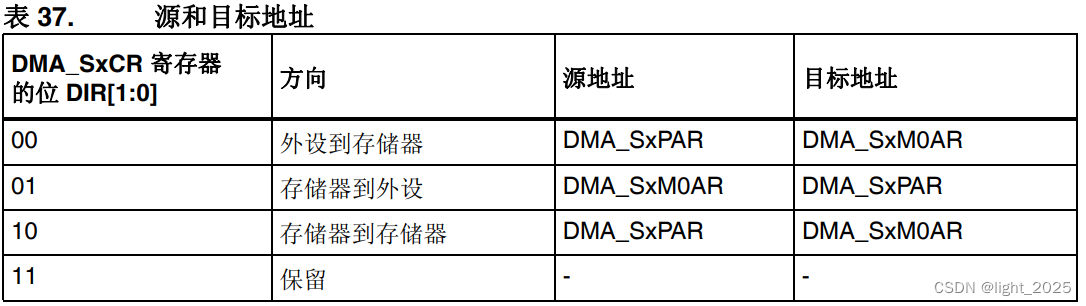

传输方向使用的是DMA_SxCR寄存器中的DIR[1:0]位进行配置,有三种可能的传输方向:存储器到外设、外设到存储器或存储器到存储器。

3.6.1 外设到存储器模式

使能了这个模式(将DMA_SxCR寄存器中的位EN置1)时,每次产生外设请求,数据流都会启动数据源到FIFO的传输。

FIFO简介:

FIFO用于在源数据传输到目标之前临时存储这些数据。

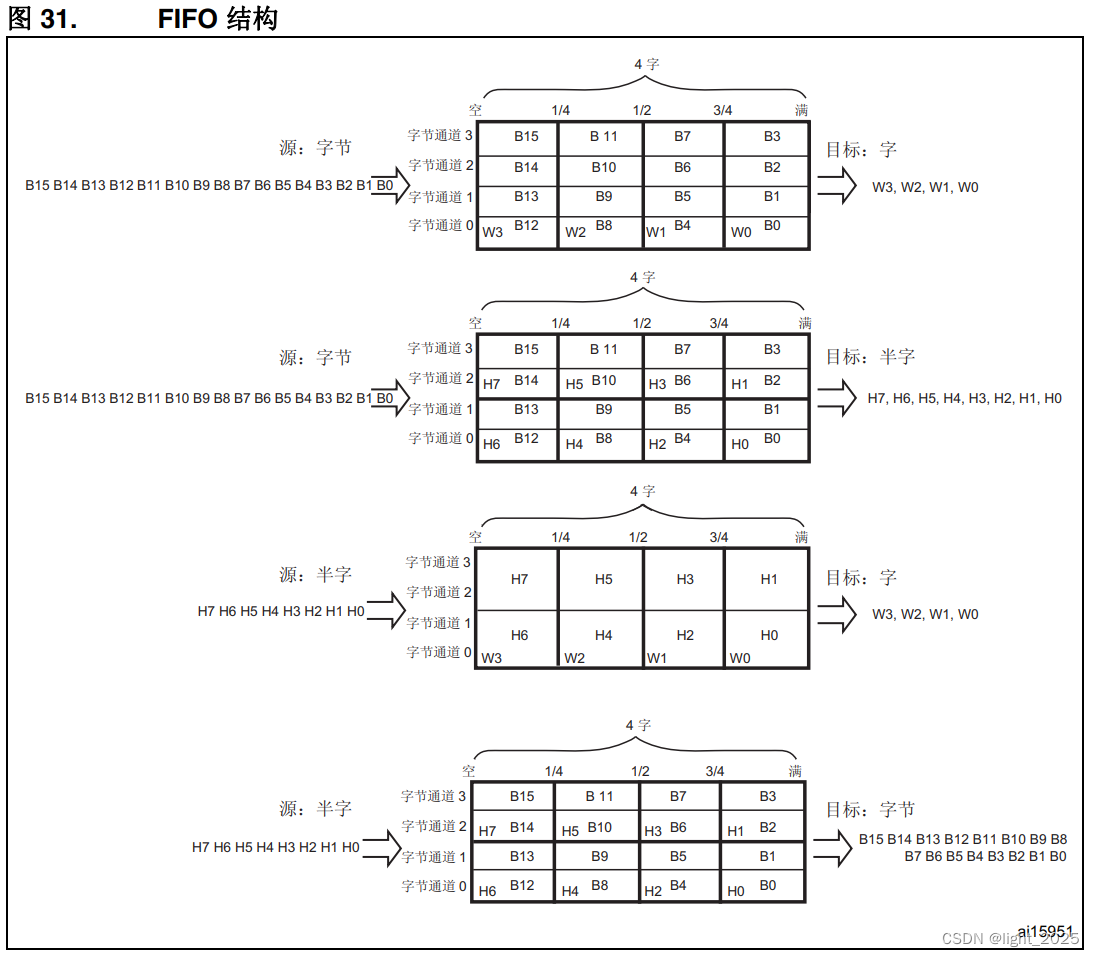

每个数据流都有一个独立的4字FIFO,阈值级别可由软件配置为1/4、1/2、3/4或满。为了使能FIFO阈值级别,必须通过将DMA_SxFCR寄存器中的DMDIS位置1来禁止直接模式。FIFO的结构随源与目标数据宽度而不同。

当达到了FIFO(源数据传输到目标之前临时存储)的阈值级别时,FIFO的内容移出并存储到目标中。

如果 DMA_SxNDTR 寄存器达到零、外设请求传输终止(在使用外设流控制器的情况下)或 DMA_SxCR 寄存器中的 EN 位由软件清零,传输即会停止。

在直接模式下(当 DMA_SxFCR 寄存器中的 DMDIS 值为“0”时),不使用 FIFO 的阈值级别控制:每完成一次从外设到 FIFO 的数据传输后,相应的数据立即就会移出并存储到目标中。

3.6.2 存储器到外设模式

使能了这种模式(将DMA_SxCR寄存器中的EN位置1)时,数据流会立即启动传输,从源完全填充FIFO。

每次发生外设请求,FIFO的内容都会移出并存储到目标中。当FIFO的级别小于或等于预定义的阈值级别时,将使用存储器中的数据完全重载FIFO。

如果 DMA_SxNDTR 寄存器达到零、外设请求传输终止(在使用外设流控制器的情况下)或 DMA_SxCR 寄存器中的 EN 位由软件清零,传输即会停止。

文章详细介绍了STM32中的DMA(直接存储器访问)机制,包括DMA的工作原理、主要特性、功能、中断处理、寄存器配置以及如何通过库函数进行初始化和配置。重点讨论了DMA在数据传输中的作用,如外设到存储器、存储器到外设和存储器到存储器的模式,以及如何通过配置DMA控制器优化系统资源利用率。

文章详细介绍了STM32中的DMA(直接存储器访问)机制,包括DMA的工作原理、主要特性、功能、中断处理、寄存器配置以及如何通过库函数进行初始化和配置。重点讨论了DMA在数据传输中的作用,如外设到存储器、存储器到外设和存储器到存储器的模式,以及如何通过配置DMA控制器优化系统资源利用率。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

911

911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?