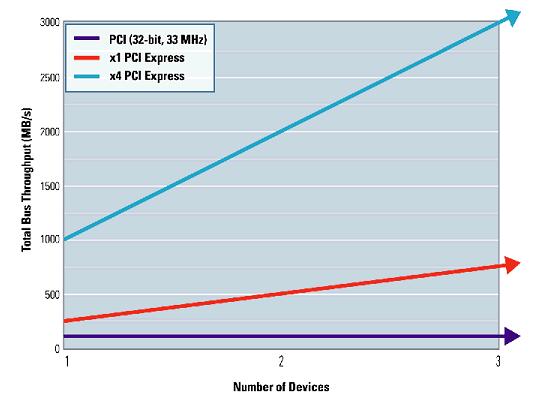

The PCI bus gained adoption as a mainstream computer bus in the mid-1990s. The most common implementation of the PCI bus operates at 33 MHz and 32 bits with a peak theoretical bandwidth of 132 MB/s and is the implementation in the majority of PXI systems. It uses a shared bus topology, where bus bandwidth is divided among multiple devices, to enable communication among the different devices on the bus. Over time, some devices have become more bandwidth-hungry. As a result, PCI Express was created to overcome the limitations due to these bandwidth-hungry devices starving other devices on the same shared bus.

The most notable PCI Express advancement over PCI is its point-to-point bus topology. The shared bus used for PCI is replaced with a shared switch, which gives each device its own direct access to the bus. Unlike PCI, which divides bandwidth between all devices on the bus, PCI Express provides each device with its own dedicated data pipeline. Data is sent serially in packets through pairs of transmit-and-receive signals called lanes, which enable 250 MB/s bandwidth per direction, per lane for PCI Express 1.0. Multiple lanes can be grouped together into x1 (“by one”), x2, x4, x8, x12, and x16 lane widths to increase bandwidth to the slot and achieve up to 4 GB/s total throughput. Since the introduction of PCI Express, the standard has evolved to allow faster data rates while maintaining backward compatibility. For instance, PCI Express 2.0 doubles the per-lane bandwidth from 250 to 500 MB/s per direction.

从1990年代中期开始,PCI总线成为主流计算机总线标准。随着设备带宽需求的增长,共享总线架构限制了系统性能。为解决这一问题,引入了PCI Express(PCIe),采用了点对点总线拓扑,为每个设备提供专用的数据通道,显著提高了带宽并克服了共享总线的局限性。

从1990年代中期开始,PCI总线成为主流计算机总线标准。随着设备带宽需求的增长,共享总线架构限制了系统性能。为解决这一问题,引入了PCI Express(PCIe),采用了点对点总线拓扑,为每个设备提供专用的数据通道,显著提高了带宽并克服了共享总线的局限性。

3378

3378

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?