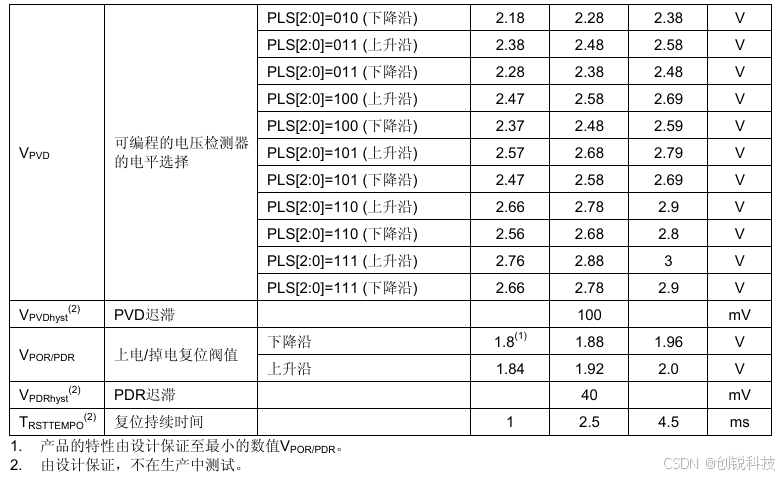

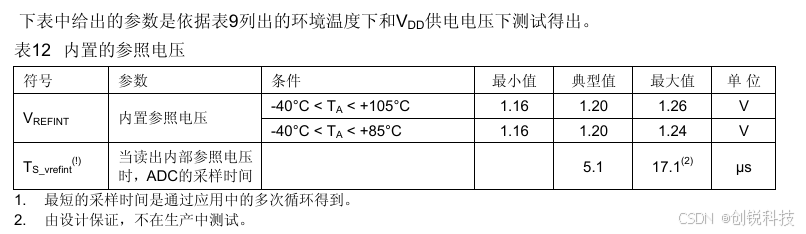

5.3.4 内置的参照电压

5.3.4 内置的参照电压 5.3.5 供电电流特性 电流消耗是多种参数和因素的综合指标,这些参数和因素包括工作电压、环境温度、I/O引脚的负载、 产品的软件配置、工作频率、I/O脚的翻转速率、程序在存储器中的位置以及执行的代码等。 电流消耗的测量方法说明,详见图13。

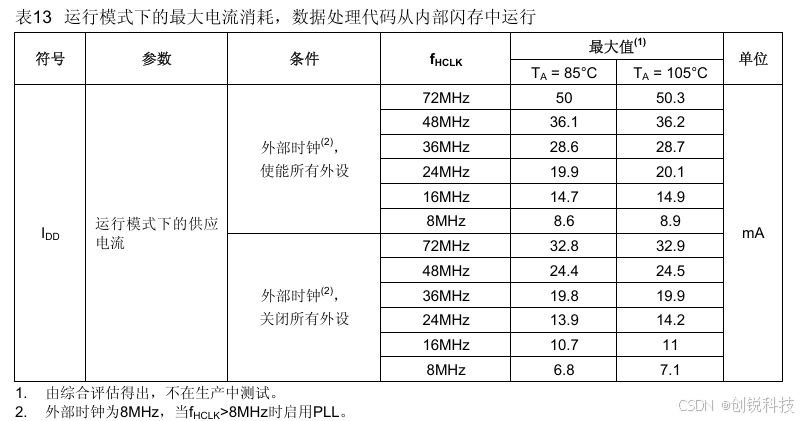

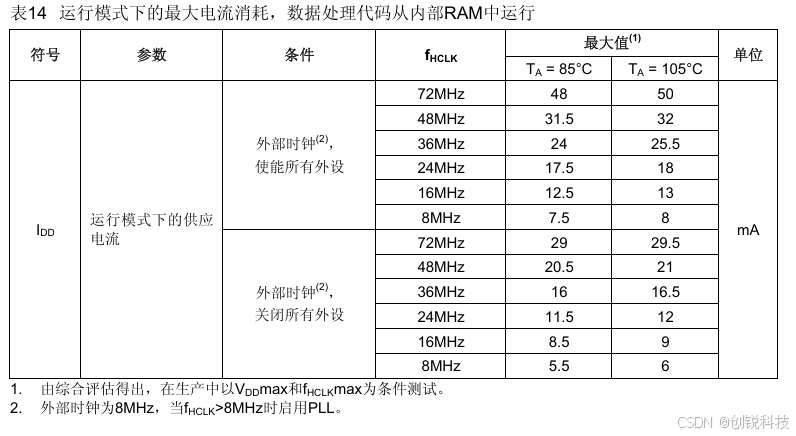

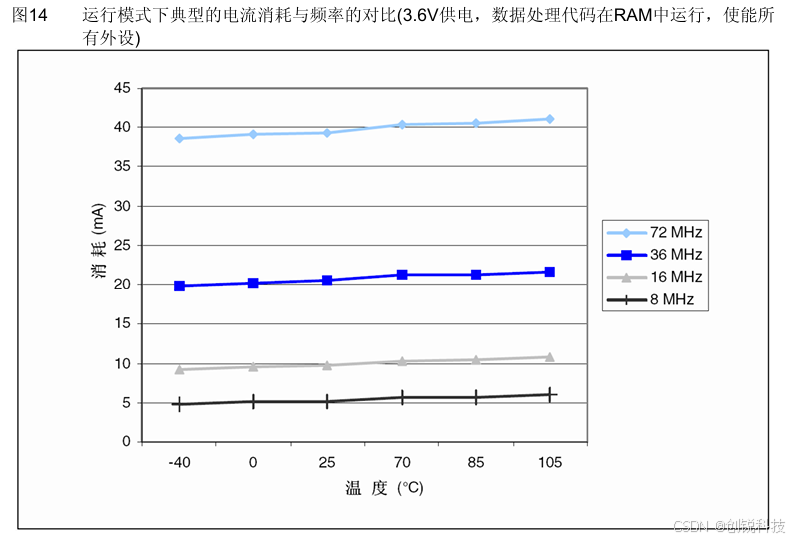

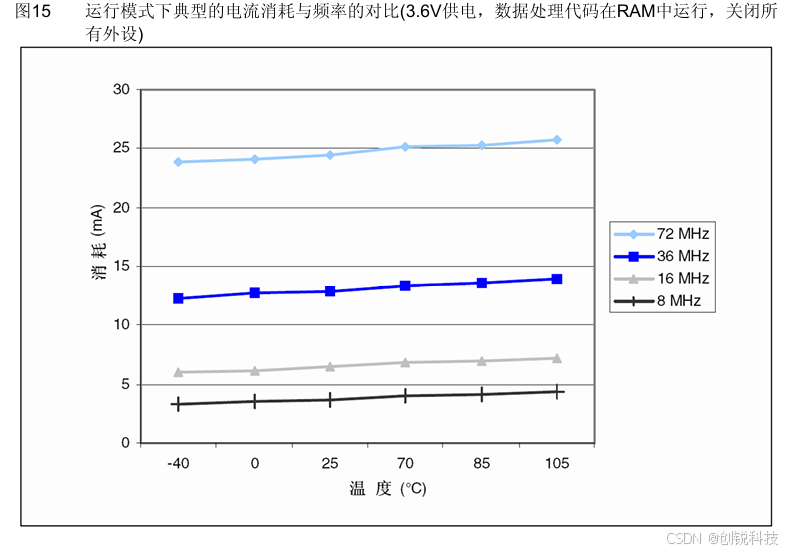

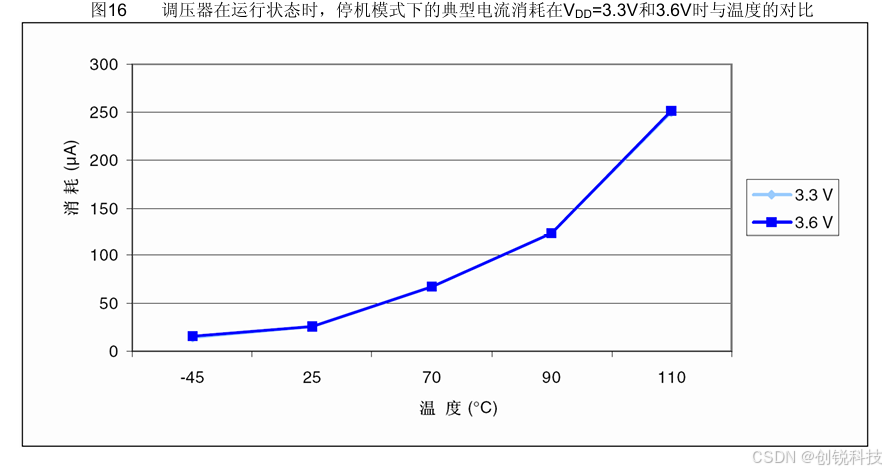

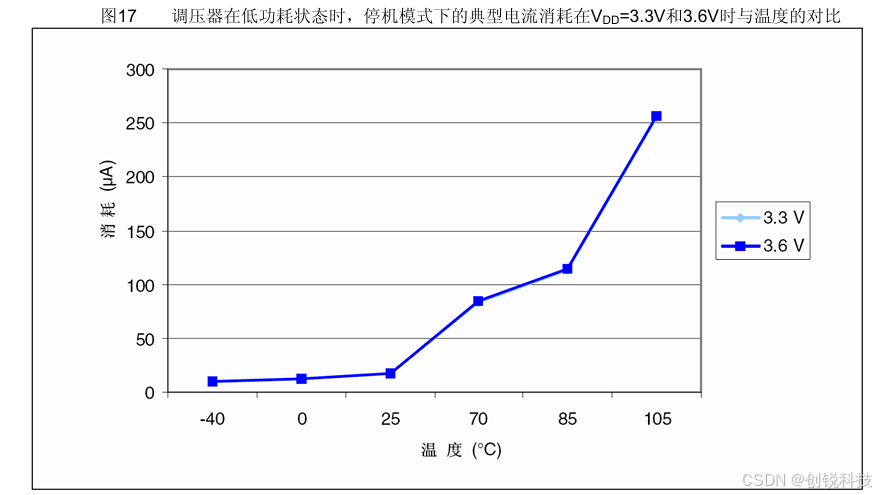

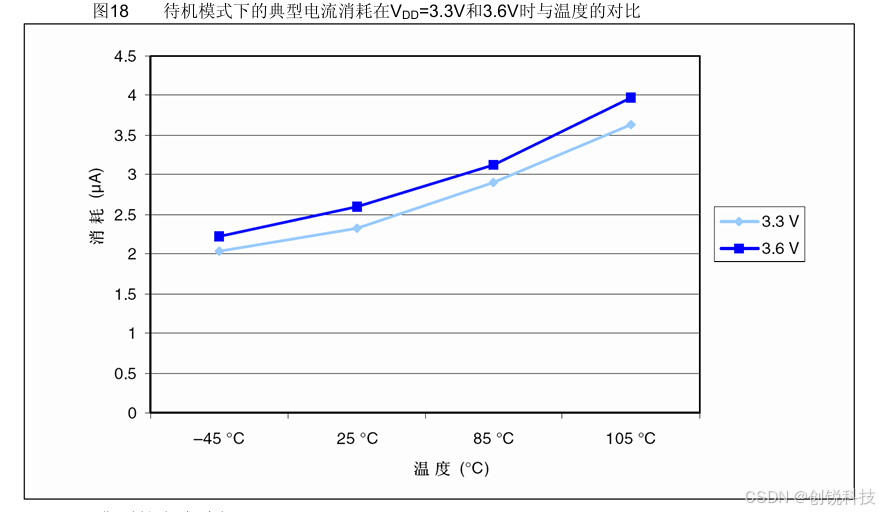

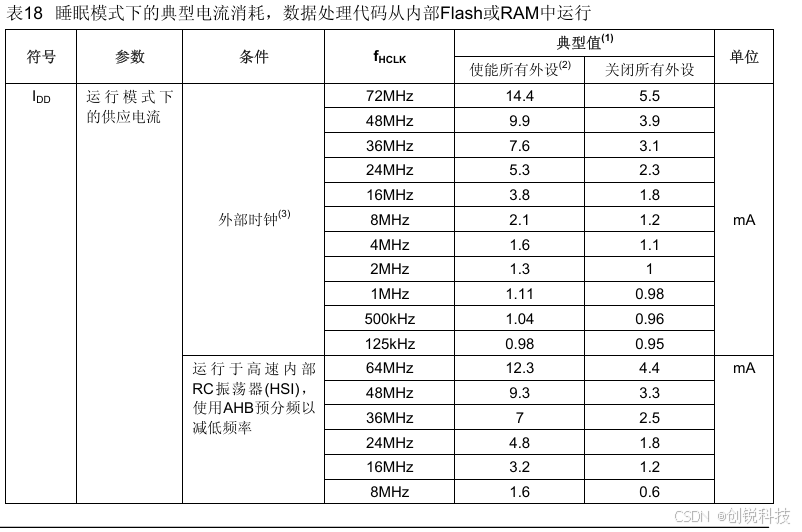

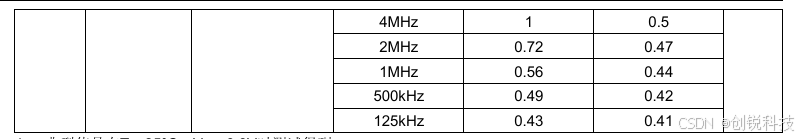

5.3.5 供电电流特性 电流消耗是多种参数和因素的综合指标,这些参数和因素包括工作电压、环境温度、I/O引脚的负载、 产品的软件配置、工作频率、I/O脚的翻转速率、程序在存储器中的位置以及执行的代码等。 电流消耗的测量方法说明,详见图13。

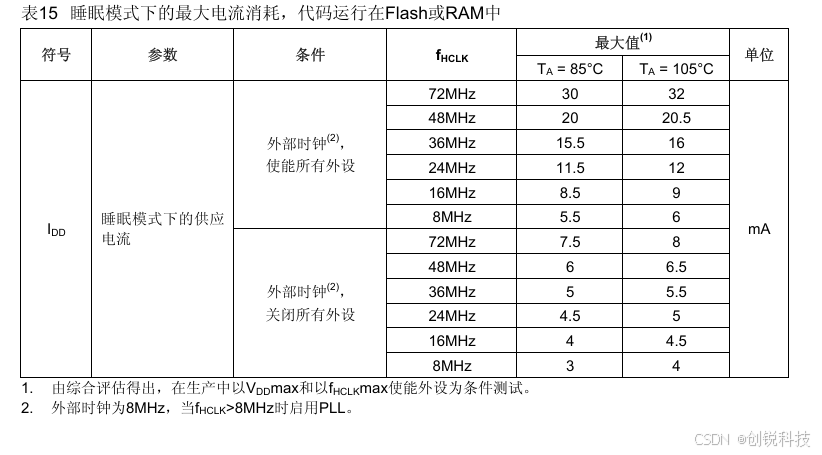

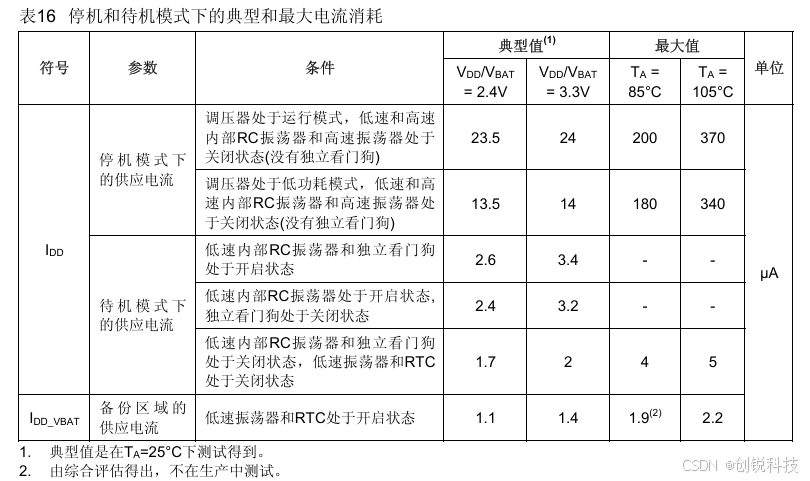

本节中给出的所有运行模式下的电流消耗测量值,都是在执行一套精简的代码,能够得到Dhrystone 2.1代码等效的结果。 最大电流消耗 微控制器处于下列条件:

● 所有的I/O引脚都处于输入模式,并连接到一个静态电平上——VDD或VSS(无负载)。

● 所有的外设都处于关闭状态,除非特别说明。

● 闪存存储器的访问时间调整到fHCLK的频率(0~24MHz时为0个等待周期,24~48MHz时为1个等 待周期,超过48MHz时为2个等待周期)。

● 指令预取功能开启(提示:这个参数必须在设置时钟和总线分频之前设置)。

● 当开启外设时:fPCLK1 = fHCLK/2,fPCLK2 = fHCLK。

表13、表14和表15中给出的参数,是依据表9列出的环境温度下和VDD供电电压下测试得出。

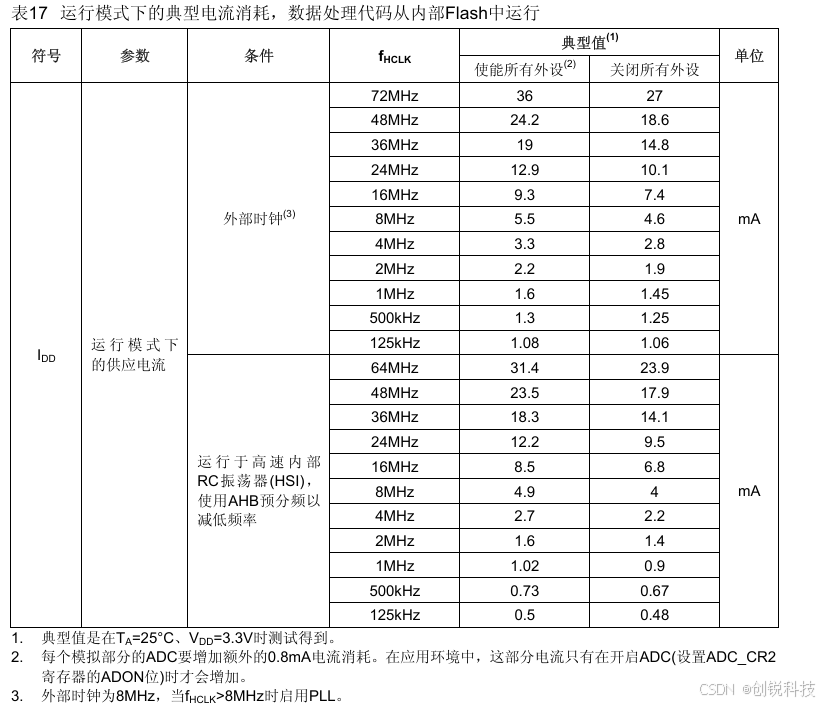

典型的电流消耗 MCU处于下述条件下:

典型的电流消耗 MCU处于下述条件下:

● 所有的I/O引脚都处于输入模式,并连接到一个静态电平上——VDD或VSS(无负载)。

● 所有的外设都处于关闭状态,除非特别说明。

● 闪存存储器的访问时间调整到fHCLK的频率(0~24MHz时为0个等待周期,24~48MHz时为1个等 待周期,超过48MHz时为2个等待周期)。

● 环境温度和VDD供电电压条件列于表9。

● 指令预取功能开启(提示:这个参数必须在设置时钟和总线分频之前设置)。当开启外设时:fPCLK1 = fHCLK/4,fPCLK2 = fHCLK/2,fADCCLK = fPCLK2/4。

1. 典型值是在TA=25°C、VDD=3.3V时测试得到。

2. 每个模拟部分的ADC要增加额外的0.8mA电流消耗。在应用环境中,这部分电流只有在开启ADC(设置ADC_CR2 寄存器的ADON位)时才会增加。

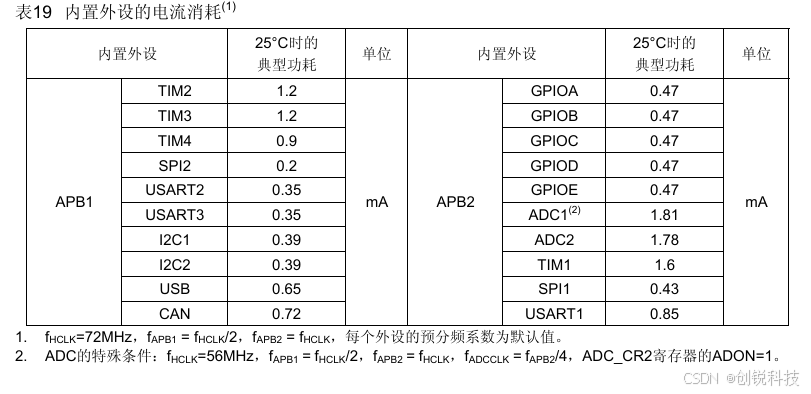

3. 外部时钟为8MHz,当fHCLK>8MHz时启用PLL。 内置外设电流消耗 内置外设的电流消耗列于表19,MCU的工作条件如下:

● 所有的I/O引脚都处于输入模式,并连接到一个静态电平上——VDD或VSS(无负载)。

● 所有的外设都处于关闭状态,除非特别说明。

● 给出的数值是通过测量电流消耗计算得出 − 关闭所有外设的时钟 − 只开启一个外设的时钟

● 环境温度和VDD供电电压条件列于表19。

363

363

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?