前言

AXI4是ARM公司推出的第四代AMBA总线协议,专为高带宽、低延迟的片上通信设计,广泛应用于FPGA、处理器及DSP等复杂系统,AXI4包含三中形态,分别为

- AXI4:标准版本,支持高带宽内存映射通信。

- AXI4-Lite:简化版,用于寄存器等简单设备的轻量级访问。

- AXI4-Stream:无地址协议,适用于高速数据流传输(如视频、音频)。

本文章主要介绍AXI4协议的代码实现

一、AXI4结构

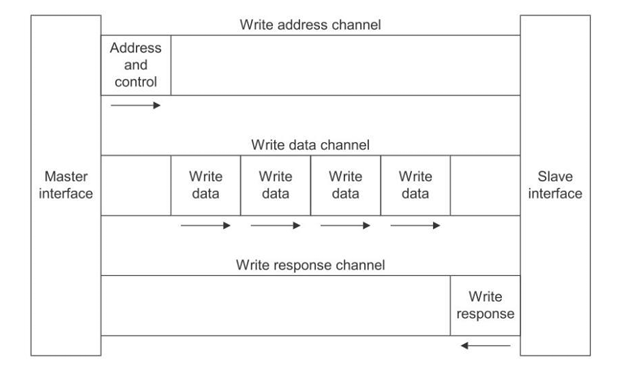

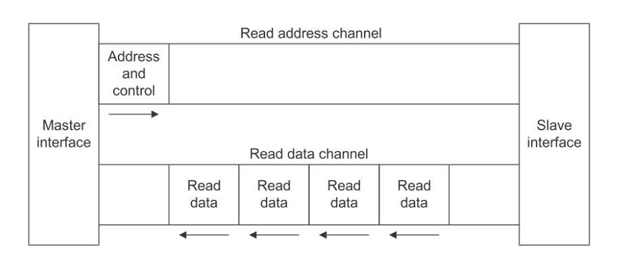

AXI4主要有五个事务(通道)组成,分别为写地址通道、写数据通道、写响应通道、读地址通道、读数据通道;其中读响应通道包含于读数通道,通道传输流程如下:

通道解释:

- 这5条独立的通道都包含一个双路的VALD、READY握手机制。信息源通过VALID信号来指示通道中的数据和控制信息什么时候有效。目地源用READY信号来表示何时准备好接收数据。传输地址信息和数据都是在VALID和READY同时为高时有效。

- 读数据和写数据通道都包括一个 LAST 信号,用来指明一个事物传输的最后一个数据。

- 读/写事务都有自己的地址通道,地址通道携带着传输事务所必须的地址和信息。

- 读数据通道传送着从设备到主机的读数据和读响应信息。读响应信息指明读事务的完成状态。

- 写数据通路传送着主机向设备的写数据和写控制信息。写响应通道提供了设备响应写事务的一种方式。在每一次突发式写会产生一个完成信号。

二、AXI4各通道定义

1. 写地址通道定义

2. 写数据通道定义

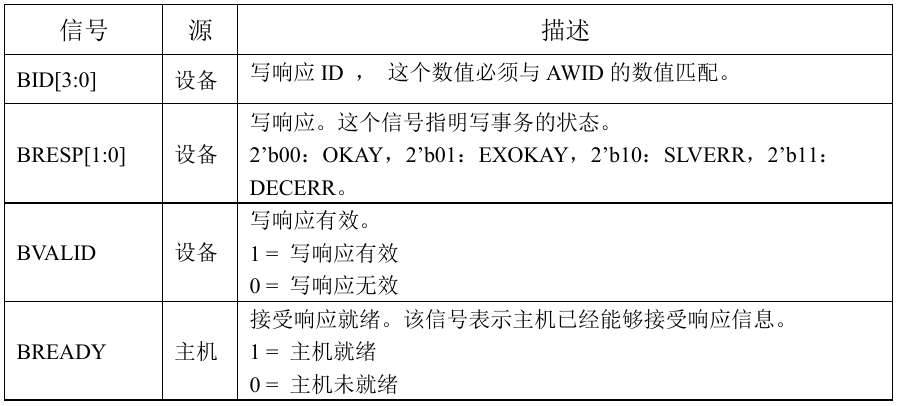

3. 写响应通道定义

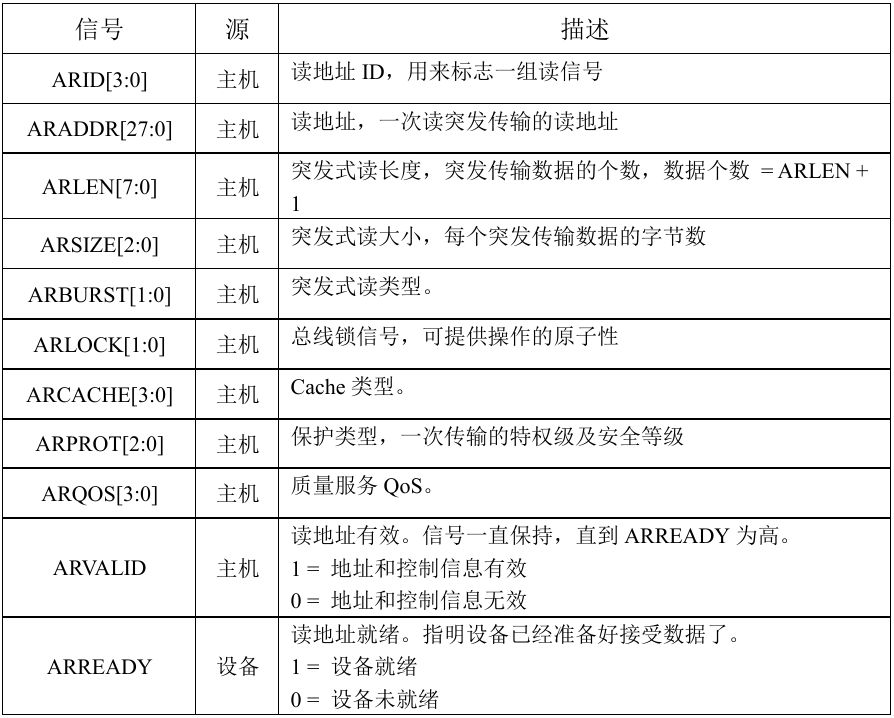

4. 读地址通道定义

5. 读数据通道定义

二、代码设计

1.思维导图

上述图片为代码状态机的流程图

2.代码设计

module axi_ram #

(

parameter WADDR_BASE = 28'h0 ,

parameter WADDR_BEND = 28'h0 ,

parameter RADDR_BASE = 28'h0 ,

parameter RADDR_BEND = 28'h0 ,

parameter AXI_ID = 4'd0 ,

parameter AXI_LEN = 8'd31 ,

parameter DWID = 128 ,

parameter ADDR = 28

)

(

input clk_sys ,

input rst_sys ,

// DDR INIT

input mmcm_locked ,

input init_calib_complete ,

// Slave Interface Write Address Ports

output [3:0] m_axi_

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7329

7329

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?