目录

1 时序逻辑与组合逻辑的区别

组合逻辑的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原本的状态无关,逻辑中不牵涉跳变沿信号的处理,组合逻辑的verilog描述方式有两种:

(1):always @(电平敏感信号列表)

always模块的敏感列表为所有判断条件信号和输入信号,但一定要注意敏感列表的完整性。在always 模块中可以使用if、case 和for 等各种RTL 关键字结构。由于赋值语句有阻塞赋值和非阻塞赋值两类,建议读者使用阻塞赋值语句“=”。always 模块中的信号必须定义为reg 型,不过最终的实现结果中并没有寄存器。这是由于在组合逻辑电路描述中,将信号定义为reg型,只是为了满足语法要求。

(2):assign描述的赋值语句。

信号只能被定义为wire型。

时序逻辑是Verilog HDL 设计中另一类重要应用,其特点为任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关。电路里面有存储元件(各类触发器,在FPGA 芯片结构中只有D 触发器)用于记忆信息,从电路行为上讲,不管输入如何变化,仅当时钟的沿(上升沿或下降沿)到达时,才有可能使输出发生变化。

与组合逻辑不同的是:

(1)在描述时序电路的always块中的reg型信号都会被综合成寄存器,这是和组合逻辑电路所不同的。

(2)时序逻辑中推荐使用非阻塞赋值“<=”。

(3)时序逻辑的敏感信号列表只需要加入所用的时钟触发沿即可,其余所有的输入和条件判断信号都不用加入,这是因为时序逻辑是通过时钟信号的跳变沿来控制的。

2 建立与保持时间

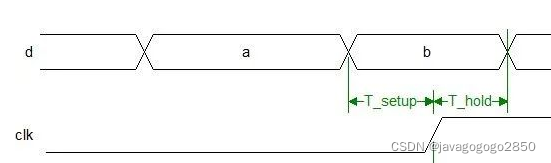

建立时间(Tsu:set up time)

是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。

保持时间(Th:hold time)

是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。

3 亚稳态

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个 正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

亚稳态产生概率:

概率 = (建立时间 + 保持时间)/ 采集时钟周期

可以看出,亚稳态出现的概率与工作时钟频率以及触发器自身的特性(器件的工艺等因素决定了它的建立/保持时间)有关;所以在异步信号采集过程中,要想减少亚稳态发生的概率可以:

1、降低系统工作时钟,增大系统周期,亚稳态概率就会减小(降低工作频率,不常用);

2、 采用工艺更好的FPGA,也就是Tsu和Th时间较小的FPGA器件;

解决

降低系统时钟(不常见,因为高速率正确处理才是目的)

用反应更快的触发器(工艺相关,受硬件制约)

引入同步机制,防止亚稳态传播(常见的处理方式,即通过一些机制,在现有硬件条件下,最大程度的减少亚稳态发生)

<

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1416

1416

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?