这里以Quartus免费版举例

1. 项目建立:

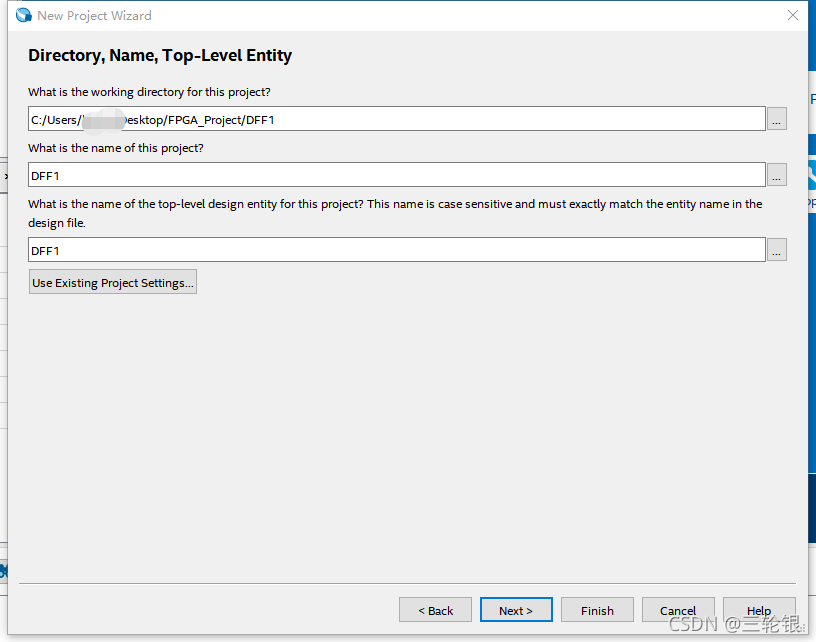

- 打开Quartus,从【File=>NewProjectWizard】新建一个项目。

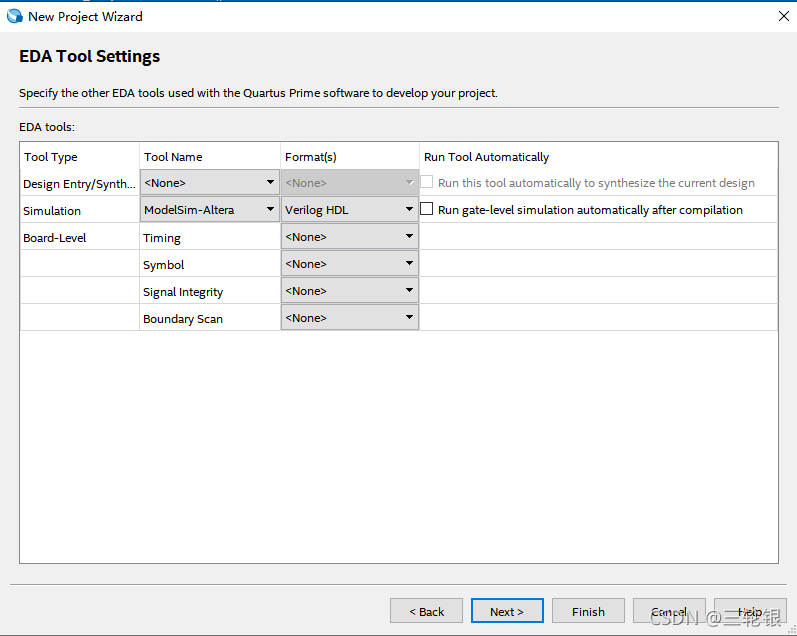

- 给项目设立文件夹,命名,并且选择Simulation为‘ModelSim—Altera’,‘Verilog’

- Finish结束(因为我没有打算烧板子,其他就不选)

2. 编写Verilog设计文件:

1.从【File=>New】新建一个文件,选择【Design Files=>Verilog HDL File】新建v文件。

2. 开始编写Verilog。(代码引用来自: link)

module dff(clk,clr,rst,d,q);//clr清0,rst复位

input clk,clr,rst,d;

output q;

reg q;

always@(posedge clk or posedge clr)

begin

if(clr==1'b1)q<=1'b0;

else if(rst==1'b1)q<

本文详细介绍了如何利用Quartus免费版建立Verilog项目,编写DFF模块,以及通过SimulationWaveformEditor和Modelsim(Testbench)进行仿真操作。在Quartus中创建新项目,编写Verilog代码实现DFF,然后通过设置和运行仿真脚本来观察波形,验证设计功能。

本文详细介绍了如何利用Quartus免费版建立Verilog项目,编写DFF模块,以及通过SimulationWaveformEditor和Modelsim(Testbench)进行仿真操作。在Quartus中创建新项目,编写Verilog代码实现DFF,然后通过设置和运行仿真脚本来观察波形,验证设计功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1464

1464

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?