MCU存储体系

1.SRAM

2.FLASH

3.TCM

SRAM

SRAM(Static Random-Access Memory):静态随机存取存储器.

特点:访问速度快、断电丢失、不

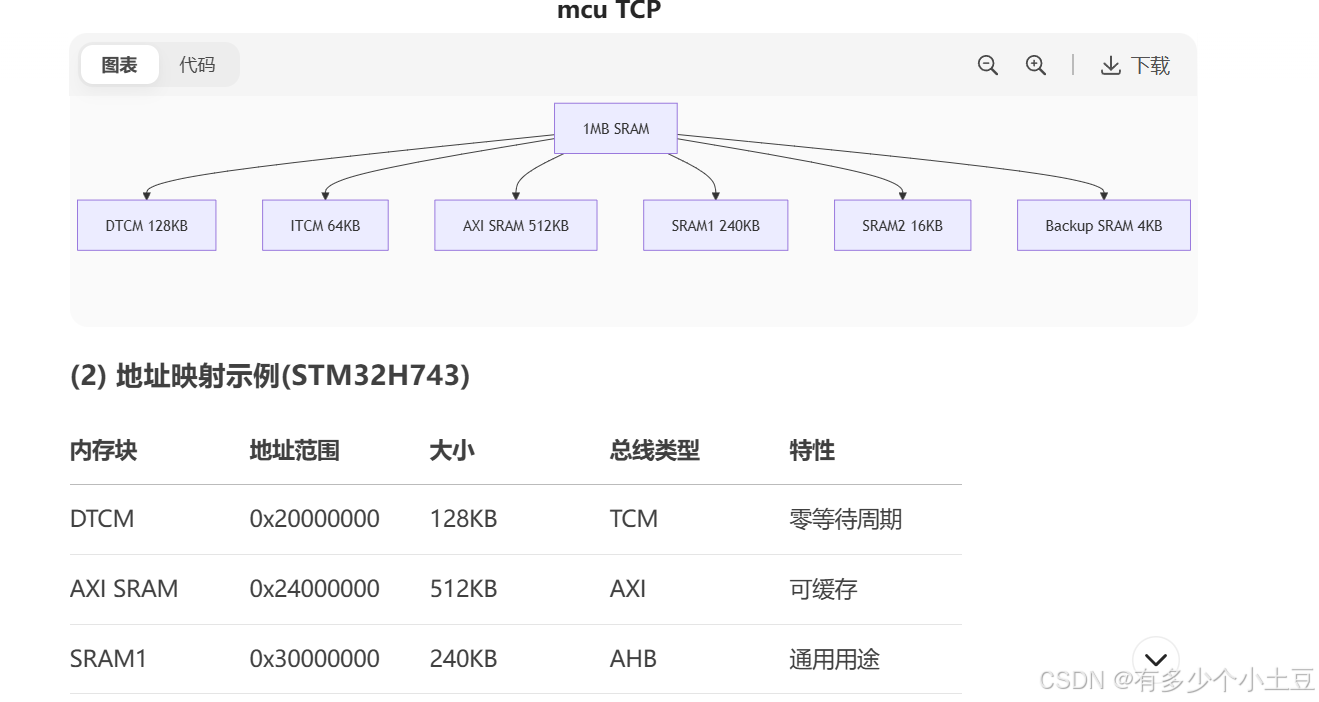

SRAM分类

1.系统SRAM:连接在系统总线上,所有外设和CPU都可访问

2.TCM SRAM:紧耦合内存,专为CPU高速访问设计(如ARM的DTCM)

3.外设SRAM:某些外设专用的缓冲区(如USB、DMA等

128KB = 128 * 1024 byte = 0x20000

地址范围:0x2000_0000 ~ 0x2002_0000

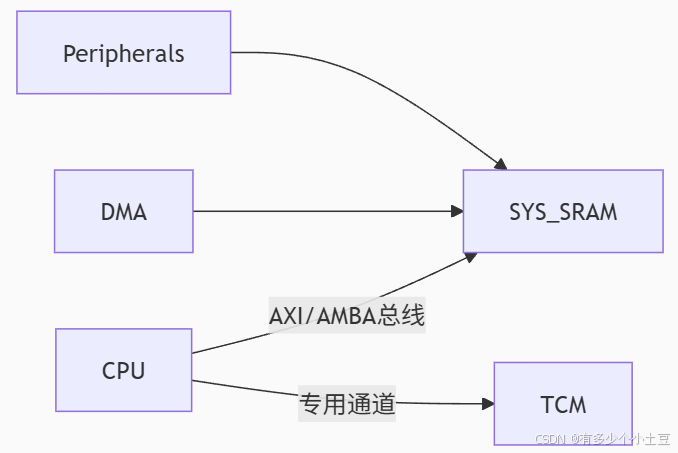

SYS SRAM与TCM DRAM的区别

| SYS SRAM | TCM SRAM |

|---|---|

| 共享资源:多主设备(CPU/DMA/外设)通过总线矩阵访问 | 物理隔离:独立于总线矩阵的专用接口 |

| 缓存支持:通常配合Cache使用提升性能 | 零等待状态:与CPU寄存器同级别的访问速度 |

| 动态分配:支持标准内存管理 “malloc” | 静态分配:需显式指定变量位置 |

SYS SRAM 和AP SRAM区别

SYS SRAM

mcu访问错误的sram地址可能会导致总线访问失败

TCM SRAM

ITCM Instruction Tightly Coupled Memory :指令紧耦合存储器,用于存储需要快速执行的代码(如中断处理程序、关键算法)

DTCM Data Tightly Coupled Memory :数据紧耦合存储器,用于存储需要快速访问的数据(如实时控制变量、DSP数据)

WIFI FW SRAM

在无线芯片(如WiFi/BT Combo芯片)的架构设计中,FW SRAM(固件SRAM)和SYS SRAM(系统SRAM)是两种不同的内存区域,它们在功能和使用方式上有显著差异

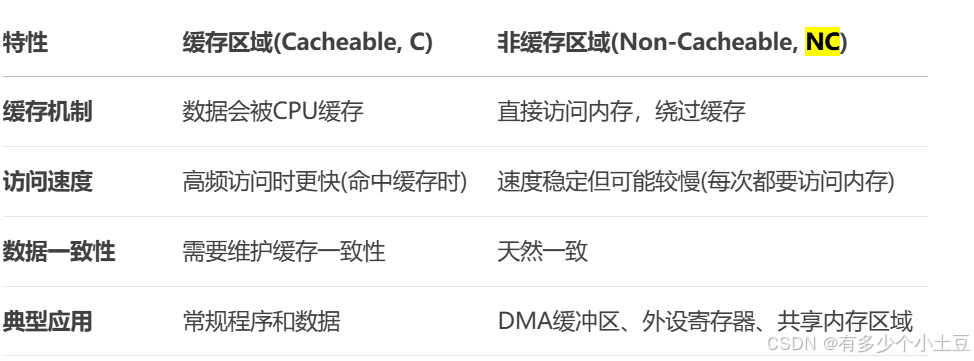

内存属性

内存区域通常被划分为缓存(Cacheable, C)、非缓存(Non-Cacheable, NC)、安全(Secure, S)和非安全(Non-Secure, NS)四种属性

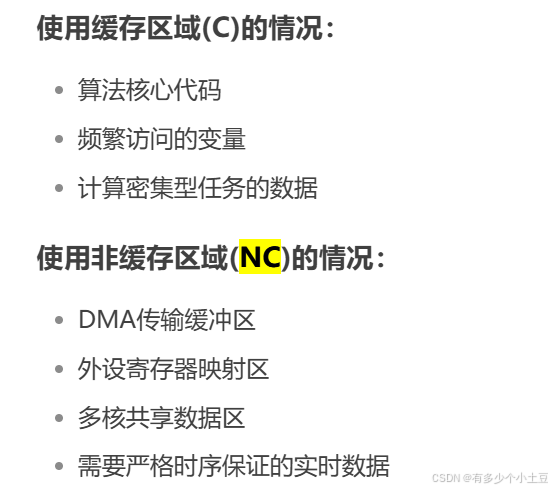

C /NC

在嵌入式系统和MCU开发中,SRAM的缓存(Cacheable, C)和非缓存(Non-Cacheable, NC)区域是两种重要的内存配置方式

S /NS

SRAM的安全(Secure, S)和非安全(Non-Secure, NS)区域划分

查看内存分区

指令

查看内存段指令

`arm-none-eabi-size -A -x your_elf_file.elf`

lst文件

链接器生成的.lst或.map文件中的"Sections"部分提供了关于程序各个段的详细信息

Idx Name Size VMA LMA File off Algn

0 .text 00001234 08000000 08000000 00010000 2**4

ld定义不同SRAM区域

“ram_extra0_bss”

“tcm_data”

__attribute__((section(".ram_extra0_bss")))

static uint32_t system_ram_var;

// 使用宏简化

#define SYS_RAM_VAR __attribute__((section(".ram_extra0_bss")))

SYS_RAM_VAR uint8_t buffer[1024];

ld文件指定SYS SRAM 和 TCM SRAM内存地址范围

MEMORY {

/* 定义内存区域 */

SRAM (rwx) : ORIGIN = 0x20000000, LENGTH = 512K

TCM (rwx) : ORIGIN = 0x10000000, LENGTH = 128K

}

SECTIONS {

/* 系统SRAM区域 */

.ram_extra0_bss (NOLOAD) : {

__ram_extra0_start__ = .;

*(.ram_extra0_bss*)

. = ALIGN(4);

__ram_extra0_end__ = .;

} > SRAM

/* TCM区域 */

.tcm_section : {

*(.tcm_data*)

} > TCM

}

测试

#pragma once

#ifdef __GNUC__

#define SYS_RAM_ALLOC(name) \

__attribute__((section(#s(.ram_extra0_bss, __LINE__))) \

__attribute__((aligned(4))) name

#define TCM_ALLOC(name) \

__attribute__((section(".tcm_data"))) \

__attribute__((aligned(32))) name

#else

#error "Compiler not supported"

#endif

// 使用示例

SYS_RAM_ALLOC(static uint32_t sys_var); // 分配到系统SRAM

TCM_ALLOC(float32_t dsp_buffer[256]); // 分配到TCM

5363

5363

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?