仲裁和时钟生成:ARBITRATION AND CLOCK GENERATION

(1)同步化:Synchronization

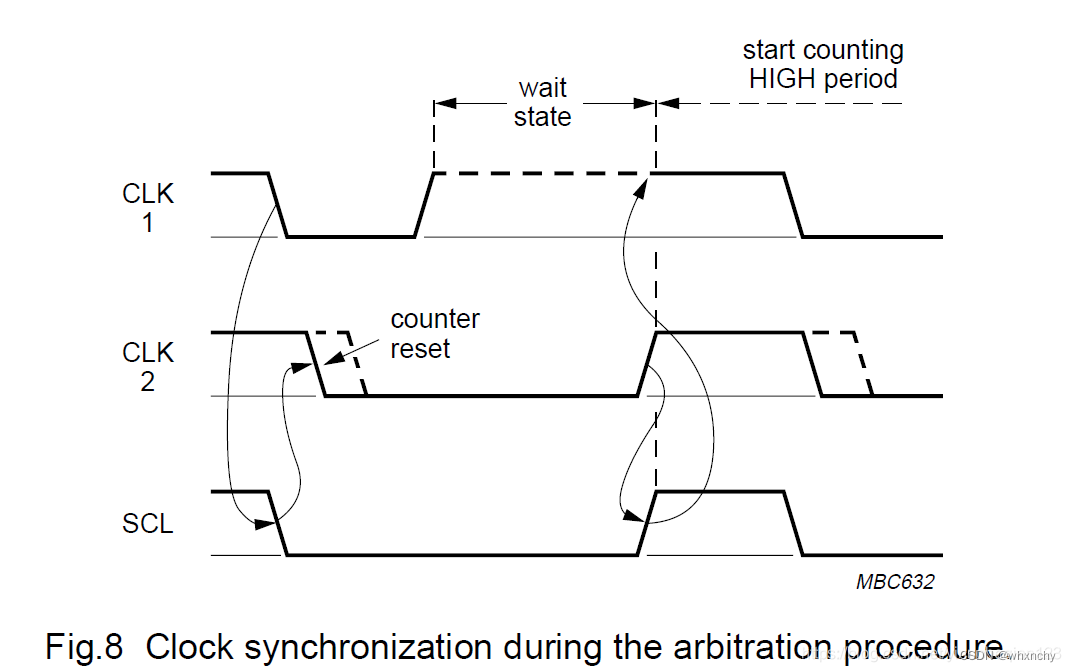

所有主机在SCL线上生成自己的时钟,以在I2C总线上传输消息。 数据仅在时钟的高电平期间有效。 因此,为了进行逐位仲裁过程,需要一个定义的时钟。时钟同步是通过I2C接口与SCL线的线与连接执行的,这意味着SCL线上从高到低的跳变将导致相关设备开始计算其低电平周期,并且一旦设备时钟变为 低电平,它将SCL线保持在该状态,直到达到时钟高电平状态为止。但是,如果另一个时钟仍在其LOW周期内,则此时钟从LOW到HIGH的转变可能不会改变SCL线的状态。 因此,SCL线将被具有最长低电平周期的器件保持低电平。 低电平周期较短的设备在此期间进入高电平等待状态。

当所有相关器件的低电平时间都结束后,时钟线将被释放并变为高电平。 这样,设备时钟和SCL线的状态之间就不会有差异,并且所有设备都将开始计数其高电平周期。 第一个完成其高电平周期的器件将再次将SCL线拉低。

这样,生成了一个同步的SCL时钟,其LOW周期由时钟LOW周期最长的设备确定,其HIGH周期由时钟HIGH周期最短的设备确定。

(2)仲裁

只有在总线空闲时,主机才可以开始传输。 两个或更多个主机可能会在启动条件的最短保持时间(tHD; STA)内产生一个启动条件,从而导致总线定义了一个启动条件。 仲裁在SDA线上进行,而SCL线在高电

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?