1 前言

总线是设备之间交换数据的通路,在计算机系统中存在着各种各样不同的总线。它们具有不同的连接方式,工作频率,数据传输格式以及应用场景。根据应用场景的不同,其可被分为片外总线和片内总线,其中片外总线主要用于芯片与外部设备之间的连接,如I2C、SPI、USB、PCIE等,而片内总线则被用于芯片内部组件之间的互联,如APB、AHB、AXI、ACE和CHI等。

AXI是当前最重要的片内总线协议之一,它从AMBA3开始被支持,当前一共包括AXI3、AXI4和AXI5 三个版本,其目的是为SOC提供高性能、高带宽和低延迟的片内互联方案。它主要支持以下主要特性:

(1)独立的读写通道

(2)支持burst传输

(3)支持非对齐访问

(4)支持原子操作

(5)支持outstanding

(6)支持乱序传输

(7)支持QOS

2 AXI基本读写流程

AXI读写遵循主从模式,即操作由主端口发起,并由从端口接收和响应。其中一个完整的读或写流程被称为一个transaction,如主设备将一个数据写到某地址并接收从设备的响应,或主设备向从设备发送读数据请求,并接收从设备返回的数据和响应,都被称为transaction。

由此可知,在读写流程中,transaction可被分为发送请求、数据以及接收响应这些不同的阶段。AXI在硬件上定义了五个通道来支持这些阶段的操作,其中包括三个写通道和两个读通道。其定义分别如下:

(1)写请求通道AW

(2)写数据通道W

(3)写响应通道B

(4)读请求通道AR

(5)读响应通道R

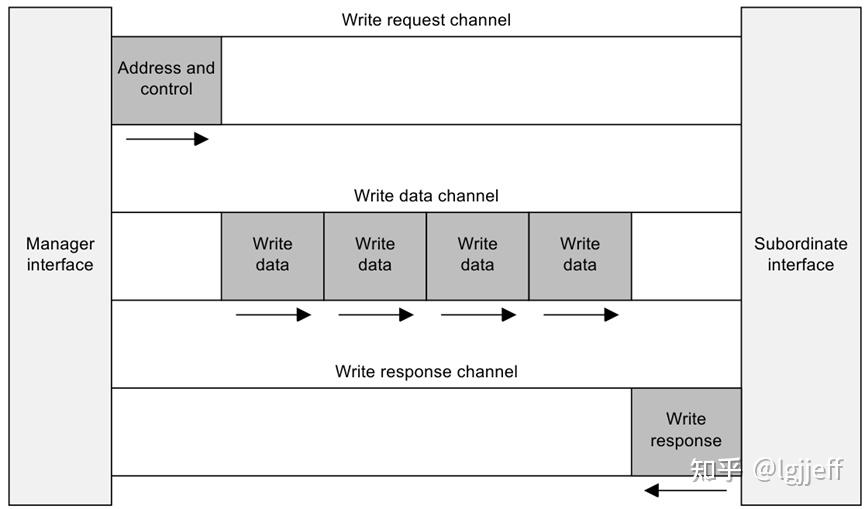

这些通道都具有独立的信号,因此可以并行执行,从而提升总线的性能。在写数据时,主端口会通过上述三个写通道与从端口交互,以下为其示意图:

写数据时,主端口首先需要向写请求通道写入地址和控制信息,然后再向写数据通道写入数据,最后由从端口通过写响应通道返回响应信息。

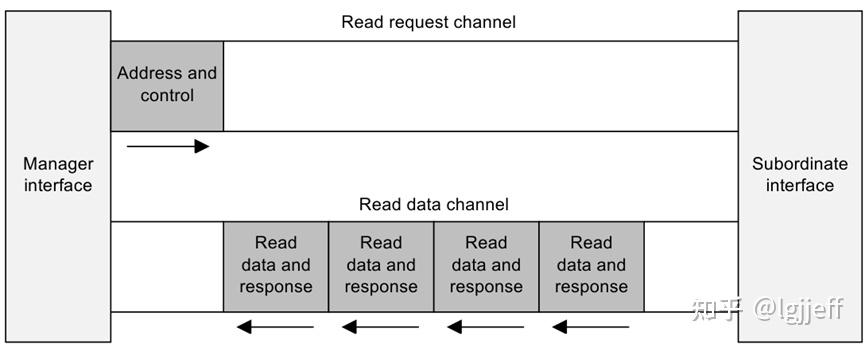

与写数据不同,读数据只有两个通道,这是因为在读操作中,数据和响应都由从端口返回给主端口,因此可以将它们合并为一个通道。以下为其示意图:

3 AXI通道握手

由于AXI通道在硬件上是独立的,因此各自都包含一组硬件信号。其中每个通道都有两个信号VALID和READY用于端口之间的握手,以写请求通道为例,其完整信号名为AWVALID和AWREADY。

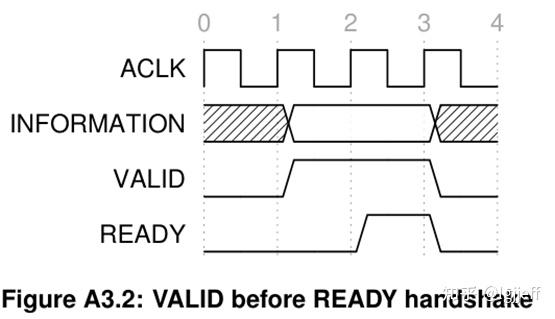

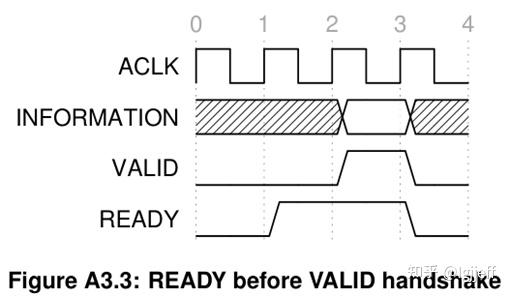

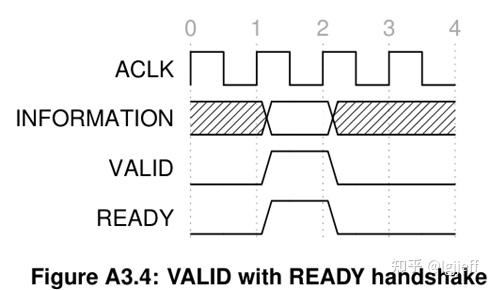

在握手过程中,VALID信号表示已经准备好地址、数据或控制信息。而READY信号则表示其已经准备好接收这些信息。只有当这两个信号都拉高时,传输操作才会执行,但这两个信号拉高的顺序并没有要求。下面为几种不同的情况:

(1)valid信号先于ready信号拉高

上图中源端口在上升沿1之后准备好information数据,并拉高了valid信号。但此时目的端口可能正忙,而没有拉高ready信号,故数据在上升沿2时不能被传输。在上升沿2之后,源端口拉高了ready信号,因而在上升沿3时,它们都已经为高,information数据可以被传输。

需要注意的是,在以上过程中所有已准备好的信号,在数据被传输之前,都不能被改变。这种情况下,目的端口可以利用ready信号反压主端口,以控制其接收数据的速率。

(2)ready信号先于valid信号拉高

上图中目的端口处于空闲状态,在上升沿1之后拉高了ready信号,表明其已经准备好接收数据,但此时源端口数据还没准备好,而没有拉高valid信号。在上升沿2之后,源端口拉高了valid信号,因而在上升沿3时,information数据可以被传输。

(3)valid信号与ready信号同时拉高

上图中在上升沿1之后,valid信号和ready信号同时被拉高,因此在上升沿2处数据就可以被传输了。

另外,对于不同的通道,其valid和ready信号也可能由不同的端口控制。如对于读写请求通道和写数据通道,valid信号由主端口控制,ready信号由从端口控制。而对于读写响应通道,valid信号由从端口控制,ready信号则由主端口控制。

虽然同一个通道的VALID和READY信号允许有不同的拉高顺序,但不同通道之间的信号依然有相互依赖,如响应通道必须在请求通道或数据通道之后才能拉高。下图是写通道之间的顺序依赖,其中双箭头表示它们之间必须要遵循先后关系,而单箭头之间表示没有严格的先后关系:

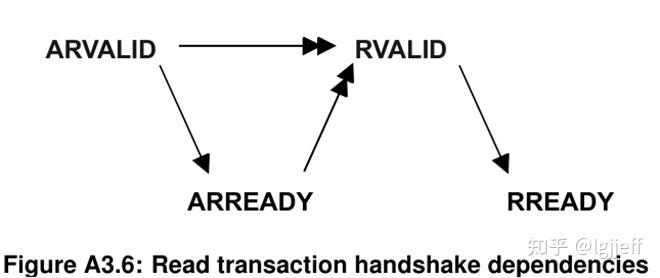

下图为读通道之间的依赖关系,从图中可看出读响应通道必须要在读通道之后:

4 burst传输

我们先回忆一下AXI的transaction流程,以写数据为例,则其包含写请求、写数据和写响应三个阶段。若还采用以上方式,当需要写入一块连续数据时,则这块数据需要按AXI位宽为粒度进行拆分,然后每个transaction传输一个该粒度的数据,直到把所有数据传输完成。在该过程中,每个数据的传输都包含了一个写请求和一个写响应,显然对带宽的影响较大。

为此,AXI通过支持突发(burst)传输来提升总线性能。其思想就是在传输连续数据时,在读写request中指定突发传输的参数(如数据长度信息),然后总线在读写数据阶段连续地执行数据读写操作,直到传完所有数据后,再发送完成响应。AXI请求通道通过AxSIZE、AxLEN和AxBURST信号来支持burst传输:

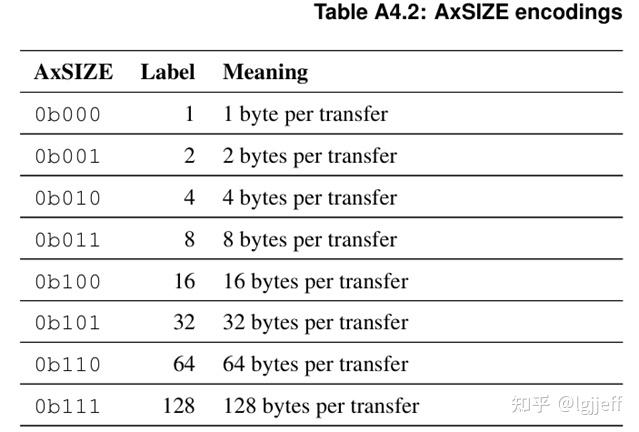

(1)AxSIZE:该信号表示每个transfer传输的数据长度,由于AXI总线支持的数据位宽为8 – 1024 bits,即1 – 128 Bytes,因此AxSIZE的范围也是1-128 BYTES。其中该信号的编码格式如下:

(2)AxLEN:该信号表示一个transaction中包含多少个data transfer。由于其宽度为8 bit,而一个transaction中的transfer数量为AxLEN + 1,故其最大值为256。

同时由于AXI协议规定一个transaction的数据不能跨越4K边界,从而单个transaction传输的数据总长度最高不能超过4K字节,因此当AxSIZE较大时,AxLEN的值会更小。最后,对于wrapping bursts模式,该值只能取2、4、8或16。

(3)AxBURST:该信号用于指定在burst传输时,transfer之间地址递增的模式。AXI一共支持以下三种模式。

- FIXED:该模式中每个transfer访问的地址都是相同的

- INCR:该模式中地址会随着transfer而递增,其中递增的值取决于AxSIZE

- WRAP:该模式中地址也会随着transfer递增,但当地址增加到某个地址后,就会回绕到开头的位置

5 窄传输与非对齐传输

AXI总线的最大位宽可达1024 bit,若单次传输数据的长度小于总线位宽,则该次传输就需要只传输部分有效数据,这种情形就是窄传输。

在AXI协议中,窄传输是通过WSTRB信号实现的,该信号的宽度为DATA_WIDTH / 8,即其每一位用于控制一个字节的数据是否有效。以下为其中的两个例子:

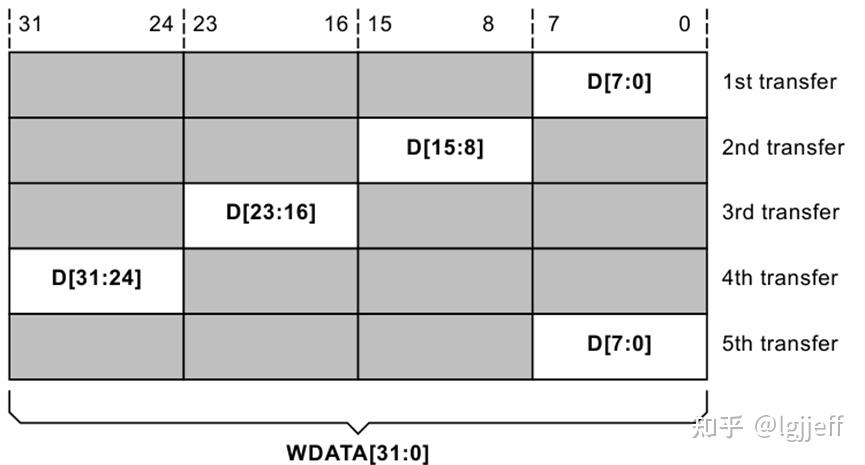

(1)32 bit位宽,8bit有效数据

上图中总线位宽为32 bit(4字节),一共传输了5个data transfer,且每个transfer只传输一个字节。则各transfer的WSTRB值分别为0b0001, 0b0010, 0b0100,0b1000和0b0001。

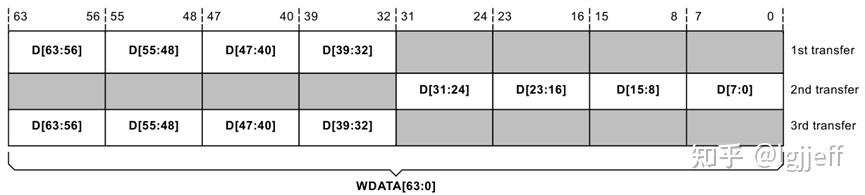

(2)64 bit位宽,32 bit有效数据

上图的总线位宽为64 bit(8字节),一共传输了3个data transfer,其每个transfer会传输4个字节。则各transfer的WSTRB值为0b11110000,0b00001111, 0b11110000。

一般情况下,数据访问需要满足按字对齐(如4字节),则此时地址的低两位必须为0。非对齐访问指的是访问地址不是按字对齐的transfer,不同总线对非对齐访问的支持并不相同,如AHB不支持,而AXI是支持的。在AXI中可以使用以下两种方式实现非对齐访问:

(1)使用低位地址信号发出非对齐的起始地址

(2)使用一个对齐的地址,然后与byte lane strobes信号结合,以表示一个非对齐的地址

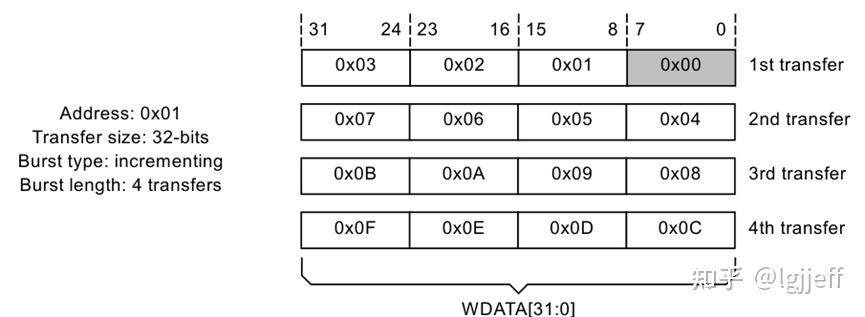

如以下是一个非对齐访问的示例:

在这个transaction中,第一个transfer中其起始地址为0x1,因而只有byte 1 – byte 3数据有效,故它是一个非对齐访问。因此,在这个transfer中,只有byte1 – byte3会被传输。

6 原子操作

原子操作是一种基本的同步机制,这类操作从软件视角来看,其执行流程就像是不可分割的。但在硬件层面确并非如此,而是可能由几个步骤组合而成,因此硬件需要通过一定的机制来支持该特性。

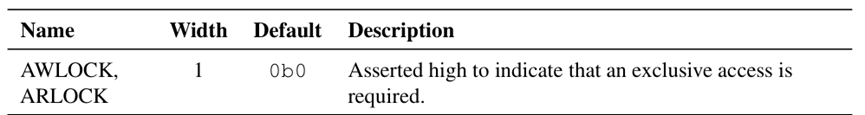

AXI协议通过独占访问(exclusive access)来支持原子操作,其基本原理是通过AxLOCK信号标识一个访问是否为独占,并通过硬件monitor监视独占访问地址,以确定独占访问是否能成功。其中AxLOCK信号的定义如下:

AWLOCK表示是一个独占写操作,ARLOCK则表示是一个独占读操作。除此之外,支持独占访问的AXI从端口需要实现一个monitor硬件,以监视独占访问相关的状态。以下为其基本原理:

(1)monitor硬件在AXI的从端口上实现,并用于记录exclusive read操作对应的地址和AR ID值。其中monitor硬件需要为每个能独占访问该端口的主端口保留一个unit,用于记录该端口对应的exclusive read操作

(2)当对一个地址执行了exclusive read操作后,monitor就会监视该地址

(3)若此后该地址发生了写操作,则数据发生了改变,此时monitor中与该地址相关的unit都需要被删除

(4)若相同AR ID在执行一次exclusive read之后,又对一个不同的地址执行一次新的exclusive read操作,则前一次的信息会被后一次替换

(5)此后若接收到一个exclusive write操作,则监视器会查询monitor中记录的信息。若其中包含了与写操作AW ID相同的AR ID,以及地址也相同的条目,则表明该地址的数据没有被修改过,因此独占写操作就会成功

(6)反之,若monitor查找不到匹配的信息,则表明该数据已经发生了修改,或者已经被其它exclusive read操作覆盖。此时该次exclusive write访问就会失败,主端口需要从头开始发起一次完整的流程来重试

以上状态机是基于AR ID和AW ID的,为了确保ID值的一致性,它需要满足一定的约束条件:

(1)每个原子操作必须使用相同的AXI ID,如请求、写响应、读数据等

(2)原子操作不能与未完成的非原子操作使用相同的AXI ID

(3)同时执行的多个原子操作不能使用相同的AXI ID

7 outstanding和乱序传输

在介绍outstanding之前,我们先回忆一下AXI协议数据传输的基本流程,对于写操作包括写请求、写数据和写响应三个阶段,对与读操作则为读请求和读响应两个阶段。在这种方式下,若请求和响应之间速度较慢,则主端口需要一直等待slave的响应,从而影响总线的效率

outstanding即是用于解决该问题的,当支持outstanding后,主端口就可以连续发起多个transactions,而不必等待前面的transaction完成。如当outstanding值为3时,则其可以一次性发出三个transaction,然后等待它们的响应。另外,在AXI中响应返回的顺序并不需要与请求发出的顺序相同,例如请求发出的顺序为1、2、3,而响应的顺序可以是3、2、1或2、1、3等,这种特性被称为乱序传输。当然,并不是所有transaction都是可以乱序的。在AXI中,其需要遵循以下约束:

(1)对于读操作,相同AR ID的transaction需要保序,即其响应需要按发送的顺序返回。不同AR ID的transaction之间不需要保序,即响应可以不按发送顺序返回

(2)对于写操作,其原则与读操作相同,即相同AWID的transaction需要保序,而不同AW ID的transaction不需要保序

1493

1493

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?