module mux2(

a,

b,

sel,

out

); //模块的开始 括号里是端口列表

input a;

input b;

input sel;

output out; //对端口类型进行声明

//assign 连续赋值语句

assign out = (sel == 0)? a : b;

endmodule//模块的结束

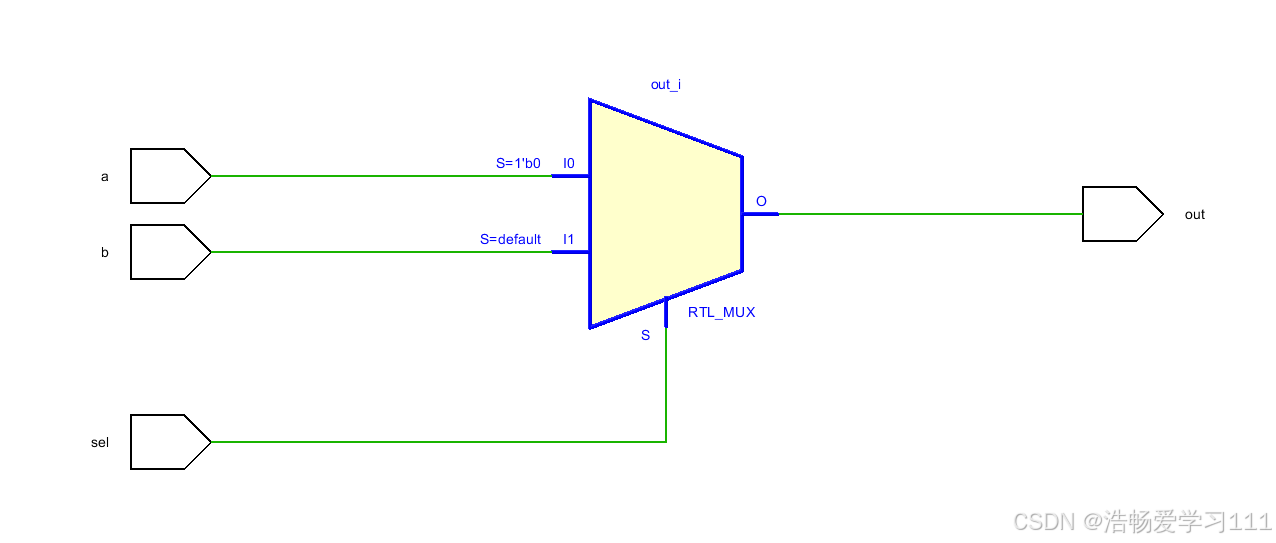

该代码实现了一个简单的二选一多路器功能.3路输入信号,1路输出信号.下面点击vivado的Open Elaborated Design 对代码进行分析综合.

自动生成一个符合我们上面代码的二选一多路器原理图.

`timescale 1ns / 1ns //指定用到延时语句的单位的精度

//例化

module mux2_tb();

reg s0;

reg s1;

reg s2;

wire mux2_out;

//1.mux2 模块名 mux2_1 标签名

//2. 连接端口

//3.产生激励信号

mux2 mux2_1(

.a(s0),

.b(s1),

.sel(s2),

.out(mux2_out)

);

initial begin //从仿真0时刻开始,顺序执行语句内的内容

s2 = 0; s1 = 0; s0 = 0;

#20; //延时20ns 精度为ps

s2 = 0; s1 = 0; s0 = 1;

#20;

s2 = 0; s1 = 1; s0 = 0;

#20;

s2 = 0; s1 = 1; s0 = 1;

#20;

s2 = 1; s1 = 0; s0 = 0;

#20;

s2 = 1; s1 = 0; s0 = 1;

#20;

s2 = 1; s1 = 1; s0 = 0;

#20;

s2 = 1; s1 = 1; s0 = 1;

#20;

end

//mux2 mux2_2(

// a,

// b,

// sel,

// out

//);

endmodule

二选一多路器的仿真文件

reg (寄存器类型)用于定义寄存器变量。寄存器是一种能够存储数据并在时钟信号控制下改变其存储值的数据元素.

-

状态保存: 寄存器可以在时钟周期之间保持其值不变,这对于实现状态机等需要保存状态的应用非常重要。

-

数据暂存: 在复杂的逻辑运算中,寄存器可以作为中间结果的存储单元,确保数据的一致性和完整性。

-

时序控制: 使用寄存器可以更好地控制数据的流动时间,通过同步时序逻辑来避免亚稳态等问题。

注意:

-

确保所有的

reg变量都在时序逻辑块中赋值,避免组合逻辑中出现寄存器赋值的情况,这会导致不必要的时延并可能导致设计错误。 -

当使用

reg类型变量时,应当明确指定其初始化值,特别是当涉及到复位逻辑时。

wire用于定义线网类型的变量,这类变量通常用来表示组合逻辑电路中的连接线。线网变量在电路中起到传递信号的作用,并且其值直接由驱动它的表达式的当前值决定。在此次工程中表现为(assign out = (sel == 0)? a : b;)

-

组合逻辑:

wire变量主要用于描述组合逻辑电路,这类电路的特点是没有记忆功能,输出仅依赖于当前的输入信号。 -

即时响应: 在组合逻辑中使用

wire可以确保信号传递的即时性,即输出会随着输入的变化而立即改变,非常适合用于需要快速响应的应用场合。 -

减少延迟: 相比于

reg类型的变量,wire没有存储延迟,因此在构建高速的数字电路时非常有用。 -

资源消耗: 在FPGA实现中,使用

wire类型变量通常意味着较少的硬件资源消耗,因为它不需要触发器等存储元件的支持。

注意

-

避免未初始化: 由于

wire类型的变量没有默认值,因此必须在定义后立即通过assign语句或模块端口映射等方式给出其值。 -

防止悬空: 如果

wire没有被正确地驱动,则可能会导致不确定的状态(高阻态),这在实际硬件实现中是非常危险的。

3095

3095

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?