1.概述

PCF8563是sharp公司开发的一款低功率,I2c接口的时钟/日历芯片,为需时钟应用的系统提供了价格低廉的解决方案。提供可编程的时钟输出,支持中断输出和低电压检测,最大数据传输速率为400kbit/s,内部的地址值会随着读写操作自动增加。

2.特性

*基于32.768khz的方波时钟提供年、月、日、小时、分钟、和秒计时

*世纪标志

*1.0-5.5v宽电压工作

*时钟后备电流:0.25UA,电压:3v(环境温度:25度)

*400khz I2C接口(在1.8-5.5v)

*可为外设提供:32.768khz,1024hz,32hz,1hz时钟

*闹钟和时钟功能

*内置振荡外围电路

*内置电源复位

*I2C总线从地址(读A3H,写A2H)

*开屚中断输出

3.应用范围

*移动电话

*便携设备

*传真

*电池供电产品

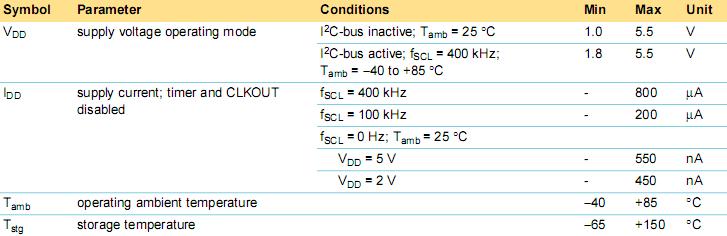

4相关参数

如下图所示

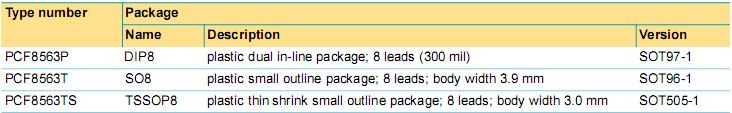

5.封装参数

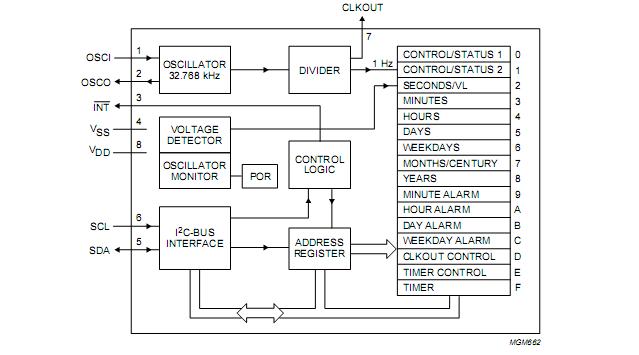

6.电路方块图

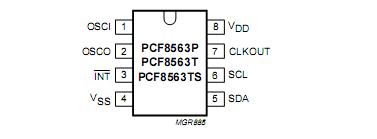

7.针脚定义

OSCI为晶体输入端

OSCO为晶体输出端

INT为中断开屚输出,低有效

CLKOUT为时钟输出

SCL为时钟输入

SDA为串行数据输入输出

VDD为电源供应

Vss为电源地

8.功能描述

PCF8563提供16个8位寄存器,当读写操作时这写地址寄存器的地址会自动增加,第一二个寄存器(00H-01H)为控制状态寄存器,02H-08H为时钟功能寄存器(秒至年计数器)09H-0CH为闹钟功能寄存器,0DH控制时钟输出频率。0EH和0FH分别为时间控制和时间寄存器。秒到年和闹钟的分到天都为BCD编码。周和闹钟的周计时都不是BCD模式编码。当在读一个寄存器时,其它的寄存器是被冻结的,这样可以避免其它寄存器被破坏。

8.1闹钟功能模块

通过清除每个闹钟寄存器的最高位,闹钟将被使能,从每分到每周,通过设置AF标志(控制/状态寄存器的第3位)来产生中断当闹钟条件发生时,AF标志只能用软件清除.

本文介绍PCF8563时钟/日历芯片的主要特性及应用范围,包括其低功率设计、I2C接口、时钟输出选项及内置振荡电路等。同时探讨了该芯片的封装参数、电路方块图和针脚定义。

本文介绍PCF8563时钟/日历芯片的主要特性及应用范围,包括其低功率设计、I2C接口、时钟输出选项及内置振荡电路等。同时探讨了该芯片的封装参数、电路方块图和针脚定义。

1357

1357

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?