目录

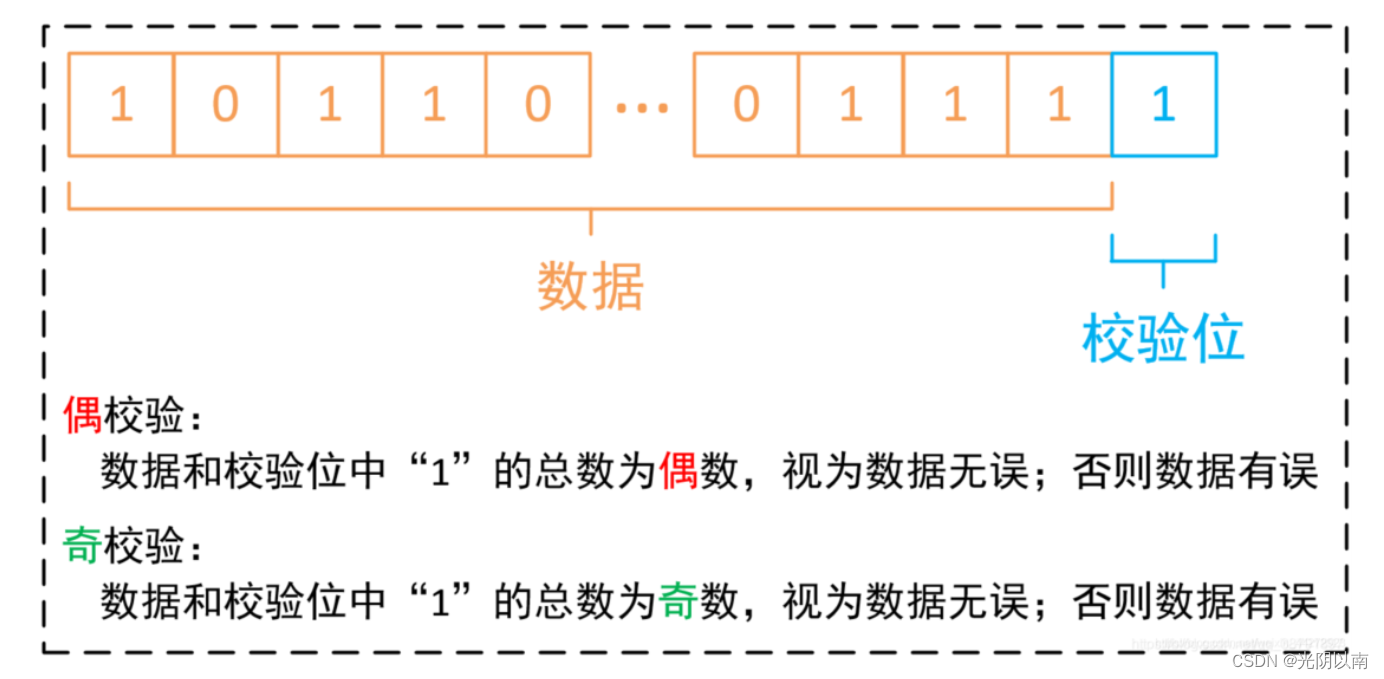

奇偶校验(Parity Check)是一种校验代码传输正确性的方法。根据被传输的一组二进制数位中“1”的个数是奇数或偶数来进行校验。*采用奇数的称为奇校验,反之,称为偶校验。采用何种校验是事先规定好的。通常专门设置一个奇偶校验位,用它使这组代码中“1”的个数为奇数或偶数。若用奇校验,则当接收端收到这组代码时,校验“1”的个数是否为奇数,从而确定传输代码的正确性。

注意奇校验的定义是数据和校验位中“1”的总数,而不仅仅是数据中的奇数位数

奇偶校验流程:

-

发送方要发送的数据是4bit,使用奇校验,那么还要发送一位校验位,校验位根据4位数据的异或结果取反得到(4bit数据异或的结果是1代表着数据中1的个数已经是奇数个,如果是0则要补上1凑成奇数个1)

-

接收方接收4位串行发送的数据,根据输入的数据自己的奇校验位不停翻转。当发送到第5个周期时,将自己的奇校验位与发送过来的奇校验位进行对比,如果相同则说明发送正确。

1 输入数据的校验方法

根据输入串行数据码流,“实时”生成所输入数据的校验位。 欲串行接收数据“11101000”(传输低位在前,高位在后),则数据线上的数据应为“0-0-0-1-0-1-1-1”

奇校验应为“x-1-1-1-0-0-1-0-1”(采用时序逻辑输出,会落后一个时钟周期) 偶校验应为“x-0-0-0-1-1-0-1-0”(采用时序逻辑输出,会落后一个时钟周期)

输出信号odd根据输入信号变化,假如输入数据只输入4-bit,0001,则奇校验位0,偶校验位1,可以看 到在输入信号的下一个周期,odd、even的输出符合预期,其他数据相同,这里不赘述。

-

奇校验实现方式:校验位默认为高电平,每检测到1,则状态翻转

-

偶校验实现方式:校验位默认为低电平,每检测到1,则状态翻转

module odd_even1(

input clk ,

input in , //串行输入

input reset , //同步复位,高电平有效

output reg odd , //奇校验位

output reg even //偶校验位

);

always@(posedge clk)begin

if(reset)begin

odd <= 1'b1;

even <= 1'b0;

end

else if(in)begin

odd <= ~odd;

even <= ~even;

end

else begin

odd <= odd;

even <= even;

end

endmodule

2 输出数据的校验方法

除了对接收数据的正确性做奇偶校验外,同时也需要对输出给的外部数据提供一个奇偶校验结果,方便外部模块比对数据是否传输正常。

欲串行发送数据“11101000”:

-

奇校验结果应为“1”,实际应传输“111010001”

-

偶校验结果应为“0”,实际应传输“111010000”

实现方法:根据异或的定义:相异为1,相同为0。可推出:偶数个1异或的结果为0,奇数个1异或的结果为1。

-

偶校验:将输入数据按位异或

-

奇校验:将输入数据按位异或再取反(与偶校验相反)

奇校验和偶校验的计算方法

-

偶校验位的计算:如果数据中1的个数是偶数,那么偶校验位为0;如果1的个数是奇数,则偶校验位为1。使用Verilog的按位异或运算符

^可以很容易地实现这个计算,因为异或运算会将所有位上的1进行异或操作,如果1的个数是偶数,异或的结果为0;如果是奇数,结果为1。 -

奇校验位的计算:与偶校验相反,如果数据中1的个数是偶数,那么奇校验位为1;如果1的个数是奇数,则奇校验位为0。这可以通过取偶校验位的反值来实现。

Verilog中的按位异或运算符 ^

Verilog中的按位异或运算符 ^ 可以用于多位信号。当用于多位信号时,它会将所有位上的信号进行异或操作,最后产生一个单一位的结果。这个操作在计算奇偶校验位时非常有用。例如,^in 会对输入 in 的所有8位进行异或操作。

module odd_even2( input clk, // 时钟信号,用于同步操作 input [7:0] in, // 8位的并行输入数据 input reset, // 同步复位信号,高电平有效 output reg odd, // 输出的奇校验位 output reg even // 输出的偶校验位 ); always@(posedge clk) begin if (reset) begin odd <= 1'b0; even <= 1'b0; end else begin odd <= ~(^in); // 计算奇校验位 even <= ^in; // 计算偶校验位 end end endmodule

在给定的代码中,even <= ^in; 这行代码直接得到偶校验位,而 odd <= ~(^in); 这行代码首先计算偶校验位,然后取反得到奇校验位。这正符合奇校验位和偶校验位的定义。

3 奇偶校验的优缺点

优点:实现简单 缺点:

-

效率低

-

如果传输过程中偶数个位同时错误则无法校验出来

-

无法检查出0的错误(多100个也检查不出来

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?