OTG :On-The-Go

Driver for linux:/drivers/usb/dwc2

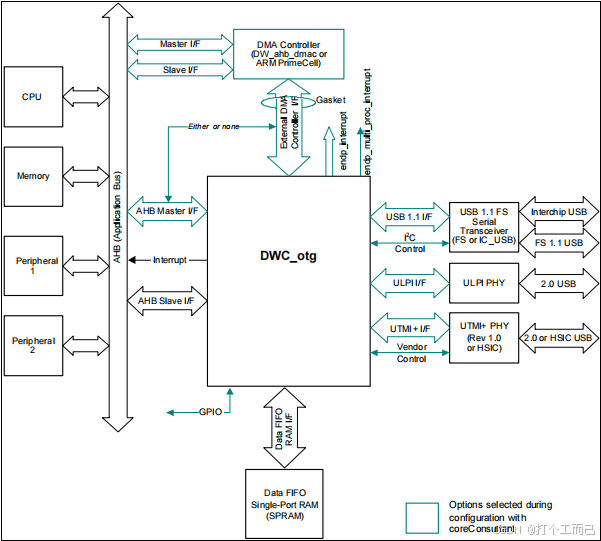

功能接口

1. AHB Slave and Data RAM

- AHB Slave:为微控制器提供对控制器的控制和状态寄存器(CSRs)、数据FIFO和队列的读取和写访问权限

-

Data RAM interface:数据RAM接口,它连接到外部单端口FIFO RAM(SPRAM),用于事务数据存储。可配置,32到32,768深,宽35位宽(32个数据位加上3个控制位)

-

DWC_otg controller支持所有的PHY和系列收发接口

2. Optional Interfaces

这些接口是可选的,只有在使用核心顾问工具选择适当的参数时才能构建:

■内部DMA控制器(AHB Master)使控制器成为AHB上的主服务器,向AHB传输数据。

■供应商控制接口ULPI和UTMI+ PHY寄存器

■I2C接口OTG控制在USB 1.1 FS模式

■通用I/O(GPIO)接口

■SOF更新切换端口(不用于DWC_otg)

■SOF输入计数端口(不用于DWC_otg)

■基于描述符的散射/DMA控制器收集设备和主机模式。(不支持基于描述符的一致性顺序DMA。)

■控制器在设备和主机模式下都支持散射聚集DMA操作。如果设备模式具有等时端点支持,请选择此选项,以获得更多的性能。请注意,在主机散点聚集DMA操作模式中不支持集线器(拆分传输)。仅在主机缓冲区DMA(内部DMA)操作模式下才支持拆分传输。

■多处理器中断的设备模式。此特性支持特定端点的中断掩码寄存器和来自控制的特定端点的中断信号

3. Transmit and Receive FIFOs

DWC_otg控制器上的发射和接收FIFO接口用于将数据进出数据FIFO RAM。这些被分为周期性(等时和中断传输)或非周期性(批量传输和控制传输),并总结为对于所有主机IN和设备OUT传输的单一接收FIFO

■ 对于非周期主机OUT传输的单一通用非周期Tx FIFO。

■ 可选的单周期传输FIFO为定期主机输出传输。

■ 周期性/非周期性设备传输的每个IN端点专用Tx FIFOs。

■ 主机模式中断OUT和设备模式中断IN(仅在共享FIFO操作中)传输可以被编程为通过非定期传输FIFO或定期传输FIFO。

Features List

1. General Features

■1软件可配置为OTG1.3和OTG2.0操作模式

❑OTG2.0支持ADP(附加检测协议)

■支持以下速度:

❑高速(HS,480Mbps),

❑全速(FS,12Mbps)和

❑低速(LS,1.5Mbps)模式

■多选项可用于低功耗操作

■多DMA/非DMA模式访问支持应用侧

■MAC

■多接口支持AHB不同时钟和PHY接口便于集成

■支持最多16个双向端点,包括控制端点0。

■低速不支持DWC_otg作为具有UTMI+物理功能的设备。

■2支持会话请求协议(SRP)

■3支持主机协商协议(HNP)

■最多支持16个主机通道。在主机模式下,当要支持的设备端点数量超过主机通道数量时,软件可以重新编程通道以支持最多127个设备,每个设备有32个端点(IN + OUT),最多支持4,064个端点。

■支持在主机缓冲器DMA模式、从属模式和外部DMA模式下的外部集线器连接。注: DWC_otg控制器在主机散射收集DMA操作模式下不支持拆分

2. Configurable Features

■ 使用核心顾问实用程序配置控制器的用户要求

■ 能力选择多个功率轨道为低功率模式

■ 选择多个DMA操作模式

■ 选择类型的Mac-Phy接口需要

3. Application Interface Features

■ 接口通过AHB:

❑AHB Slave接口,用于访问控制和状态寄存器(CSRs)、数据FIFO和队列

■ 当内部DMA启用时,数据FIFO访问,

■ 支持AHB时钟频率高达270 MHz与合适的技术(测试与标准65 nm技术,并没有布局后的延迟,时钟树合成或门级模拟)仅为某些配置。

■只支持AHB上的32位数据。

■支持小的或大的环境模式(可按引脚选择)。

■支持INCR4、INCR8、INCR16、INCR和AHB从属接口上的单次传输。

■支持在AHB主界面上的拆分、重试和错误AHB响应。不会在AHB从属界面上生成拆分和重试响应。

■软件-在DMA模式❑下的AHB主接口上可选择的AHB突发类型。如果选择了INCR4,控制器只使用INCR/INCR4,或单一。

❑如果选择了INCR8,控制器通常使用INCR8,但在传输的开始和结束时,它可以使用INCR或Single,这取决于传输的大小。

❑如果选择了INCR16,控制器通常使用INCR16,但在传输的开始和结束时,它可以使用INCR或Single,这取决于传输的大小。

■将处理固定的突发地址对齐方式。例如,只有当级别较低的地址[5:0]均为0时才使用INCR16。

■在AHB主接口上生成AHB忙周期

■处理1KB边界分割

4. MAC-PHY Interface Features

■支持以下MAC-Phy接口:❑UTMI 8/16、❑ULPI、❑HSIC、❑IC_USB(用于低速/全速)、❑FS Shared在UTMI

■支持UTMI+ Level 3接口(第1.0版,2004年2月25日)。系统支持8位、16位和8/16位的数据总线。

■支持ULPI接口(修订版1.1rc,2004年9月1日),8位SDR,4位DDR,6针串行,3针串行和Carkit。

■UTMI+ L3和ULPI可以同时存在并被软件选择,或者在核心配置期间只能指定所需的接口。只有当选择了UTMI+时,才能选择

■HSIC接口。否则,无法选择HSIC接口

■I2C接口(用于支持迷你USB模拟Carkit接口规范,CEA-936,修订版2)。不打算与其他设备一起使用。

■支持UTMI-to-UTMI桥(参见附录J,“UTMI-to-UTMI桥附加功能”)

5. System Memory Architecture

■支持Slave,1个外部DMA控制器接口,或内部DMA模式

■可选的,在选择内部DMA模式时,基于描述符的散射/收集DMA操作

■包括到外部DMA控制器的可选接口;数据通过AHB从属接口传输。

2426

2426

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?