第5章 面向制造的设计简介

目录

印制电路板组装与焊接工艺简介 83

组装工艺 84

焊接工艺 85

元器件放置与方向指南 89

通孔器件的元件间距 91

表面贴装器件的元件间距 93

混合通孔器件和表面贴装器件的间距要求 95

面向印制电路板可制造性的焊盘图形和焊盘堆栈设计 95

表面贴装器件的焊盘图形 96

通孔器件的焊盘图形 103

参考文献 109

印刷电路板组装和焊接工艺介绍

要使印刷电路板可制造,裸板必须能够在标准制造公差范围内进行制造,并且电路板必须能够根据不同的元件技术进行组装。如前几章所述,设计和制造印刷电路板有许多步骤。当设计完成并提交给板厂时,板厂必须能够执行设计所要求的制造步骤。印刷电路板是否可制造,实际上从Capture中的元器件创建和原理图输入、焊盘堆栈与封装设计、PCB编辑器中的元器件布局与走线布线以及artwork production等环节就开始了。

但这还不是全部。一旦电路板制造完成,如果没有功能元器件,它就几乎没有用处。这些元器件需要能够被安装到电路板上,且不能损坏元器件或电路板本身。元器件的安装包括定位元器件(取决于正确的元器件布局和方向)以及在元器件引脚与电路板的安装焊盘之间形成可靠的焊点(这取决于良好的焊盘堆栈和封装设计)。本章提供了为可制造性印刷电路板设计焊盘堆栈、封装设计和元器件布局所需的信息。

组装工艺

印制电路板可以手工组装,也可以通过自动化设备进行组装。组装工艺取决于元器件技术的类别(如第4章:行业标准介绍中所述的A到Z类)以及一次性需要组装的电路板数量。一些公司可能在同一场所同时进行电路板的制造和组装,而有些公司可能仅专注于印制电路板制造,另一些则仅专注于PCB组装。由于间距、方向问题以及焊接工艺的影响,组装方式会影响PCB的布局设计。以下简要概述了组装工艺以及元器件布局、方向和间距的考虑因素。

手工组装工艺

手工组装通常用于原型和小批量生产,以及自动化组装后对异形元件的处理。表面贴装技术(SMT)和通孔插装技术(THT)元器件均可通过手工方式进行组装。在小批量生产中,可采用由多名装配工人组成的装配线,每人负责安装特定的元器件。在印刷电路板组装过程中,可多次中断组装工艺,对印刷电路板的部分区域进行功能测试。手工组装可能包括手工放置和焊接,或手工放置与自动焊接相结合的方式(如下所述)。

手工组装可能是一项繁琐的工作。在印刷电路板项目中保持元器件布局和方向的一致性,有助于装配工人进行手工组装。例如,将有极性元件(电容器和二极管)朝向同一方向排列,并使集成电路(IC)的引脚1位于相同方向,可显著减少组装缺陷并提高良率。

自动化组装工艺(拾取放置)

表面贴装器件(SMD)和通孔器件(THD)均存在自动插装工艺(拾取与放置),其中通孔器件包括径向引线和轴向引线器件。自动化设备被编程用于从卷盘或料盒中提取元器件,并将其放置在印刷电路板(PCB)的正确位置和方向上。通孔器件通常可以以每小时20,000至40,000个元件(CPH)的速度进行装配(Coombs,2001,第41.2.5节,第41.10页)。用于编程自动化贴装设备的数据可由PCB编辑器及其他计算机辅助制造程序输出提供。

通孔器件通常以成卷或成条的元件形式封装,其引线通过胶带固定在一起。通孔元件通常仅放置在板子的顶层,以便引线可以进行波峰焊接,而元器件本身不会接触到熔融焊料。焊接工艺如下所述。

通孔器件的典型自动化工艺步骤是先插入双列直插式封装,然后是轴向引线器件,接着是径向引线器件,最后是异形器件。元器件插入完成后,电路板通常采用波峰焊接(波峰焊接在下文描述),但也可以采用回流焊接(侵入式回流焊接;参见Coombes, 2001,第43.10页),如下所述。

表面贴装器件通常采用管状包装、矩阵托盘、卷带包装和散装形式。表面贴装器件可安装在印刷电路板的一侧或两侧。当仅安装在顶层时,通过丝网印刷将焊膏涂覆到印刷电路板的焊盘上。然后由贴片机将元器件放置到电路板上,使元件引脚端子插入焊膏中,从而临时固定元器件位置。接着将电路板送入回流焊炉,使焊料熔化后冷却,从而将元器件固定在电路板上。通常情况下,表面贴装器件的装配速度可达每小时10,000至100,000个(库姆斯,2001,第41.3.2节,第41.15页)。

当表面贴装器件(SMDs)安装在印刷电路板(PCB)的两侧,或电路板同时包含表面贴装器件和通孔器件(THDs)时,采用顺序回流/波峰焊接工艺。首先,使用下文所述的焊膏和回流焊工艺将顶层的表面贴装器件固定到电路板上。接着,从顶层插入通孔器件,并通过引脚弯折固定(将引线在底层弯曲)、在顶层粘接元器件,或在某些情况下依靠引线与孔之间的摩擦力来固定位置。然后将电路板翻转,在其底面由自动点胶机施加胶点。底面表面贴装器件随后通过手工或贴片机放置到胶点上。胶水将底面表面贴装器件固定在位,直至焊点焊接完成。组装件随后进入烘箱以固化胶水。最后,将带有顶层通孔器件以及顶层和底层表面贴装器件的电路板送入波峰焊接站,对通孔引线和底面表面贴装器件进行焊接。此前已在顶层焊接好的表面贴装器件在顶部保持原有焊点不变。

当印刷电路板仅包含表面贴装器件但两面都有时,有时会采用两步回流焊焊接工艺。首先使用高温焊膏将顶层的表面贴装器件固定到电路板上,然后将电路板送入高温回流焊炉。当顶层元器件牢固地固定后,将电路板翻转,再使用低温焊膏和回流焊工艺将底面表面贴装器件进行安装,如下所述。通常情况下,印刷电路板两面使用相同类型的焊膏。此时,设计者应将所有较重的元器件放置在印刷电路板的一面,该面将在第二步中组装,以防止它们在第二次回流焊过程中掉入回流焊炉内。

焊接工艺

焊接既用于将元器件物理连接到印刷电路板上,也用于在元器件引脚与印刷电路板走线之间提供电导率。

要使焊接过程成功,必须在焊料与基底材料(引线和走线)之间形成金属间化合物或合金。为了保护焊点区域免受氧化,新PCB板的接触区域会通过浸入焊料槽并进行热风整平,或采用化学镀镍等其他镀层工艺进行表面处理,如镀金或镀钯(库姆斯,2001,第32.1页)。在焊接之前或期间,待连接的表面会使用助焊剂进行清洁(去氧化),以便焊料能够流动并润湿表面。

焊接方法主要有两类:批量焊接(包括波峰焊、回流焊、汽相回流焊和传导回流焊)和定向能量焊接(包括热气焊、热压焊、激光焊、烙铁焊和pinpoint火炬焊)(参见库姆斯,2001,第43.10页;IPC-CM-770E,第34页)。本文仅简要讨论手工、波峰焊接和回流焊。

手工焊接

手工焊接广泛应用于各种场景,从完整的印刷电路板组装到简单的维修工作和补焊。目前有多种类型的手工焊接工具可供选择,包括但不限于热风笔、电烙铁和感应线圈。除了焊接速度较慢外,手工焊接最大的缺点是在操作过程中增加了静电放电的风险,以及由于对电路板和元器件进行局部加热而产生的热梯度。对于将要手工放置并焊接的元器件,在间距和方向上无需特殊的布局考虑,只需遵循下文所述的基本要求即可。然而,如果元器件布局能留出足够的操作空间,并且相同类型的元器件以一致的方向和排列方式布置,则有助于装配人员操作。

波峰焊接

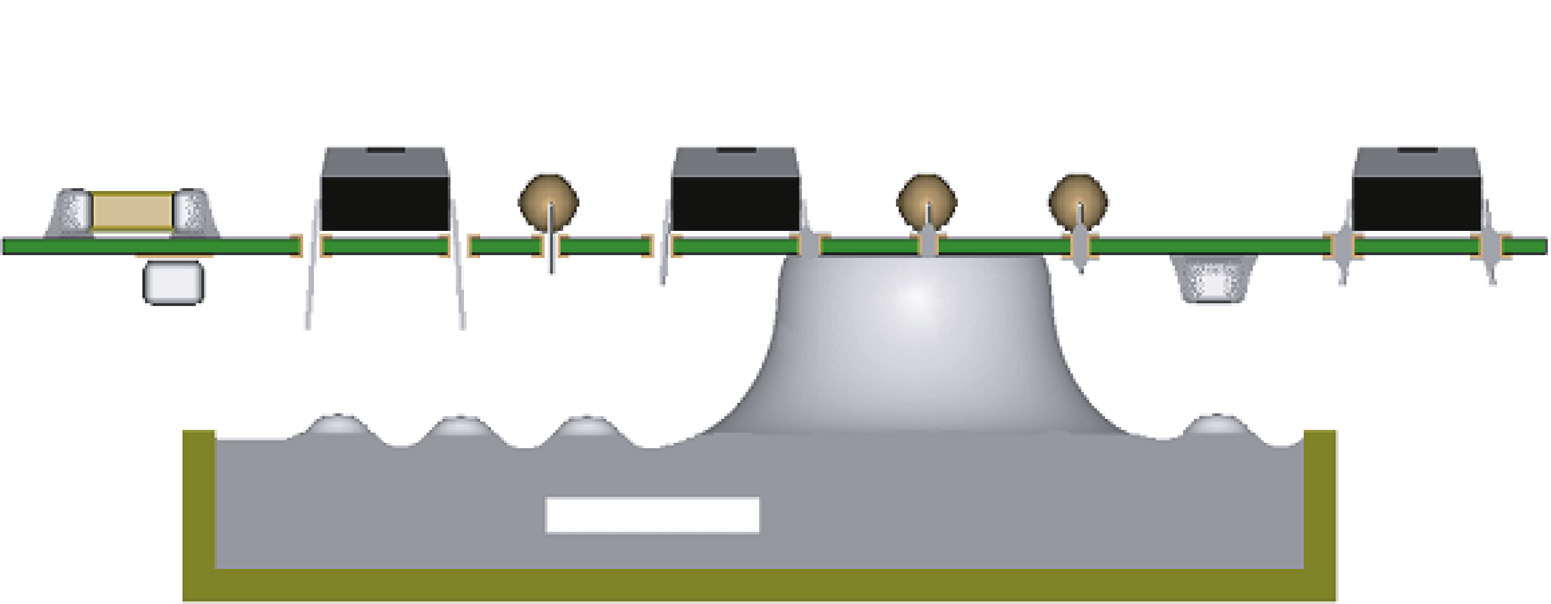

在波峰焊接过程中,电路板由传送带夹住其边缘,施加助焊剂并进行预热,如图5.1和5.2所示。传送带将电路板送过一个稳定的熔融焊料波峰,仅使电路板底面接触焊料。波峰焊接可用于通孔器件和表面贴装器件,但表面贴装器件优先采用回流焊。通孔元件安装在顶层,引线从电路板底面伸出,并预先施加助焊剂。当传送带将印刷电路板送入焊料波峰时,焊料通过毛细作用上升至孔壁,并在顶部和底部形成焊角。表面贴装器件则通过粘接到电路板上,施加助焊剂后进入波峰焊。非常小的元件或较大的钽电容器在波峰焊接中可能会出现问题。

小型元件在粘接工艺中容易出问题,因为在某些情况下胶点比元件本身更大,胶水可能溢出到焊盘上。大型表面贴装器件则会因热应力而导致元件开裂。

当表面贴装器件采用波峰焊接(即安装在电路板底面)时,设计者需要知道(或指定)电路板通过波峰的方向。元器件应按图5.3所示方式放置在电路板上,以避免较大元件遮挡较小元件造成小元件焊点不良,同时防止引线之间出现焊桥。

由于某些表面贴装器件的引脚间距较小,可能会导致焊桥。当每个引脚离开焊料波峰时,熔融焊料会试图降低其表面张力(如图5.3所示方向),从而倾向于从相邻引脚带走部分焊料。这会导致最后两排引脚出现问题,因为没有后续引脚将多余的焊料带走,可能导致侧面最后两个引脚被多余焊料桥接。一种最小化

防止桥接的方法是在SMD集成电路的尾边放置吸锡焊盘,如图5.3所示。吸锡焊盘是放置在最后焊盘之后的额外焊盘,用于将多余焊料从焊盘上引开。也可以通过将最后焊盘做得稍大一些,并比该器件上的常规焊盘向后延伸更远来形成吸锡焊盘。

如果表面贴装元件位于电路板顶部,并且在进行波峰焊接之前已进行回流焊接,则扇出过孔应远离焊盘,以防止焊料从表面贴装器件的焊盘处迁移到过孔中。当热量从焊料波峰通过过孔孔壁传导上来时,会导致焊料再次熔融,并通过毛细作用将焊料吸入过孔内部。建议的间距为$20密耳(IPC-7351B),即过孔边缘与焊盘边缘之间的间距。可以在PCB编辑器的扇出Router Parameters对话框中的“扇出”选项卡中设置默认间距。

有些电路板可能过大或过小而无法进行波峰焊接。大尺寸电路板在加热时会发生下垂,除非使用特殊的固定夹具。小尺寸电路板可能需要通过可分离连接点(标签式切割路径或V型槽)进行拼板,以便能够被自动化设备处理,而无需制作专用的电路板支架。

回流焊接

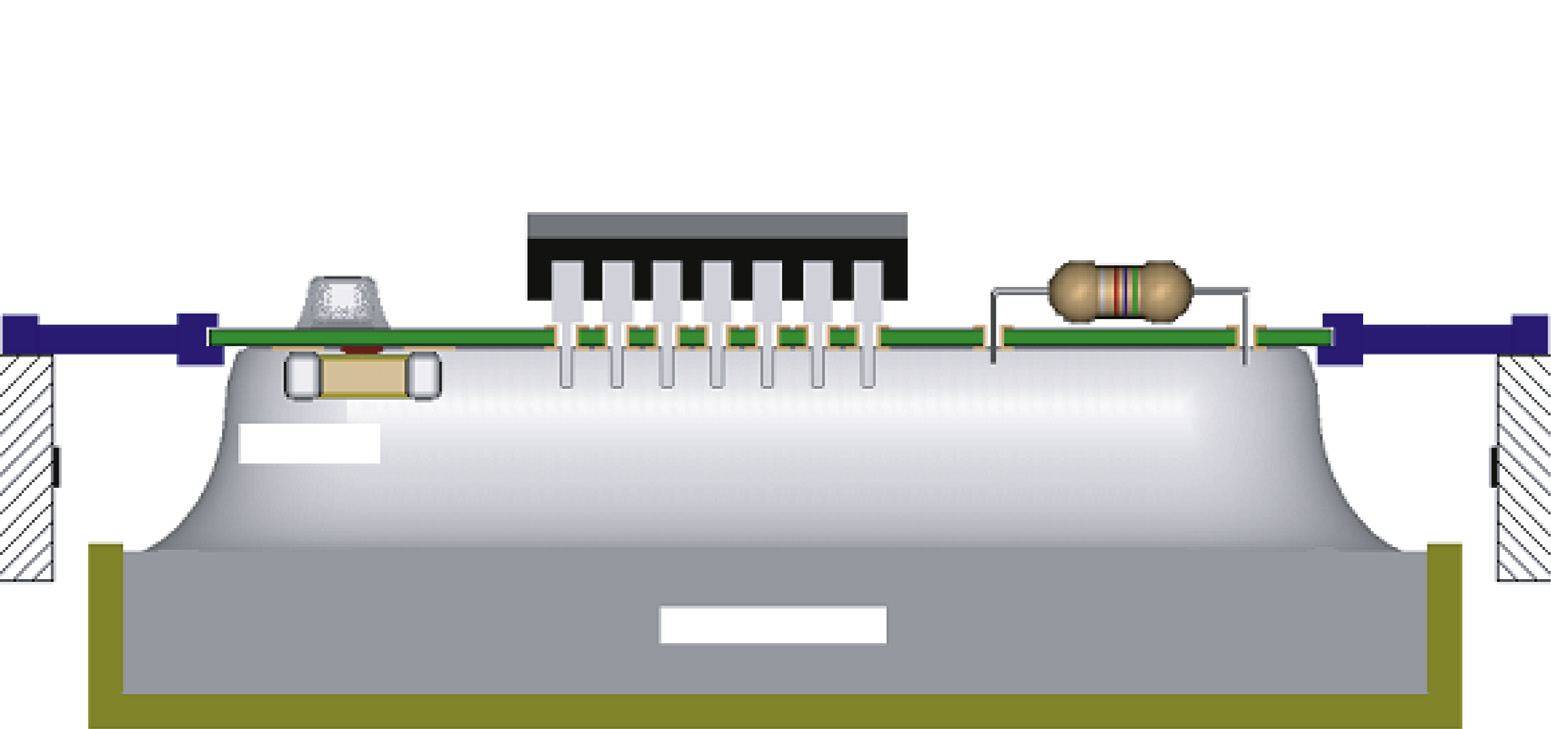

回流焊接有多种类型,但此处的讨论仅限于炉式回流焊接。回流焊接最常用于表面贴装器件,但通孔元件也可以通过这种方式进行焊接。

焊料 小偷

电路板运行方向

(称为 pin-in-paste 或 侵入式回流焊接)。图5.4 显示了回流焊炉的示意图。

焊膏(包含焊料和助焊剂的粘稠膏体)通过钢网涂覆在裸板上。元器件被放置到指定位置(通常由贴片机完成),使其引线位于焊膏中。组装好的电路板被放置在传送带上,送入温控炉中均匀加热。随着组装件温度升高,助焊剂被激活,焊料开始回流(熔化)。熔融焊料的表面张力有助于元器件自动对齐。然而,如果元器件未正确对齐,或热梯度导致各焊盘上的焊料未能同时熔化,则元件可能在一端竖起(称为立碑)。当组装件达到适当温度且焊料完全回流后,组装件离开烘箱并冷却,使焊料固化。

对于波峰焊和回流焊接,都需要选用可焊接的元器件。同时,应避免将所有热容量大的元器件放置在电路板的同一区域,因为这会导致电路板上出现热梯度,从而在较冷区域造成焊点形成不良(Coombs, 2001,第43.12页;关于电路板设计,参见Coombs, 2001,第43.25 页)。

元器件放置与方向指南

PCB组装包括裸板、已安装的元器件和连接器。电路板设计可能对元器件在电路板上的放置和安装难易程度以及最终产品的可靠性产生重大影响。

板级拓扑(类别和等级)、元器件技术(表面贴装器件或通孔)以及用于安装元器件的焊接方法(回流焊与波峰焊)在元器件于电路板上的放置和间距设计中起着重要作用。

元器件布局和方向取决于元件类型(通孔插装技术或表面贴装技术)、组装方法(手工、波峰焊接或回流焊)以及电气性能要求(电气性能在下文讨论)。这些因素本身并不使电路板功能更好,但它们确实使组装、检查、测试更加容易,

and troubleshoot. General guidelines 是 1. 元器件应整齐有序地放置,保持均匀的间距和对齐。2. 元器件的方向应使其边缘与电路板边缘平行(波峰焊接情况除外,如下所述)。3. 如果电路板采用机器焊接,通孔元件应尽可能安装在与焊料相对的一侧。4. 当在电路板两侧放置元器件以及混合使用通孔和表面贴装器件(SMD)技术时,需考虑可能需要多个组装阶段才能完成所有元器件的安装,这会增加成本和潜在故障点,并使返工更加困难。5. 不要将塑料有引线芯片载体或大尺寸钽电容器放在电路板的底层(即不要进行波峰焊接),因为它们可能因热应力而容易开裂。6. 应尽可能使用100密耳(2.5毫米)网格,但如果元件引脚不在标准网格上,则可根据需要使用20密耳(0.5毫米)网格甚至2密耳(0.05毫米)网格(IPC-2221B,第5.4.2节和第8.1.2节)。当使用公制网格时,应采用2.54毫米(0.100英寸)、1.27毫米(0.05英寸)、0.64毫米(0.025英寸)或0.50毫米(0.020英寸)的网格(IPC-7351B)。7. 对于需要进行针床测试的电路板,应使用0.100英寸(2.54毫米)网格。8. 在整个电路板上,有极性电容器和二极管的朝向应保持一致,以便于检查和测试。9. 当使用机器视觉辅助组装工艺时,应添加基准标记(全局和局部),以帮助元器件布局。10. 如果设计允许,在使用自动化焊接工艺时,连接器应放置在电路板的短边。11. 在元器件布局过程中,应在板边留出足够的空间,以便于电路板的操作并容纳安装硬件。12. 每引脚重量超过5.0克的元件,如果电路板将经历振动,则应提供机械支撑(IPC-2221B,第5.2.7节,第43页)。13. 在整个设计过程中,应考虑焊接过程和电路工作期间的热管理。14. 当电气考虑因素与机械考虑因素发生冲突时,通常优先考虑电气因素,除非会导致电路板的机械失效。15. 对于混合信号(模拟/数字)印制电路板,应将元器件分隔布置,以最小化开关噪声对模拟电路的影响。高功率电路也应与低功率和低噪声电路分隔开来。

通孔器件的元器件间距

以下表格提供了分立器件和集成电路通孔器件的最小推荐间距指南。

分立通孔器件

对于分立通孔器件,请参见表5.1和表5.2。

表5.1 分立轴向通孔器件的推荐最小间距 s.

| 参数 | Mils | 毫米 | PCB编辑器默认值 |

|---|---|---|---|

| 侧面到PCB边缘 (a) | a ≥ 75 | a ≥ 1.9 | 取决于焊盘到走线间距设置。无 DRC错误只要……就会发生放置轮廓未穿过封装保持在轮廓内 |

| 端到PCB边缘 (b) | b ≥ 90 | b ≥ 2.29 | — |

| 端到端并排 (D₁ < 100 mil, D₂ < 100 mil) | 100 | 2.54 | 如果出现DRC错误如果放置轮廓重叠 |

| 侧到端 (D₁ ≥ 100 mil, D₂ > D₁) | 95 + (1/2)D₁ | 2.41 + (1/2)D₁ | 发生DRC错误如果有放置轮廓重叠当一个或多个本体直径是 >100密尔 |

DRC,设计规则检查器;PCB,印刷电路板。参考:IPC-2221B,图 7-1。第 68 页。

表5.2 分立径向通孔器件的最小推荐间距 .

| 参数 | 密耳(毫米) | PCB编辑器默认值 |

|---|---|---|

| PCB边缘 (r) | r = 1/2 直径的设备或1/2高度,以较大者为准,且 r ≥ 60 密尔 (1.52 毫米) | 未发生DRC错误只要放置轮廓不交叉封装保持区轮廓 |

| 其他元器件 (r) | r = 1/2 直径的器件或1/2高度,以较高者为准更大 | 如果出现DRC错误放置轮廓重叠 |

设计规则检查,设计规则检查器;印刷电路板,印刷电路板。

集成电路通孔器件

对于集成电路通孔器件,请参见表5.3。

表 5.3 通孔安装的集成电路推荐的最小间距 .

| 参数 | Mils | 毫米 | PCB编辑器默认值 |

|---|---|---|---|

| 侧到侧 PCB edge (a) | a ≥ 100 | a ≥ 2.54 | 无DRC错误只要发生放置轮廓是否不违反元件保留区轮廓 |

| 端到 edge (b) | b ≥ 75 | b ≥ 1.91 | — |

| 端到端 | 200 | 5.08 | 无DRC错误只要发生放置轮廓不重叠。可能违反 IPC标准和不会导致设计规则检查错误 |

| 并排 | 100 | 2.54 | — |

设计规则检查,设计规则检查器;印刷电路板,印刷电路板。

混合分立和集成电路通孔器件

对于混合分立器件和集成电路通孔器件,请参见表5.4。

表5.4 通孔分立器件与集成电路之间的最小推荐间距

| 参数 | Mils | 毫米 | PCB编辑器默认值 |

|---|---|---|---|

| — | a - (D₁ ≤ 100) | b - (D₂ < 100) |

DRC,设计规则检查器;PCB,印刷电路板。

孔和跳线

对于孔和跳线,请参见表5.5。

表5.5 过孔和跳线的最小推荐间距。

| 参数 | 密耳(毫米) | PCB编辑器默认值 |

|---|---|---|

| 孔到孔 (镀层或非镀层) (b)(a) |

1. 以免违反焊盘间距规则

2. 使得残留覆铜板在孔之间为0.20密耳(0.5毫米)在孔之间 | 如果出现DRC错误焊盘间距规则被违反 |

| 跳线 (any direction) | 100密尔(2.54毫米) | 如果出现DRC错误焊盘间距规则被违反 |

设计规则检查,设计规则检查器;印刷电路板,印刷电路板。

表面贴装器件的元件间距

以下表格提供了分立和集成电路表面贴装器件的最小推荐间距指南。

分立表面贴装器件

参见表5.6 了解分立表面贴装器件。

表5.6 分立表面贴装器件的最小推荐间距 .

| 参数 | Mils | 毫米 | PCB编辑器设计规则检查 |

|---|---|---|---|

| 侧到侧 PCB edge 和端/到或 PCB edge (a) | 60 | 1.5 | 如果出现DRC错误焊盘间距轮到廓板小边于焊盘到走线间距规则或如果放置轮廓跨过元件保留区轮廓 |

| 端到端 | |||

| 侧和到/或侧 side (a) 尺寸0603或更大 | 20 | 0.50 | — |

| 小于0603 | 12 | 0.30 | — |

| 焊盘到过孔 | 20 | 0.50 | 如果出现DRC错误边缘之间的距离焊盘小于焊盘到‐焊盘间距规则 |

参考文献:IPC-2221B,第73页;IPC-7351B。表格3.5–3.8,图 3.15。设计规则检查,设计规则检查器。

集成电路表面贴装器件

对于集成电路表面贴装器件,请参见表 5.7。

表 5.7 集成电路表面贴装器件的推荐最小间距 s.

| 参数 | Mils | 毫米 | PCB编辑器默认值 |

|---|---|---|---|

| 元件侧到侧 PCB edge 和端/到或 PCB edge (a) | 60 | 1.5 | 如果出现DRC错误焊盘间距到板边轮廓小于小于焊盘到走线间距规则或如果放置轮廓跨过封装保持在轮廓内 |

| 端到端 (本体) | 20 | 0.50 | 由间距确定通过以下关系放置轮廓到焊盘和本体 DRC错误如果放置轮廓重叠 |

| 并排焊盘到 pad) | 20 | 0.50 | — |

设计规则检查,设计规则检查器;印刷电路板,印刷电路板。参考文献:IPC-2221B,第73页;IPC-7351B,表格3.2–3.22。

混合离散和集成电路表面贴装器件

对所涉及的元器件,采用上述间距规则中较大的值。

混合通孔器件和表面贴装器件的间距要求

对于所涉及的元器件,采用上述间距规则中较大的值(通常是通孔焊接间距)。

面向印制电路板可制造性的焊盘图形和焊盘堆栈设计

PCB编辑器软件包含了许多封装,但您最终需要自行创建封装。第8章,创建和编辑焊盘布局,介绍了用于设计封装的PCB编辑器工具,以下内容则描述了与封装设计相关的注意事项和行业标准。表面贴装器件(SMD)和通孔器件(THD)的封装设计有显著差异,但两者均需考虑印刷电路板可制造性和组装。

在PCB编辑器中,一个封装(焊盘图案)由焊盘堆栈、丝印元素和放置边界轮廓组成(具体信息请参见第8章:创建和编辑焊盘布局)。

PCB编辑器中存在一些基于元件边界与其他对象之间距离的有用元器件间距约束。封装设计(放置边界轮廓的尺寸)决定了间距,从而决定了在不产生设计规则检查(DRC)错误的情况下可能实现的最大板卡密度[。根据IPC标准,有若干间距建议,这些建议取决于板卡分类和封装类型。PCB编辑器中的封装不一定符合特定的IPC设计标准。因此,如果您需要生产C级板卡,则需要修改或创建符合特定指南的新封装。或者,如果您希望封装专门满足A级要求以提高良率和可靠性,则可能也需要设计特殊封装或修改现有封装。以下将讨论一些设计问题,并提供对行业标准的参考文献。

表面贴装器件的焊盘图形

当进行电路板布局时,如果所需的元件不在PCB编辑器的封装库中,您可以采取多种方法来创建一个。如果PCB编辑器中存在与所需封装类似的元件,但引脚数量不同,则可以将现有元件另存为新名称,并将其作为模板,根据需要添加引脚并调整放置轮廓和丝印层。如果PCB编辑器中没有可用作参考的封装,则下一步应查阅制造商的数据表,查看是否提供了推荐的焊盘图形。若数据表未提供必要信息,则可尝试使用名为PCB元件库专家的免费软件工具——IPC 焊盘图案查看器,从中获取设计参数。如果以上方法均不可行,则必须根据元件数据表中的封装信息或JEDEC封装标准从头开始设计。

元件数据表和JEDEC封装标准通常提供封装尺寸信息,但不提供PCB焊盘图案。IPC标准提供了相对于引线尺寸的焊盘图形尺寸指导,但需要进行额外计算才能在PCB编辑器中构建焊盘堆栈和封装。在PCB编辑器中设计封装时,您需要知道焊盘堆栈的尺寸以及焊盘中心之间的距离。IPC标准通常提供相对于焊盘边缘的间距信息。

因此,为了方便起见,需要一种将JEDEC封装尺寸直接转换为PCB编辑器封装尺寸的方法,同时保持符合IPC标准。

当查阅一个元器件的数据表时,所列尺寸通常是相对于封装而言的。图5.5展示了一个八引脚小外形集成电路(SOIC)的例子。元器件制造商还可能提供 JEDEC规格。图5.5。图5.6展示了小外形集成电路(SOIC)封装的JEDEC标准 MS‐012的一个示例。图5.6 经JEDEC许可转载。图5.6 经JEDEC许可转载。

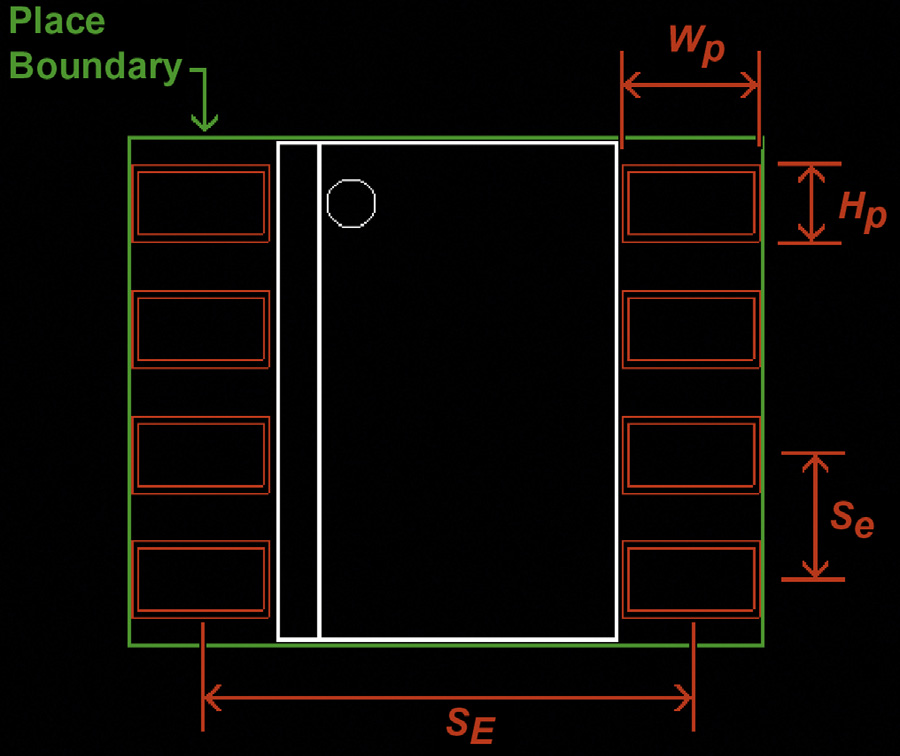

根据制造商的信息和/或标准,我们需要能够确定焊盘堆栈宽度和高度,以及图5.7所示x和y方向上的焊盘间距,以便在PCB编辑器中创建新的封装。

我们首先研究焊盘堆栈的设计,然后使用已确定的焊盘堆栈进行封装设计。

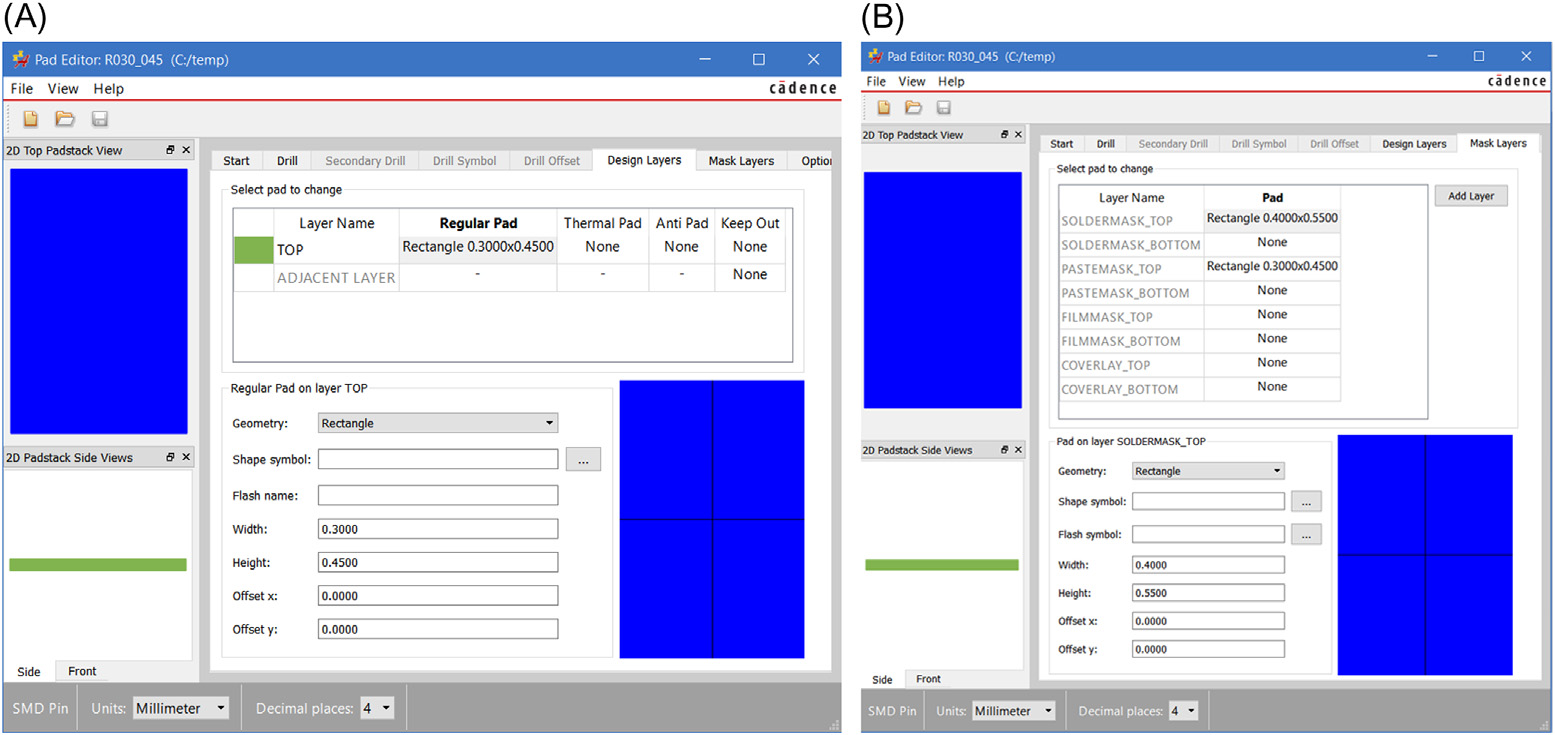

表面贴装器件焊盘堆栈设计

良好的焊盘堆栈有助于在元件端子(引线)与印刷电路板之间形成最佳的焊点。焊盘堆栈必须能够容纳元件尺寸变化、PCB制造公差、贴装公差以及焊锡焊角规格。通孔器件相对较大,因此对这些公差较为宽容,但表面贴装器件通常尺寸更小,因此对制造和贴装公差的变化更为敏感。IPC-7351B(取代了 IPC-SM-780/2)是表面贴装焊盘图形设计的行业标准,适用于焊盘堆栈和封装设计。

如图5.8所示,焊盘(焊盘堆栈)需要比元件引线更大,以形成可靠的焊点。所需的焊盘超尺寸在IPC-7351B(第 10–21页)中定义,其中术语J T定义了从焊盘末端到引线端部的距离,J H定义了从焊盘末端到引线跟部的距离,而J S定义了从焊盘侧面到引线侧面的距离。

值 JT、J H 和 JS取决于元件类型和所需的密度等级(A 至 C);标称值见表5.8–5.10。

在PCB编辑器中设计焊盘堆栈时,我们需要知道焊盘堆栈的宽度WP和焊盘堆栈的高度 HP,以便在PCB编辑器的工具中填入所需的数值(图5.9)。

表5.8 按封装类型划分的端部焊锡焊角标称值(JT)。标称密度

| 封装类型 | Mils | 毫米 |

|---|---|---|

| 鸥翼形(SOG) | 14 | 0.35 |

| J形引脚(SOJ) | 14 | 0.35 |

| 片式元件(0603及以上) | 14 | 0.35 |

| 片式元件(小于0603) | 4 | 0.10 |

| 小外形封装(SO) | 12 | 0.30 |

| 钽电容器 | 6 | 0.15 |

| 无引线芯片载体 | 22 | 0.55 |

| MELF | 16 | 0.40 |

| 对接接头 | 31 | 0.80 |

MELF,金属电极面。

表5.9 按封装类型划分的诺姆跟部焊锡焊角值 (JH)

| 封装类型 | Mils | 毫米 |

|---|---|---|

| 鸥翼形(SOG) | 14 | 0.35 |

| J形引脚(SOJ) | 28 | 0.70 |

| 小外形封装(SO) | 0 | 0.00 |

| 片式元件(全部) | 22 | 0.55 |

| 钽电容器 | 20 | 0.50 |

| MELF | 4 | 0.10 |

| 无引线芯片载体 | 6 | 0.15 |

| 对接接头 | 31 | 0.80 |

MELF,金属电极面。

表5.10 按封装类型划分的标称侧面焊锡焊角值(JS)。

| 封装类型 | Mils | 毫米 |

|---|---|---|

| 鸥翼形 (SOG) (间距大于0.625 mm) | 1 | 0.03 |

| 鸥翼形 (SOG) (间距小于0.625 mm) | 21 | 0.53 |

| J形引脚(SOJ) | 0 | 0.00 |

| 片式元件(0603及以上) | 22 | 0.55 |

| 片式元件(小于0603) | 22 | 0.55 |

| MELF | 8 | 0.20 |

| 小外形封装(SO) | 2 | 0.05 |

| 钽电容器 | 2 | 0.05 |

| 无引线芯片载体 | 2 | 0.05 |

| 对接接头 | 22 | 0.55 |

MELF,金属电极面。

使用元件数据表或JEDEC标准中的参数,公式(5.1)和(5.2) 可用于确定 WP 和 HP的最大尺寸。

$$

WP(\text{MAX}) = E_{\text{MIN}} - (E_{\text{MAX}} - 2L_{\text{MIN}}) + 2J_T + 2J_H + \sqrt{(E_{\text{TOL}}(\Delta))^2 + F^2 + P^2}

\quad (5.1)

$$

其中,WP(MAX)为最大焊盘宽度(见图5.7和图5.9);E(MIN和MAX)为根据 JEDEC尺寸规定的引线末端之间的距离(图5.6);ETOL(Δ)为根据JEDEC尺寸规定的E的公差,或由(EMAX−EMIN)计算得出(图5.6);L为根据JEDEC尺寸规定的将焊接至焊盘的引线长度(图5.6);JT和JH为焊锡焊角余量,如表5.8和表5.9中所述,源自IPC‐7351B;F为印制电路板制造公差(IPC‐2221B,通常为0.1 mm或4 密尔);P为贴片机的贴装公差(取决于设备,典型值为0.15 mm或6密尔);

$$

HP(\text{MAX}) = b_{\text{MIN}} + 2J_S + \sqrt{(b_{\text{TOL}}(\Delta))^2 + F^2 + P^2}

\quad (5.2)

$$

其中 HP(MAX)为最大焊盘高度(见 图5.7和图5.9),bMIN为最小引线宽度,J S为表 5.10中所述的焊锡焊角余量,Table5.10,bTOL(Δ)为根据JEDEC(固态技术协会)尺寸 或由(bMAX− b1MIN)计算得出的公差(图5.6),且F和 P如公式(5.1)所述。Eq.(5.1)。

这些公式源自 IPC-7351B 中的多个表格,但实际标准还包括舍入因子,而 公式(5.1)和 (5.2) 中未包含这些因素。表 5.8–5.10同样源自 IPC-7351B 中的多个表格,但其来源标准包含更高和更低的密度等级的附加数据,而此处仅包含标称密度等级。有关完整的尺寸考虑,请参阅源文件或下载IPC焊盘图案查看器(可在 www.pcblibraries.com/ 免费获取演示版本)。

焊盘设计完成后(即已计算出宽度和高度),请使用第8章,创建和编辑 焊盘布局中提供的步骤,通过Padstack Editor 创建焊盘。

表面贴装器件封装设计

焊盘堆栈设计完成后,需要将其准确定位以完成封装设计。 IPC-7351B定义焊盘图形参数的方式如 图5.10 所示,以八引脚SOIC为例。元件轮廓定义了集成电路的最外边界,包括封装边缘和引线末端。接下来,在器件周围定义一个庭院,该庭院包含本体和基本焊盘图形。庭院从元件轮廓向外调整,延伸并占用 PCB空间。庭院向外突出的量(称为 禁布区超出)决定了贴装时元器件之间的最小间距。禁布区超出越大,PCB的元器件密度越低。密度等级按A至C级分类,如 表5.11 所列的各种表面贴装器件封装(来自 IPC-7351B,表格 3‐2–3‐22)。

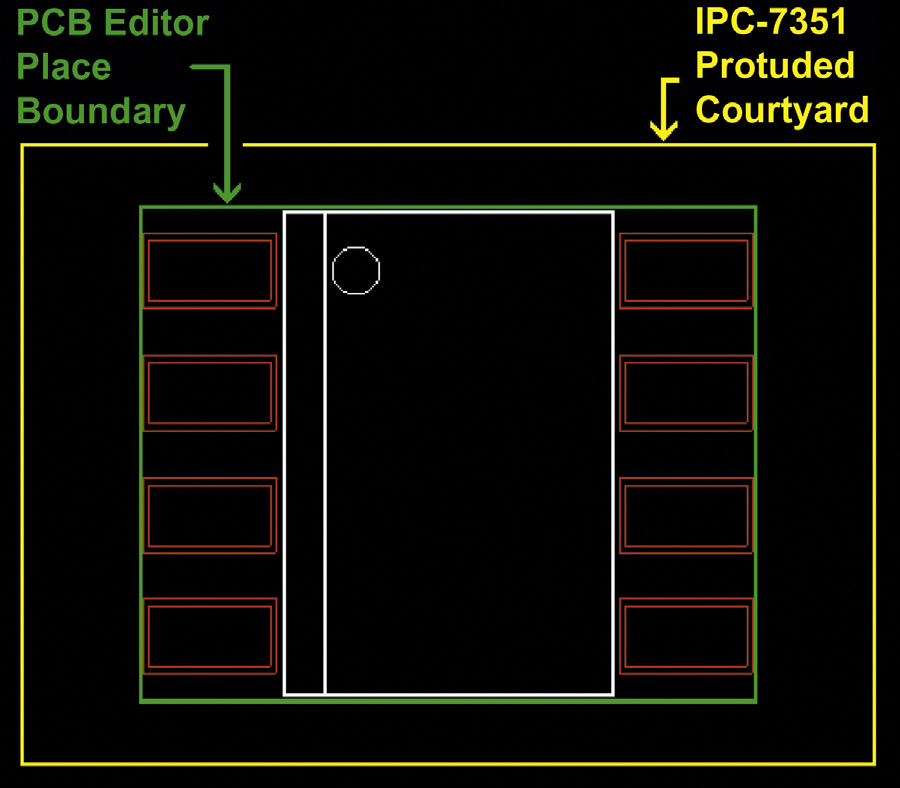

PCB编辑器在其SMD封装中未使用IPC-7351B标准所采用的庭院概念。 图5.11 显示了PCB编辑器中的八引脚SOIC放置边界轮廓叠加在IPC外扩的禁布区轮廓上的情况。请注意,PCB编辑器的放置边界轮廓未包含本体末端或引线周围的多余空间。

对于软件库中包含的大多数PCB编辑器封装,禁布区超出不存在。此外,在 OrCADs PCB编辑器的约束管理器中,您可设置一些封装间距约束,它们位于其/制造/面向装配的设计/间距/ 子文件夹中。功能更强大的约束表存在于更高级别的—Allegro Venture PCB编辑器中,本书不讨论该内容。如果您未在OrCAD PCB编辑器中设置“制造”约束,则设计规则检查仅会在放置轮廓交叉处查找违规情况。因此,要满足密度等级要求,您需要修改焊盘定义,或保守地设置放置网格,并参考表 5.6 和 5.7 手动逐一检查每个元件。

表5.11 不同密度等级下各种表面贴装器件的禁布区超出(突出)。

| 封装类型 | 密度等级A | 密度等级B | 密度等级C |

|---|---|---|---|

| Mils | 毫米 | Mils | |

| 鸥翼形(SOG) | 20 | 0.50 | 10 |

| J形引脚(SOJ) | 20 | 0.50 | 10 |

| 小外形封装(SO) | 20 | 0.50 | 10 |

| 片式元件(0603 及以上) | 20 | 0.50 | 10 |

| 钽电容器 | 20 | 0.50 | 10 |

| MELF | 20 | 0.50 | 10 |

| 芯片(元件小于0603) | 8 | 0.20 | 6 |

| 无引线芯片 | 59 | 1.50 | 31 |

| 对接接头 | 59 | 1.50 | 31 |

MELF,金属电极面。

通孔器件的焊盘图形

通孔器件的封装设计 通孔器件通常分为两类:轴向引线或径向引线。图5.12展示了一个径向引线电容器的示例。图5.12。此类器件的封装设计完全由器件本身的结构决定。显然,焊盘堆栈的位置必须与本体引出的引线位置一致。径向引线器件包括针栅阵列 以及许多分立晶体管器件,例如TO‐220和TO‐92封装。唯一的变量是针对引线直径的焊盘堆设计。焊盘堆设计将在下方描述。

轴向引线元器件的封装设计相较于径向引线器件具有更高的可变性,但IPC标准 (IPC-CM-770E,第11.1.8节)和文献中的其他来源对封装设计提供了通用指导。图5.13展示了轴向引线元件 (此处为碳膜电阻器)的设计参数。焊盘堆栈的位置取决于元件本体长度以及 引线弯曲位置(引线形式)。焊盘堆栈之间的最小所需距离通过以下公式计算:

$$

L_P = L_B + 2(R + L_A);

\quad (5.3)

$$

其中 $L_P$ 为焊盘间距(中心到中心),$L_B$ 为元件本体长度,$R$ 为弯曲半径余量 (从表5.12中查得),而 $L_A$ (从表5.12中查得)为从元件本体末端到弯折起始处的引线延伸长度。注意R和LA取决于引线直径DL,且LE是LA与R之和。焊盘堆栈计算将在下一节中描述。在计算出该最小焊盘堆栈间距后,应将焊盘堆栈放置在最近的标准网格位置上。标准网格间距详见元器件放置与方向指南。大多数情况下使用100密耳网格。除非元件具有机械支撑,否则两个引线的总长度不应超过1英寸(25毫米)。

通孔器件的焊盘堆设计

PCB制造中最薄弱的环节是金属化通孔(PTH),原因在于对准误差、纵横比、电镀等。可能的故障点是露铜由于对准偏差以及在焊接工艺(组装和返工)过程中因热应力和循环导致的环形铜环控制问题和开路。但如果我们遵循标准和制造商的设计指南,通常就不会遇到太大问题。

在设计通孔元件的金属化孔时,我们需要考虑引线直径/钻孔直径关系、 PCB厚度/钻孔直径关系(纵横比)、孔周围铜环的宽度(环形铜环)、平面层与金属化孔之间的间距,以及电路板制造商的能力(参见图4.1和图4.2)。此处参考库姆斯和IPC标准,以定义Padstack Editor中金属化孔的设计流程。

孔与引线比例

金属化孔的尺寸应足够大,以便引线能轻松插入孔内,但又不能过大,以免在焊接过程中影响毛细作用。确定金属化孔所需孔径与将要焊接的引线直径之间关系有两种方法。第一种方法源自IPC-2221B和库姆斯(第42.2.1节,第 42.3页)的综合。该方法考虑了电镀厚度(假设值或已知值),并允许设计者定义一个公差系数。此方法产生的引线与金属化孔之间的间距随引线直径而变化。钻头直径通过以下公式计算:

$$

D_H = (D_L + 2T_P) \times k;

\quad (5.4)

$$

其中,$D_H$ 是钻孔工具的直径(单位为 Padstack Editor),$D_L$ 是引线直径 (依据元件的数据表或实测值),$T_P$ 是孔内电镀层的厚度(若未知,可采用 $T_P=1$ 密尔),$k$ 为用户自定义公差系数,取值范围为 $1.05 ≤ k ≤ 3.0$(推荐使用 $1.5$)。成品孔直径(单位为 Padstack Editor)比 $D_H$ 小 $2 × T_P$。

例如,如果元件引脚的直径$D_L$为32密尔,则钻头直径应为$D_H=(32 + 2 × 1) × 1.5 = 51$密尔,而成品孔直径为49密尔。除变量k外,此方法明确且易于使用。然而,随着引脚直径增大,引脚与孔之间的间距也会变宽,到一定程度时,间距可能过大,导致无法实现良好的毛细作用。这种情况发生的具体条件在文献中尚未明确记载。

第二种方法是使用一个查找表,其中成品钻孔孔径取决于引线直径和所需的可制造性等级(A–C),如表5.13 所示(源自 IPC-2222A,表9‐5,第25页)。

例如,使用此方法时,如果我们采用相同的32密耳引线直径,并且数据表规定引线直径有10%的公差,则最大引线直径为35.2密尔,且最小值为28.8密尔。如果我们希望达到可制造性等级A,则孔径应在45.2密尔( 35.2 + 10)至56.8密尔(28.8 + 28)之间。

如果你在网上搜索,可以找到其他用于计算“合适”的孔与引线比例的算法。选择哪种方法由你决定。此处列出的两种方法源自IPC标准及其他来源,但并非强制性要求。

金属化孔焊盘尺寸(环形铜环宽度)

确定钻孔尺寸后,下一步是确定焊盘(也称为焊盘)的直径。焊盘直径与钻孔直径之间的差值称为环形铜环。这是与元件引脚形成焊点的铜区域。焊盘直径越大,焊点就越大—但有一定限度。过大的焊盘并不一定能形成更好的焊点,反而会增加形成焊点所需的热量。过小的焊盘可能导致焊点强度不足,并且焊盘容易因热或机械应力而损坏,从电路板上剥离。根据IPC-2221B(第 96页)推荐的焊盘直径可通过以下公式计算:

$$

D_P = a + 2b + c;

\quad (5.5)

$$

其中 $D_P$ 为焊盘直径(见 图5.14),$a$ 为成品孔尺寸($a= D_H - 2T_P$ 来自 图 5.14),$b$ 为 表5.14中的最小环形焊盘要求(IPC-2221B,表9‐2),以及 $c$ 为 表5.15中的标准制造公差(IPC-2221B,表9‐1)。

例如,如果我们使用上述示例中的32密耳引线(孔径为50密耳),并计算外层焊盘的尺寸(TOP或 BOTTOM在PadstackEditor中),且要求达到A级可制造性水平,则焊盘尺寸应为$(50 - 2 × 1) + (2 × 2) + 16 = 68$ mil。

表5.13 按可制造性等级划分的孔与引线尺寸关系。

| 级别 A | 级别 B | C级 | |

|---|---|---|---|

| 孔径 Mils | 毫米 | Mils | |

| 最小值 = max 引线直径 + | 10 | 0.25 | 8 |

| 最大 = 最小值 引线长度(L) 直径 + | 28 | 0.70 | 28 |

表5.14 内外环形焊盘要求。

| 内层 | 外层 | |

|---|---|---|

| Mils | 1 | 2 |

| 毫米 | 0.025 | 0.05 |

表5.15 金属化通孔设计的标准制造公差。

| 级别 A | 级别 B | C级 | |

|---|---|---|---|

| Mils | 16 | 10 | 8 |

| 毫米 | 0.40 | 0.25 | 0.20 |

平面层与金属化通孔之间的间距

通孔和过孔通常在所有层上都有焊盘,即使该层没有与之连接;这些被称为非功能焊盘。IPC-2222A(第9.1.4节,第23页)指出,当可能时,内层应使用非功能焊盘,但如果电路板超过10层,则并非每层都必须设置非功能焊盘,且平面层上也不要求设置非功能焊盘。当过孔或金属化孔穿过平面层时,为了制造公差的需要,防止电镀液从通孔芯吸进入层压板(导致与内层平面发生内部短路),并满足耐压(绝缘)要求,平面与电镀孔或其非功能焊盘之间必须保留最小间距。

IPC-2221B(第6.3.1节,第57页)指出,线间间距要求(另见本文第6章:信号完整性用印制电路板设计中的表6.8)适用于平面边缘与金属化孔或其焊盘之间的间距。此外,根据IPC-2222B(第22页,图9‐1),平面边缘与内层非功能焊盘或电镀孔边缘之间的最小间距应至少为10密耳(0.25毫米),即 Clearance直径应比钻孔直径大20密耳(0.51毫米)。

通常情况下,PCB编辑器中的焊盘堆栈在平面层上不包含非功能焊盘,因此Clearance直径应比钻孔直径大20密耳(0.51毫米)(即平面的边缘距离电镀通孔孔壁的边缘为10密耳)。未按此方式设计的焊盘堆栈可能在电路板制造或运行过程中引发问题。

如果焊盘(pad)按照公式(5.5) 设计,并且使用孔与平面层之间的最小间距,则Clearance直径通常会比焊盘大几个密尔。然而,如果焊盘大于 Clearance直径,则即使间距(尺寸d)满足IPC标准,焊盘与平面层之间也会出现重叠,如图5.15所示。这种情况应予以避免,因为焊盘与平面层之间会产生电容耦合,这可能会改变走线的特性阻抗,并在高频时引起串扰问题。特性阻抗在第6章《印刷电路板信号完整性设计》中有更详细的描述。

另一点需要注意的是,Clearance直径应尽可能小,因为当多个引脚靠得很近时(如板对板或插座连接器中),过大的Clearance会在地(返回)平面形成较大的开槽,当信号线在引脚之间穿过时,可能对高速数字和高频模拟电路造成问题。这会迫使地平面上的返回信号绕行地平面中的开槽,从而增加电路的回路电感。我们将在第6章《PCB制造公差(F)》中关于信号完整性设计的电路板设计部分进一步探讨回路电感和地平面。

阻焊层和焊膏尺寸

阻焊层开窗通常比焊盘(焊盘)直径大 PadstackEditor。PCB制造商有时会要求特定的放大开窗尺寸(5密尔并不少见)。如果他们没有自动为您调整尺寸,则您需要在创建PCB光绘文件之前修改阻焊层开窗尺寸。

焊膏的尺寸通常与外层焊盘(TOP和BOTTOM层)相同。默认库中自带的大多数PCB编辑器封装未定义焊膏。如果需要焊膏定义,请确保根据具体的组装需求正确指定。

39

39

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?