关于AHB总线的小结:1,流水线2,数据的保持问题

https://blog.youkuaiyun.com/ivy_reny/article/details/78144785?locationNum=3&fps=1

http://blog.163.com/qixin_william/blog/static/240217035201491133626819/这里写的很好

一个基于AHB总线的Slave:

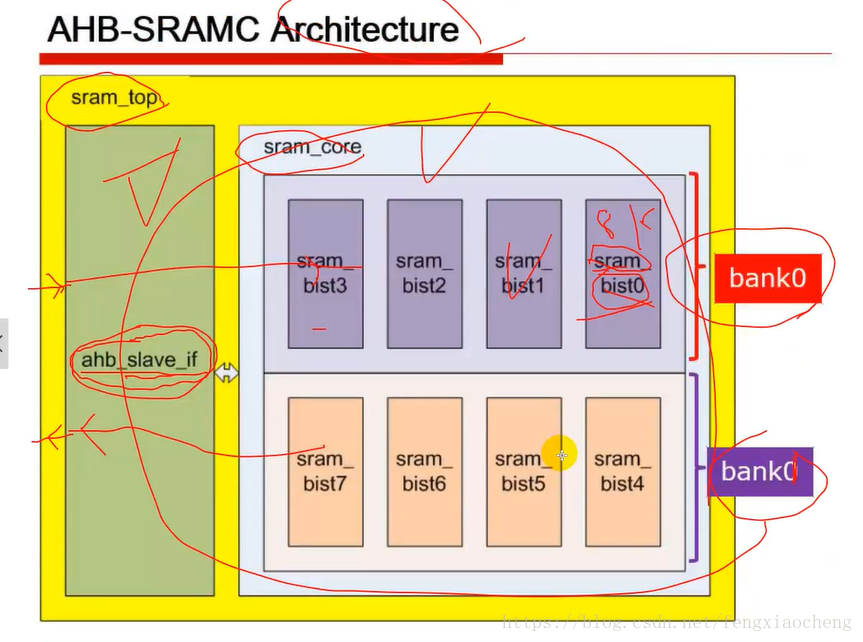

总的架构:一个ahb_slave_if,一个sram_core(有两个bank,每个bank4个SRAM—bist)

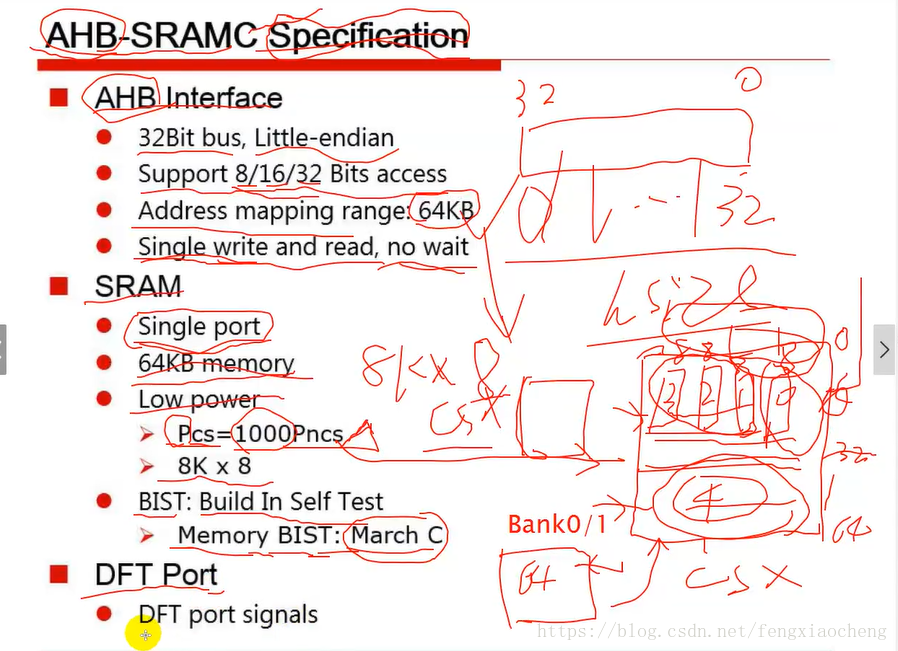

具体的一些功能或者接口描述:

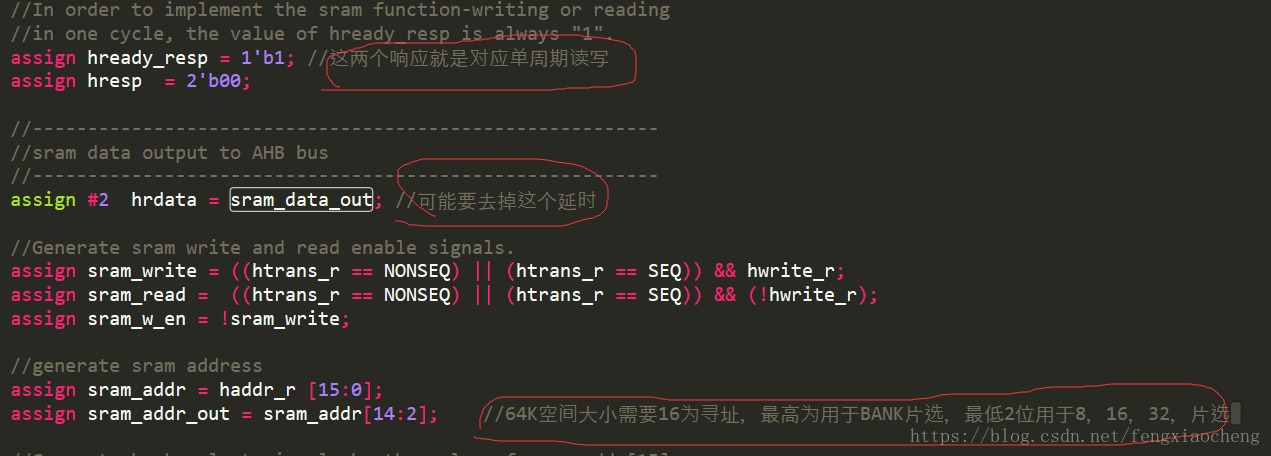

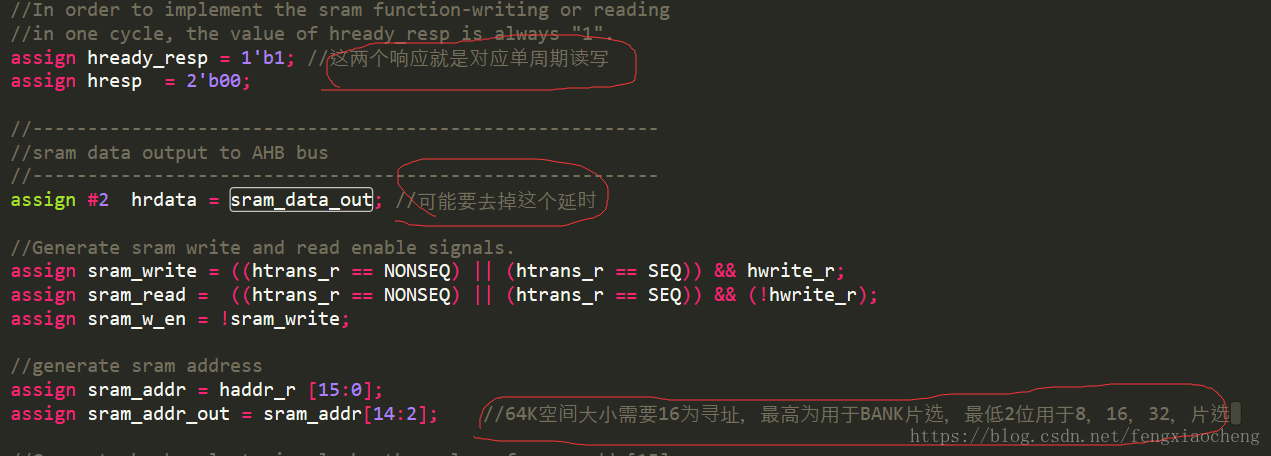

32位总线,支持8/16/32位数据读写,SRAM空间大小是64KB,单周期读写(本设计不支持wait,即hready都拉高)

SRAM是一个单端口(FiFo是双端口,这里就是一边读写就行,就使用单端口),大小是8*8K,支持低功耗(工作状态的功耗是low power standby 状态的几百倍),支持BIST

也预留了DFT port端口,可以有三种Model:function,BIST,DFT

输入信号:一个片选信号HSELx,address和几个控制信号HWRITE,HSIZE,HTRANS,HBURST; 数据date,复位reset,时钟clock,(一般也会有来至master的hready-in信号),最下面的两个很少用。

输出信号:传输完成拉高HREADY,传输状态HRESP(okay,error,retry,split),HRDATA

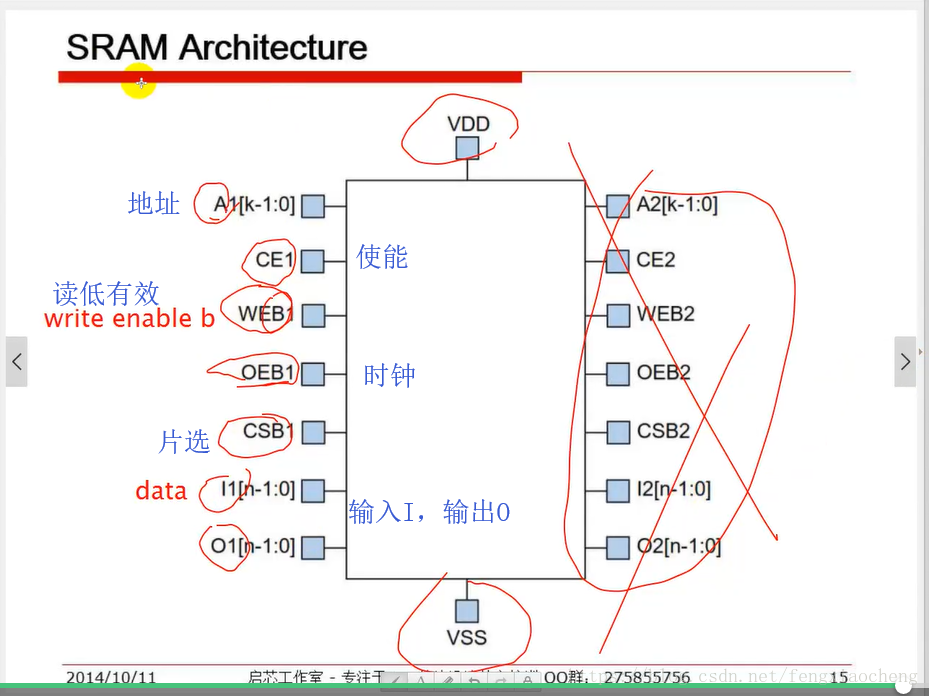

一个SRAM的端口:

一个

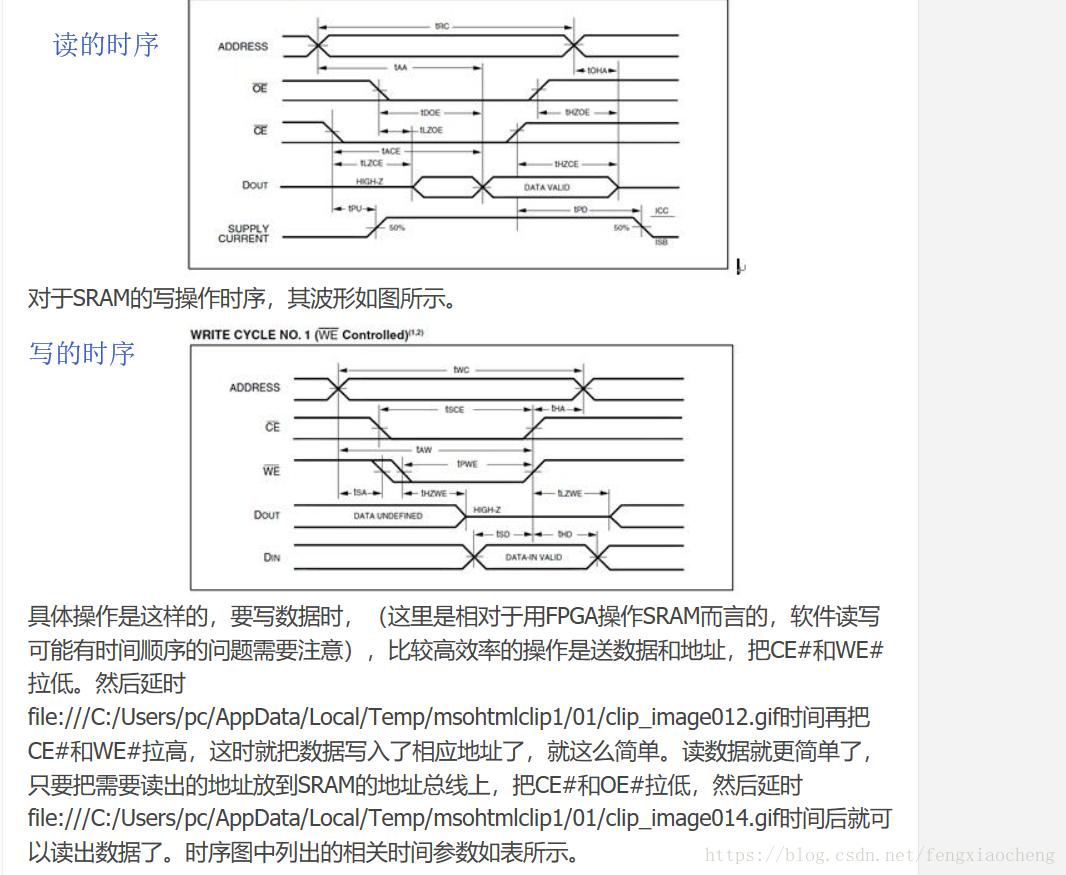

简单的SRAM读写时序:是一拍的,地址数据控制都在一个T下完成。

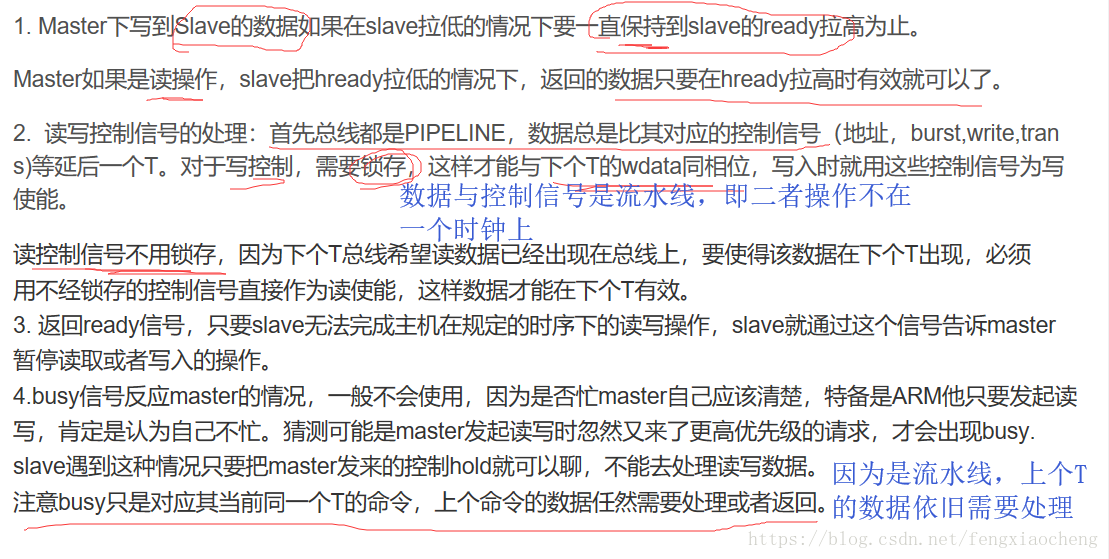

RTL里需要注意的:

3477

3477

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?