背景

经常需要使用mlxconfig来配置某个静态参数。 这些配置的作用mlxconfig提供了一个命令来查看作用

命令

mlxconfig -d 01:00.0 show_confs # 查看config

mlxconfig -d 01:00.0 i #简洁方法

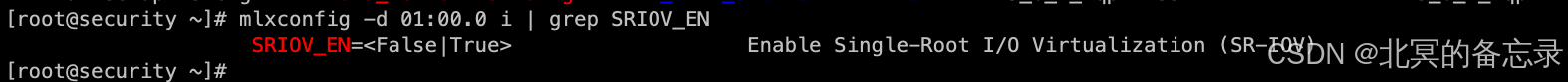

mlxconfig -d 01:00.0 i | grep SRIOV_EN # 只查看某个配置的作用

实操

查看某个配置

查看全量配置

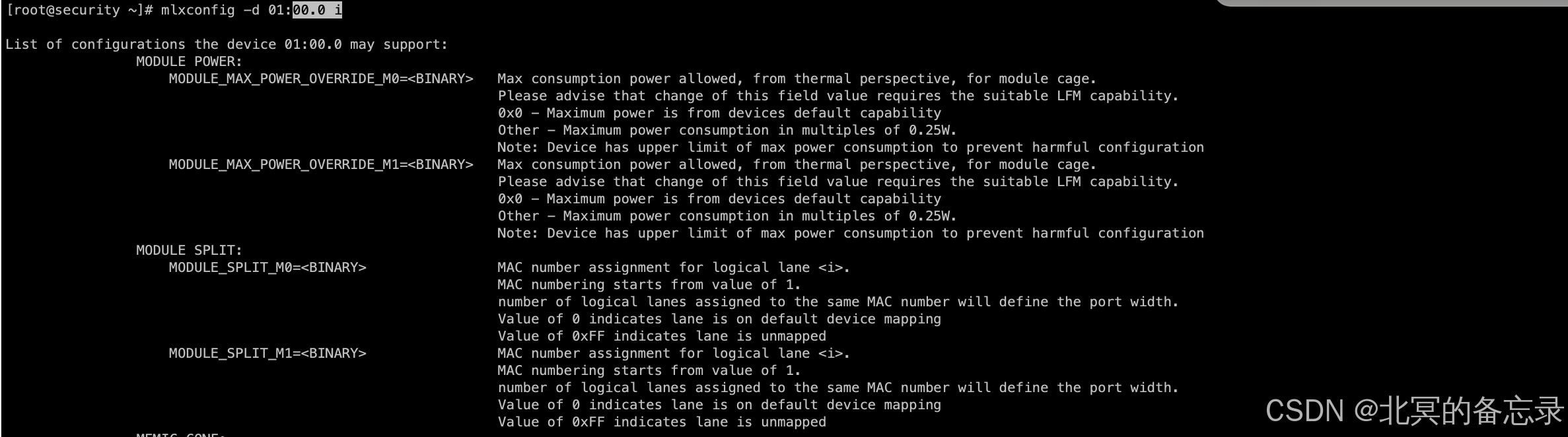

i方式

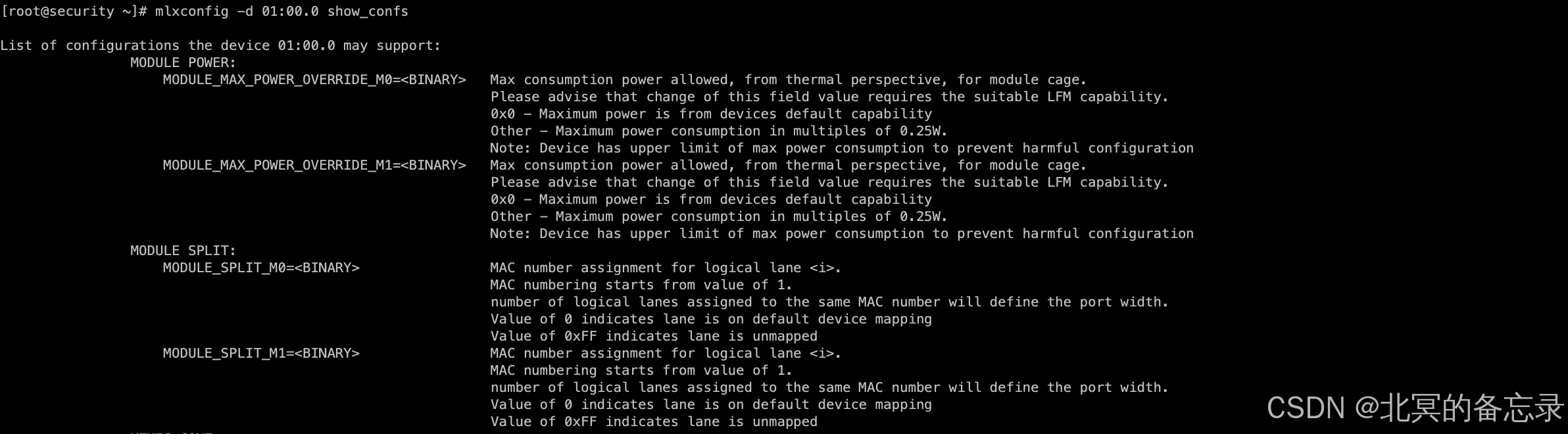

show_confs方式

全量mlxconfig可供查询的配置

当前是基于cx5的信息

[root@security ~]# mlxconfig -d 01:00.0 i

List of configurations the device 01:00.0 may support:

MODULE POWER:

MODULE_MAX_POWER_OVERRIDE_M0=<BINARY> Max consumption power allowed, from thermal perspective, for module cage.

Please advise that change of this field value requires the suitable LFM capability.

0x0 - Maximum power is from devices default capability

Other - Maximum power consumption in multiples of 0.25W.

Note: Device has upper limit of max power consumption to prevent harmful configuration

MODULE_MAX_POWER_OVERRIDE_M1=<BINARY> Max consumption power allowed, from thermal perspective, for module cage.

Please advise that change of this field value requires the suitable LFM capability.

0x0 - Maximum power is from devices default capability

Other - Maximum power consumption in multiples of 0.25W.

Note: Device has upper limit of max power consumption to prevent harmful configuration

MODULE SPLIT:

MODULE_SPLIT_M0=<BINARY> MAC number assignment for logical lane <i>.

MAC numbering starts from value of 1.

number of logical lanes assigned to the same MAC number will define the port width.

Value of 0 indicates lane is on default device mapping

Value of 0xFF indicates lane is unmapped

MODULE_SPLIT_M1=<BINARY> MAC number assignment for logical lane <i>.

MAC numbering starts from value of 1.

number of logical lanes assigned to the same MAC number will define the port width.

Value of 0 indicates lane is on default device mapping

Value of 0xFF indicates lane is unmapped

MEMIC CONF:

MEMIC_ATOMIC=<DEVICE_DEFAULT|MEMIC_ATOMIC_DISABLE|MEMIC_ATOMIC_ENABLE>Indicates whether Atomic operations address range is supported for MEMIC. When accessing this range Read and Write operation are translated into 'Atomic test-and-set' and 'Atomic add' respectively.

0x0: DEVICE_DEFAULT

0x1: MEMIC_ATOMIC_DISABLE

0x2: MEMIC_ATOMIC_ENABLE

other values are reserved

MEMIC_ATOMIC_ENDIANESS=<DEVICE_DEFAULT|MEMIC_ATOMIC_ENDIANNESS_BIG|MEMIC_ATOMIC_ENDIANNESS_LITTLE>Indicates what is the endianness of MEMIC for DM operations.

This configuration does not apply to Internal CPU.

0x0: DEVICE_DEFAULT

0x1: MEMIC_ATOMIC_ENDIANNESS_BIG

0x2: MEMIC_ATOMIC_ENDIANNESS_LITTLE

MEMIC_BAR_SIZE=<NUM> The amount of BAR size assigned for MEMIC. The size in bytes is memic_size_limit*2^log_memic_bar_size.

When activating MEMIC Atomic access by MEMIC_ATOMIC, the allocated BAR size for MEMIC is doubled.

MEMIC_SIZE_LIMIT=<DISABLED|_1024KB|_256KB|_512KB>The maximum amount of internal device memory that can be consumed by the MEMIC application.

0x0: DISABLED

0x1: _256KB

0x2: _512KB

0x3: _1024KB

HOST CHAINING CONF:

HOST_CHAINING_CACHE_DISABLE=<False|True>When TRUE, host chaining data is not cached on the device.

HOST_CHAINING_DESCRIPTORS=<NUM> Log(base 2) of the number of packets descriptors that should be allocated by the host for host chaining for a given IEEE802.1p priority i.

0 means that no descriptors are allocated for this priority and traffic with this priority will be dropped.

HOST_CHAINING_MODE=<BASIC|DISABLED> Enable and select host-chaining mode.

0x0: DISABLED

0x1: BASIC

other values are reserved

HOST_CHAINING_TOTAL_BUFFER_SIZE=<NUM> Log(base 2) of the buffer size (in bytes) allocated for host chaining for a given IEEE802.1p priority i.

0 means no buffer for this priority and traffic with this priority will be dropped.

FPGA CONF:

FPGA_AUTO_RELOAD=<False|True> When set, the FPGA bitstream is reloaded from flash as part of the ConnectX boot sequence.

INTERNAL CPU CONF:

INTERNAL_CPU_ESWITCH_MANAGER=<ECPF|EXT_HOST_PF>Defines the owner of Eth Embedded Switch responsibilities

0x0: ECPF

0x1: EXT_HOST_PF

Valid for INTERNAL_CPU_MODEL = EMBEDDED_CPU

INTERNAL_CPU_IB_VPORT0=<ECPF|EXT_HOST_PF>Defines the owner of IB Vport0 responsibilities

0x0: ECPF

0x1: EXT_HOST_PF

INTERNAL_CPU_MODEL=<EMBEDDED_CPU|SEPARATED_HOST>Select the model for the Internal CPU

0x0: SEPARATED_HOST - Supported only when NV_INTERNAL_CPU_CAP.separate_host_model_supported==1.

0x1: EMBEDDED_CPU - Supported only when NV_INTERNAL_CPU_CAP.embedded_cpu_model_supported==1.

other values are reserved

This NVCONFIG parameter can only be configured from the embedded CPU.

INTERNAL_CPU_OFFLOAD_ENGINE=<DISABLED|ENABLED>Defines whether the Internal CPU is used as an offload engine

0x0: ENABLED

0x1: DISABLED

Valid for INTERNAL_CPU_MODEL = EMBEDDED_CPU

INTERNAL_CPU_PAGE_SUPPLIER=<ECPF|EXT_HOST_PF>Defines the owner of providing ICM pages to the external host functions

0x0: ECPF

0x1: EXT_HOST_PF

Valid for INTERNAL_CPU_MODEL = EMBEDDED_CPU

FLEX PARSER CONF:

FLEX_IPV4_OVER_VXLAN_PORT=<NUM> The UDP port for incoming IPoVxLAN traffic (non-standard).

When set, also affects flex_vxlan_gpe_supported when enabled on same profile.

FLEX_PARSER_PROFILE_ENABLE=<NUM> Indicates which flex parser profile to enable. Each profile supports a set of protocols. The support indication and the set of protocols supported by profile 'x' reported in NC_FLEX_PARSER_CAP.flex_parser_profile_x_supported.

PROG_PARSE_GRAPH=<False|True> When TRUE, the device parse graph may be dynamically configured. The amount of programmable resources is reduced according to the amount of protocols already supported by FLEX_PARSER_PROFILE_ENABLE.

ROCE 1 5 CONF:

ROCE_NEXT_PROTOCOL=<NUM> The next protocol value set in the IPv4/IPv6 packets for RoCE v1.5.

INTERNAL HAIRPIN CONF:

ESWITCH_HAIRPIN_DESCRIPTORS=<NUM> Log(base 2) of the number of packets descriptors allocated internally for hairpin for a given IEEE802.1p priority i.

0 means that no descriptors are allocated for this priority and traffic with this priority will be dropped.

ESWITCH_HAIRPIN_TOT_BUFFER_SIZE=<NUM> Log(base 2) of the buffer size (in bytes) allocated internally for hairpin for a given IEEE802.1p priority i.

0 means no buffer for this priority and traffic with this priority will be dropped.

DPA AUTH:

DPA_AUTHENTICATION=<False|True> When TRUE, DPA code is authenticated before executed.

GLOBAL PCI CONF:

DPU_RESET_NOTIFICATION_ENABLED=<DISABLED|ENABLED>When set, the NIC can report PCIe errors through AER cap to all hosts it is connected to on DPU reset\panic. (If no error reporting is enabled, the DPU will not report any error.)

0x0: DISABLED

0x1: ENABLED

FPP_EN=<False|True> When this bit is cleared, the device exposes a single PCI function for both ports. When set, the device exposes one or more PCI functions for each port (this is the only mode supported by ConnectX-4 devices).

HIDE_PORT2_PF=<False|True> When TRUE, the device will not advertise the PFs associated with port 2, except for the Embedded CPU (ECPF) if exists. This configuration is available only when NV_PCI_CONF.ADVANCED_PCI_SETTINGS is TRUE.

INTERNAL_CPU_RSHIM=<DISABLED|ENABLED> Defines whether an RSHIM function will be exposed (when available) to the external host.

0x0: ENABLED

0x1: DISABLED

NON_PREFETCHABLE_PF_BAR=<False|True> When set, the PF BAR prefetchable bit is cleared.

Note: PCI switches and operation systems have dedicated quotas for non-prefetchable memory, hence, you may need to decrease log_pf_uar_bar_size to enable this feature.

NUM_OF_PF=<NUM> Total number of Network PCIe functions (PFs) exposed by the device. In case the number of PFs cannot be equally distributed between the number of ports, the remainder of PFs will be distribute between the ports with the lower numbers. For a Multi-Host device, this number is applied to each host individually.

Value 0 is only supported when an Emulated PCI Switch is present or another type of PF (e.g. emulated device).

NUM_OF_VFS=<NUM> The total number of Virtual Functions (VFs) that can be supported, for each PF.

Valid when PF_NUM_OF_VF_VALID is FALSE

NUM_PF_MSIX=<NUM> Number of MSI-X vectors and EQs per PF.

NUM_PF_MSIX_VALID=<False|True> When set, the num_pf_msix field is valid.

When cleared, the number of PF MSI-X is defined by PER_PF_NUM_MSIX

NUM_VF_MSIX=<NUM> Number of MSI-X vectors and EQs per VF.

PARTIAL_WRITE_CACHE_MODE=<ADDRESS_BASED|DEVICE_DEFAULT|DISABLED|FUNCTION_BASED>Specifies the mode of operation for PCI write cache, for partial cacheline writes:

0x0: DEVICE_DEFAULT - device default configuration

0x1: DISABLED

0x2: FUNCTION_BASED

0x3: ADDRESS_BASED

other values are reserved

PER_PF_NUM_SF=<False|True> When TRUE, the SFs configuration is defined by TOTAL_SF and SF_BAR_SIZE for each PF individually. In case they are not defined for a PF, device defaults are used.

When FALSE, the SFs configuration is defined by device defaults.

Valid only when PF_BAR2_ENABLE is set to FALSE.

PER_PF_NUM_VF_MSIX=<False|True> When set to TRUE, the VF MSI-X configuration is defined by NUM_VF_MSIX for each PF individually. In case they are not defined for a PF, device defaults are used for that PF.

When set to FALSE, the MSI-X configuration is defined by

NUM_VF_MSIX for all PFs.

PF_BAR2_ENABLE=<False|True> When TRUE, BAR2 is exposed on all external host PFs (but not on the embedded ARM PFs/ECPFs). The BAR2 size is defined by the log_pf_bar2_size.

When FALSE, the SFs and BAR2 configurations are defined by PER_PF_NUM_SF

PF_BAR2_SIZE=<NUM> Log (base 2) of the size of a PF's BAR2 size, given in MB.

PF_LOG_BAR_SIZE=<NUM> Log 2 of the size of a PF"s UAR BAR in MBs.

PF_NUM_OF_VF_VALID=<False|True> When TRUE, the number of VFs is defined for each networking PF individually in PF_NUM_OF_VF. In case they are not defined for a PF, device defaults are used instead.

When FALSE, the number of VFs is defined symmetrically for all PFs by NUM_OF_VFS

PF_NUM_PF_MSIX_VALID=<False|True> When TRUE, the MSI-X configuration is defined by PF_NUM_PF_MSIX for each PF individually. In case they are not defined for a PF, device defaults are used.

When FALSE, the MSI-X configuration is defined by device defaults

Valid only when NUM_PF_MSIX_VALID is set to FALSE.

SRIOV_EN=<False|True> Enable Single-Root I/O Virtualization (SR-IOV)

STRICT_VF_MSIX_NUM=<False|True> When set to TRUE, num_vf_msix defines a strict number (no calculation and roundup).

VF_LOG_BAR_SIZE=<NUM> Log 2 of the size of a VF"s UAR BAR in MBs.

VF_NODNIC_ENABLE=<False|True> When set to TRUE, VF has VSC Gateway exposed through PCI, and may access the NODNIC initialization segment

VF_VPD_ENABLE=<False|True> When set, VPD Capability is exposed to Virtual Functions.

TPT CONF:

INT_LOG_MAX_PAYLOAD_SIZE=<AUTOMATIC|_4KB>Sets the PCIe burst size for the NIC internal Translation and Protection (TPT) mechanism.

0x0: AUTOMATIC

0xC: _4KB

GLOBAL PCI CONF 2:

MAX_ACC_OUT_READ=<NUM> Maximum accumulated outstanding Read requests bytes. Value is given in units of 1K bytes.

The limit is applied for each PCI bus link individually.

Value 0x0 indicates the use of device defaults.

Configuration is available only when NV_PCI_CONF.ADVANCED_PCI_SETTINGS is TRUE.

PCIE_CREDIT_TOKEN_TIMEOUT=<NUM> PCIe credit timeout. In case a pending transaction has no credits longer than this timeout value, buffered transactions will be dropped. Value is given in milliseconds in the range of 10 to 4,000.

Value 0x0 indicates the device will adjust the timeout automatically.

Value 0xffff disables the feature.

POWER CONF:

ACCURATE_TX_SCHEDULER=<False|True> When TRUE, the device will optimize the transmit scheduler for high accuracy.

When False, the device defaults will apply for the scheduler.

ADVANCED_POWER_SETTINGS=<False|True> Show/hide additional power settings parameters.

Warning: Wrong power settings may cause physical damage.

DISABLE_SLOT_POWER_LIMITER=<False|True> When cleared, the device is not allowed to consume more than 25W from the PCIe power rails, unless a PCI slot power limit message statesthat a new power limit is received.

When set, the slot power limiter is disabled, and the device is allowed to consume more than 25W from the PCIe power rails.

Note: if the power limiter is active and there is not enough power, the device will shut down the network modules.

LAG_RESOURCE_ALLOCATION=<DEVICE_DEFAULT|PRE_ALLOCATION>Defines the way resources are allocated for LAG

0x0: DEVICE_DEFAULT

0x1: PRE_ALLOCATION - resources are preallocated regardless of LAG activation

using pre-allocation allows LAG activation regardless of functions state

Other values are reserved

NETWORK_PORTS_NUMBER=<NUM> Number of network ports enabled by the device, If the value exceeds the number of ports supported by the card, this field will be ignored. Value 0x0 indicates device defaults.

PARTIAL_RESET_EN=<False|True> When set, the partial reset flow is enabled. This reset skips on resetting GPIOs, loading PLL new parameters and performing self-tests. Partial reset will be triggered only if no exceptions requiring full reset were detected (for example, if any of the boot record"s parameter had changed)

PHY_COUNT_LINK_UP_DELAY=<DELAY_10_SEC|DELAY_20_SEC|DELAY_NONE>Defines a period after Link UP where phy counters activation is delayed

0x0: DELAY_NONE

0x1: DELAY_10_SEC

0x2: DELAY_20_SEC

Other values are reserved

RESET_WITH_HOST_ON_ERRORS=<False|True> When set, host reset will trigger a device reset, if the device has previously detected fatal errors.

RT_PPS_ENABLED_ON_POWERUP=<False|True> When TRUE the PPS_OUT will be activated on power up

Applicable only when REAL_TIME_CLOCK_ENABLE is TRUE

SW_RECOVERY_ON_ERRORS=<False|True> When set, SW will be instructed to perform a recovery flow when health buffer reports an error.

HOST SYNC CONF:

ICMD_SEM_LOCK_THRESHOLD=<NUM> Host will be expelled from VSEC Gateway usage if it holds the ICMD Global Semaphore for a period longer than this threshold. Value is given in units of 0.1sec

Value 0xFFFF indicates this threshold is infinite (disabled)

IDLE_ICMD_SEM_LOCK_THRESHOLD=<NUM> Host will be expelled from VSEC Gateway usage if it holds the ICMD Global Semaphore, without issuing any ICMD, for a period longer than this threshold. Value is given in units of 0.1sec

Value 0xFFFF indicates this threshold is infinite (disabled)

VSEC_EXPULSION_DURATION=<NUM> Host VSEC Gateway expulsion will persist for this period. Value is given in units of 0.1sec

EMULATION NVME CONF:

NVME_EMULATION_CLASS_CODE=<NUM> PCIe class_code register for the NVME emulated device

NVME_EMULATION_DEVICE_ID=<NUM> PCIe device_id config register for the NVME emulated device.

NVME_EMULATION_ENABLE=<False|True> When set to TRUE, NVME device emulation is enabled.

NVME_EMULATION_MAX_QUEUE_DEPTH=<NUM> Log (base 2) of the maximal queue depth of NVME Physical Functions.

Value 0 indicates device default.

NVME_EMULATION_NUM_MSIX=<NUM> Number of MSI-X Vectors assigned for each PF/VF of the NVME emulation device. Value 0x0 will use device defaults

NVME_EMULATION_NUM_PF=<NUM> Total number of PCIe functions (PFs) exposed by the device for NVME emulation.

NVME_EMULATION_NUM_VF=<NUM> The total number of Virtual Functions (VFs) that can be supported for each PF.

NVME_EMULATION_NUM_VF_MSIX=<NUM> Number of MSI-X vectors assigned to each VF associated with this type of PF. Value 0x0 indicates device defaults.

NVME_EMULATION_REVISION_ID=<NUM> PCIe revision_id register for the NVME emulated device

NVME_EMULATION_SUBSYSTEM_ID=<NUM> PCIe subsystem_id register for the NVME emulated device

NVME_EMULATION_SUBSYSTEM_VENDOR_ID=<NUM>PCIe subsystem_vendor_id register for the NVME emulated device

NVME_EMULATION_VENDOR_ID=<NUM> PCIe vendor_id config register for the NVME emulated device.

EMULATION PCI SWITCH CONF:

PCI_SWITCH_EMULATION_ENABLE=<False|True>When TRUE, the device will expose a PCI switch. All PF configurations are applied on the switch downstream ports. On such case, each PF will have a different PCI device on the emulated switch. This configuration allows to expose 0 network PFs toward host

PCI_SWITCH_EMULATION_NUM_PORT=<NUM> Number of emulated switch downstream ports. Each downstream port can hold either one emulated PCI hotplug PF or multiple PCI static PFs (emulated functions or Nvidia functions).

VIRTIO_EMULATION_HOTPLUG_TRANS=<False|True>When TRUE, the device will support hotplug of EMulated transitional VIRTIO devices

EMULATION VIRTIO NET CONF:

VIRTIO_NET_EMULATION_ENABLE=<False|True>When set to TRUE, VIRTIO_NET device emulation is enabled.

VIRTIO_NET_EMULATION_NUM_MSIX=<NUM> Number of MSI-X Vectors assigned for each PF/VF of the VIRTIO_NET emulation device. Value 0x0 will use device defaults

VIRTIO_NET_EMULATION_NUM_PF=<NUM> Total number of PCIe functions (PFs) exposed by the device for VIRTIO_NET emulation.

VIRTIO_NET_EMULATION_NUM_VF=<NUM> The total number of Virtual Functions (VFs) that can be supported for each PF.

VIRTIO_NET_EMULATION_NUM_VF_MSIX=<NUM> Number of MSI-X vectors assigned to each VF associated with this type of PF. Value 0x0 indicates device defaults.

VIRTIO_NET_EMULATION_PF_PCI_LAYOUT=<VIRTIO_1_X|VIRTIO_TRANSITIONAL>Indicates which VIrtIO specification the PCI layout of the emulated Physical Function(s) will follow.

0x0: VIRTIO_1_X

0x1: VIRTIO_TRANSITIONAL

other values are reserved

VIRTIO_NET_EMULATION_SUBSYSTEM_ID=<NUM> PCIe subsystem_id register for the VIRTIO_NET emulated device

VIRTIO_NET_EMULATION_VF_PCI_LAYOUT=<VIRTIO_1_X|VIRTIO_TRANSITIONAL>Indicates which VIrtIO specification the PCI layout of the emulated Virtual Function(s) will follow.

0x0: VIRTIO_1_X

0x1: VIRTIO_TRANSITIONAL

other values are reserved

VIRTIO_NET_EMU_SUBSYSTEM_VENDOR_ID=<NUM>PCIe subsystem_vendor_id register for the VIRTIO_NET emulated device

EMULATION VIRTIO BLK CONF:

VIRTIO_BLK_EMULATION_ENABLE=<False|True>When set to TRUE, VIRTIO_BLK device emulation is enabled.

VIRTIO_BLK_EMULATION_NUM_MSIX=<NUM> Number of MSI-X Vectors assigned for each PF/VF of the VIRTIO_BLK emulation device. Value 0x0 will use device defaults

VIRTIO_BLK_EMULATION_NUM_PF=<NUM> Total number of PCIe functions (PFs) exposed by the device for VIRTIO_BLK emulation.

VIRTIO_BLK_EMULATION_NUM_VF=<NUM> The total number of Virtual Functions (VFs) that can be supported for each PF.

VIRTIO_BLK_EMULATION_NUM_VF_MSIX=<NUM> Number of MSI-X vectors assigned to each VF associated with this type of PF. Value 0x0 indicates device defaults.

VIRTIO_BLK_EMULATION_PF_PCI_LAYOUT=<VIRTIO_1_X|VIRTIO_TRANSITIONAL>Indicates which VIrtIO specification the PCI layout of the emulated Physical Function(s) will follow.

0x0: VIRTIO_1_X

0x1: VIRTIO_TRANSITIONAL

other values are reserved

VIRTIO_BLK_EMULATION_SUBSYSTEM_ID=<NUM> PCIe subsystem_id register for the VIRTIO_BLK emulated device

VIRTIO_BLK_EMULATION_VF_PCI_LAYOUT=<VIRTIO_1_X|VIRTIO_TRANSITIONAL>Indicates which VIrtIO specification the PCI layout of the emulated Virtual Function(s) will follow.

0x0: VIRTIO_1_X

0x1: VIRTIO_TRANSITIONAL

other values are reserved

VIRTIO_BLK_EMU_SUBS_VENDOR_ID=<NUM> PCIe subsystem_vendor_id register for the VIRTIO_BLK emulated device

GLOBAL PCI CONF 3:

PCI_BUS0_RESTRICT=<False|True> When TRUE, PCI bus width, speed and ASPM will be restricted according to PCI_BUS_RESTRICT_WIDTH, PCI_BUS_RESTRICT_SPEED, PCI_BUS_RESTRICT_ASPM respectively

PCI_BUS0_RESTRICT_ASPM=<False|True> When FALSE, PCI bus will not have ASPM enabled.

Valid when PCI_BUS_RESTRICT is TRUE.

PCI_BUS0_RESTRICT_SPEED=<PCI_GEN_1|PCI_GEN_2|PCI_GEN_3|PCI_GEN_4|PCI_GEN_5>Restricts the PCI speed to be smaller or equal to:

0x0: PCI_GEN_1

0x1: PCI_GEN_2

0x2: PCI_GEN_3

0x3: PCI_GEN_4

0x4: PCI_GEN_5

Valid when PCI_BUS_RESTRICT is TRUE.

PCI_BUS0_RESTRICT_WIDTH=<PCI_X1|PCI_X16|PCI_X2|PCI_X4|PCI_X8>Restricts the PCI bus width to be smaller or equal to:

0x0: PCI_X1

0x1: PCI_X2

0x2: PCI_X4

0x3: PCI_X8

0x4: PCI_X16

Valid when PCI_BUS_RESTRICT is TRUE.

PCI_BUS1_RESTRICT=<False|True> See PCI_BUS0_RESTRICT

PCI_BUS1_RESTRICT_ASPM=<False|True> See PCI_BUS0_RESTRICT_ASPM

PCI_BUS1_RESTRICT_SPEED=<PCI_GEN_1|PCI_GEN_2|PCI_GEN_3|PCI_GEN_4|PCI_GEN_5>See PCI_BUS0_RESTRICT_SPEED

0x0: PCI_GEN_1

0x1: PCI_GEN_2

0x2: PCI_GEN_3

0x3: PCI_GEN_4

0x4: PCI_GEN_5

PCI_BUS1_RESTRICT_WIDTH=<PCI_X1|PCI_X16|PCI_X2|PCI_X4|PCI_X8>See PCI_BUS0_RESTRICT_WIDTH

0x0: PCI_X1

0x1: PCI_X2

0x2: PCI_X4

0x3: PCI_X8

0x4: PCI_X16

PCI_BUS2_RESTRICT=<False|True> See PCI_BUS0_RESTRICT

PCI_BUS2_RESTRICT_ASPM=<False|True> See PCI_BUS0_RESTRICT_ASPM

PCI_BUS2_RESTRICT_SPEED=<PCI_GEN_1|PCI_GEN_2|PCI_GEN_3|PCI_GEN_4|PCI_GEN_5>See PCI_BUS0_RESTRICT_SPEED

0x0: PCI_GEN_1

0x1: PCI_GEN_2

0x2: PCI_GEN_3

0x3: PCI_GEN_4

0x4: PCI_GEN_5

PCI_BUS2_RESTRICT_WIDTH=<PCI_X1|PCI_X16|PCI_X2|PCI_X4|PCI_X8>See PCI_BUS0_RESTRICT_WIDTH

0x0: PCI_X1

0x1: PCI_X2

0x2: PCI_X4

0x3: PCI_X8

0x4: PCI_X16

PCI_BUS3_RESTRICT=<False|True> See PCI_BUS0_RESTRICT

PCI_BUS3_RESTRICT_ASPM=<False|True> See PCI_BUS0_RESTRICT_ASPM

PCI_BUS3_RESTRICT_SPEED=<PCI_GEN_1|PCI_GEN_2|PCI_GEN_3|PCI_GEN_4|PCI_GEN_5>See PCI_BUS0_RESTRICT_SPEED

0x0: PCI_GEN_1

0x1: PCI_GEN_2

0x2: PCI_GEN_3

0x3: PCI_GEN_4

0x4: PCI_GEN_5

PCI_BUS3_RESTRICT_WIDTH=<PCI_X1|PCI_X16|PCI_X2|PCI_X4|PCI_X8>See PCI_BUS0_RESTRICT_WIDTH

0x0: PCI_X1

0x1: PCI_X2

0x2: PCI_X4

0x3: PCI_X8

0x4: PCI_X16

PCI_BUS4_RESTRICT=<False|True> See PCI_BUS0_RESTRICT

PCI_BUS4_RESTRICT_ASPM=<False|True> See PCI_BUS0_RESTRICT_ASPM

PCI_BUS4_RESTRICT_SPEED=<PCI_GEN_1|PCI_GEN_2|PCI_GEN_3|PCI_GEN_4|PCI_GEN_5>See PCI_BUS0_RESTRICT_SPEED

0x0: PCI_GEN_1

0x1: PCI_GEN_2

0x2: PCI_GEN_3

0x3: PCI_GEN_4

0x4: PCI_GEN_5

PCI_BUS4_RESTRICT_WIDTH=<PCI_X1|PCI_X16|PCI_X2|PCI_X4|PCI_X8>See PCI_BUS0_RESTRICT_WIDTH

0x0: PCI_X1

0x1: PCI_X2

0x2: PCI_X4

0x3: PCI_X8

0x4: PCI_X16

PCI_BUS5_RESTRICT=<False|True> See PCI_BUS0_RESTRICT

PCI_BUS5_RESTRICT_ASPM=<False|True> See PCI_BUS0_RESTRICT_ASPM

PCI_BUS5_RESTRICT_SPEED=<PCI_GEN_1|PCI_GEN_2|PCI_GEN_3|PCI_GEN_4|PCI_GEN_5>See PCI_BUS0_RESTRICT_SPEED

0x0: PCI_GEN_1

0x1: PCI_GEN_2

0x2: PCI_GEN_3

0x3: PCI_GEN_4

0x4: PCI_GEN_5

PCI_BUS5_RESTRICT_WIDTH=<PCI_X1|PCI_X16|PCI_X2|PCI_X4|PCI_X8>See PCI_BUS0_RESTRICT_WIDTH

0x0: PCI_X1

0x1: PCI_X2

0x2: PCI_X4

0x3: PCI_X8

0x4: PCI_X16

PCI_BUS6_RESTRICT=<False|True> See PCI_BUS0_RESTRICT

PCI_BUS6_RESTRICT_ASPM=<False|True> See PCI_BUS0_RESTRICT_ASPM

PCI_BUS6_RESTRICT_SPEED=<PCI_GEN_1|PCI_GEN_2|PCI_GEN_3|PCI_GEN_4|PCI_GEN_5>See PCI_BUS0_RESTRICT_SPEED

0x0: PCI_GEN_1

0x1: PCI_GEN_2

0x2: PCI_GEN_3

0x3: PCI_GEN_4

0x4: PCI_GEN_5

PCI_BUS6_RESTRICT_WIDTH=<PCI_X1|PCI_X16|PCI_X2|PCI_X4|PCI_X8>See PCI_BUS0_RESTRICT_WIDTH

快速查看Mellanox网卡config作用的方法

快速查看Mellanox网卡config作用的方法

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3988

3988