先上关系图:

先来看一张内存条的内存在linux内核中是怎么被组织起来的?

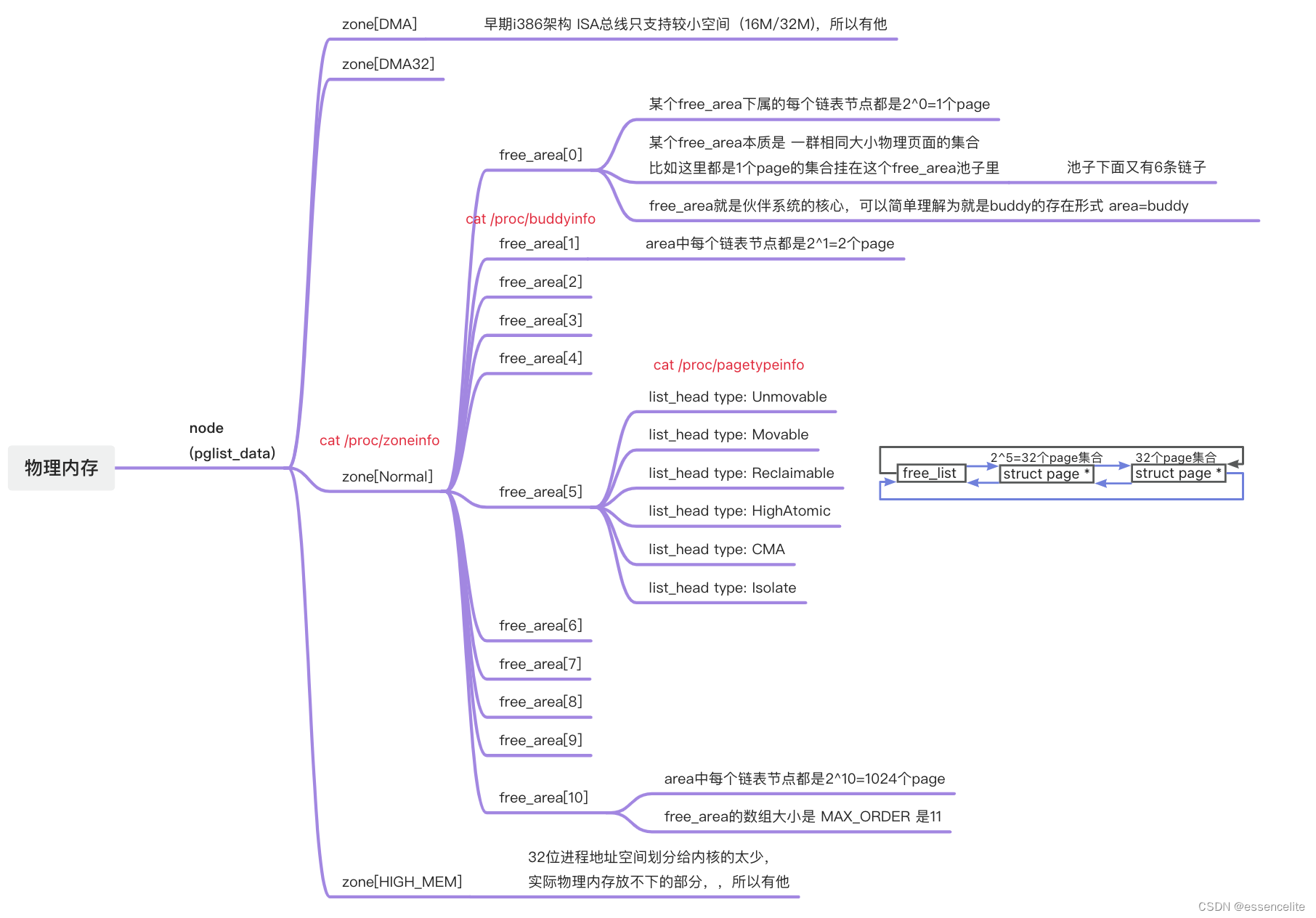

每张内存条在内核中叫一个node

在linux内核中用pglist_data来描述一个node,每个node分成了多个zone,每个zone分成了11个free_area,每个free_area存储了不同大小的页表分别有11种(2^0个page,2^1个page... 2^10个page),每一种大小的页表链又被分到了6种状态子链表(根据页表是否能够移动MOVEABLE等)

详细参考文章:手撕烂笔头-Linux内核中物理内存是如何组织起来的?

所以本质是按照page进行组织的,这些page存在在哪?

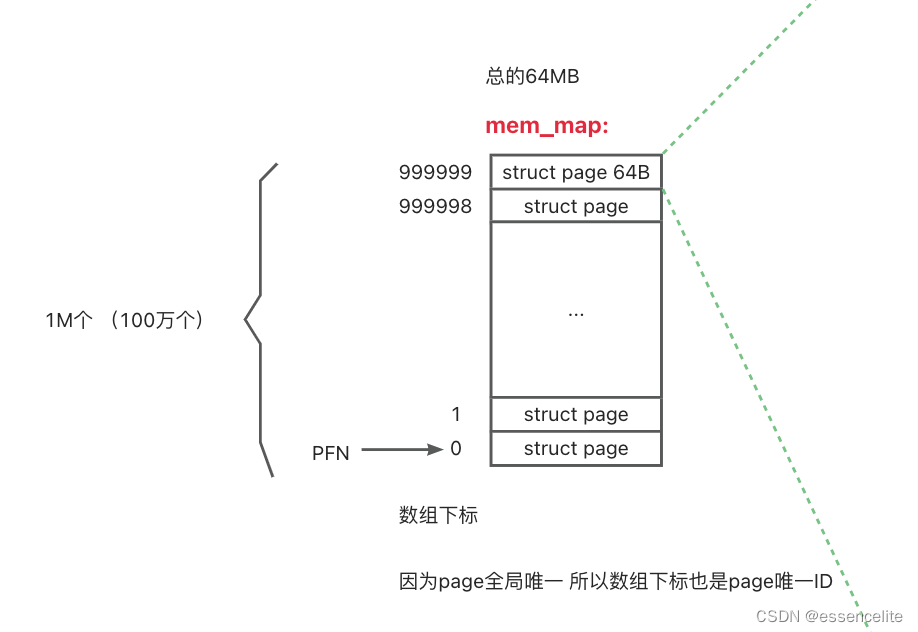

mem_map

![]()

参考代码:

memory.c - mm/memory.c - Linux source code (v5.10.134) - Bootlin

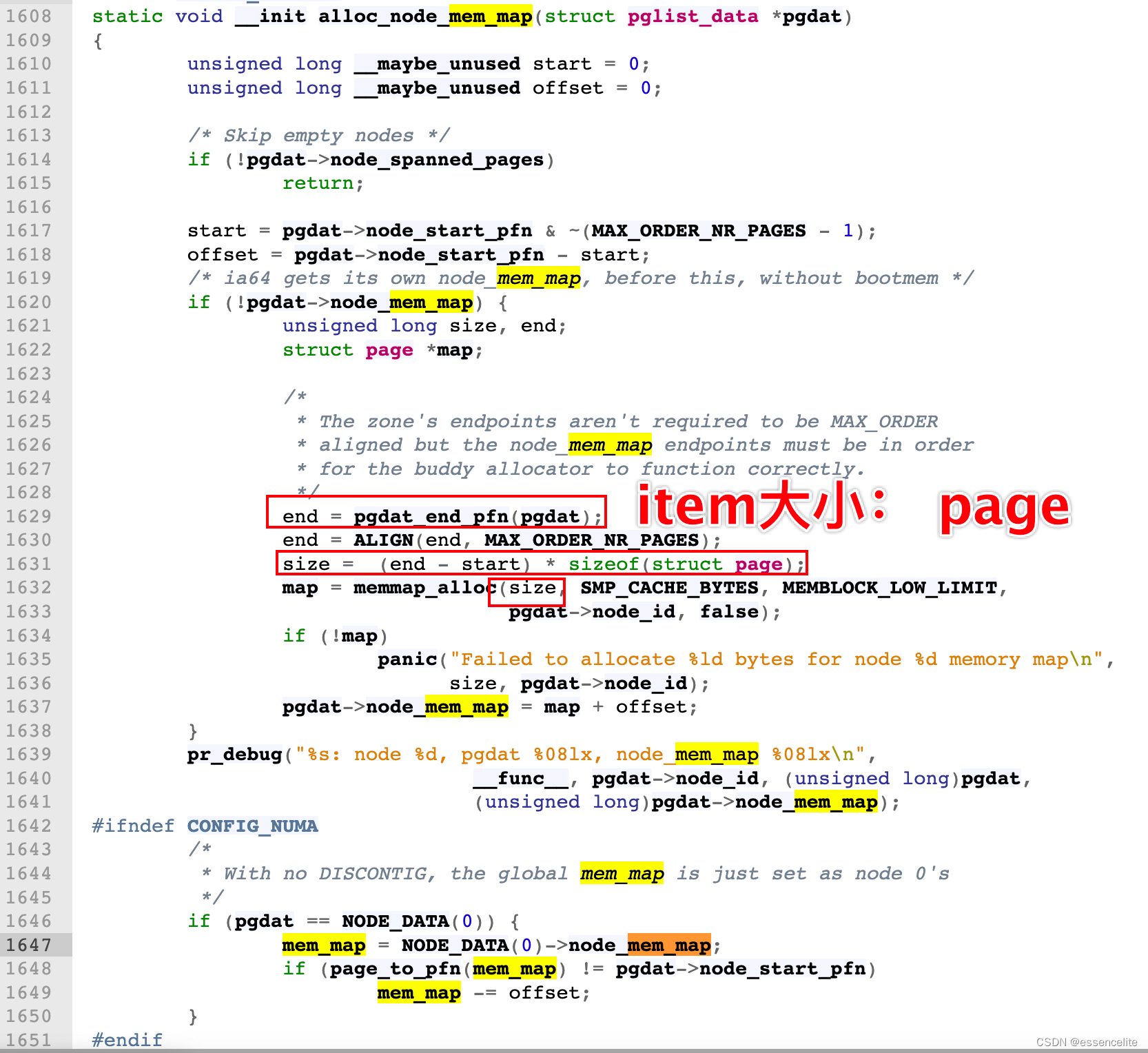

mem_map初始化

查看源码分配了n个struct page的内存。所以相当于是一个大数组。

mm_init.c - mm/mm_init.c - Linux source code (v6.4.8) - Bootlin

如果按照4G物理内存,4K大小的页表,需要4G/4K=1M个,也就是100万个page。

再来看mem_map有多大?

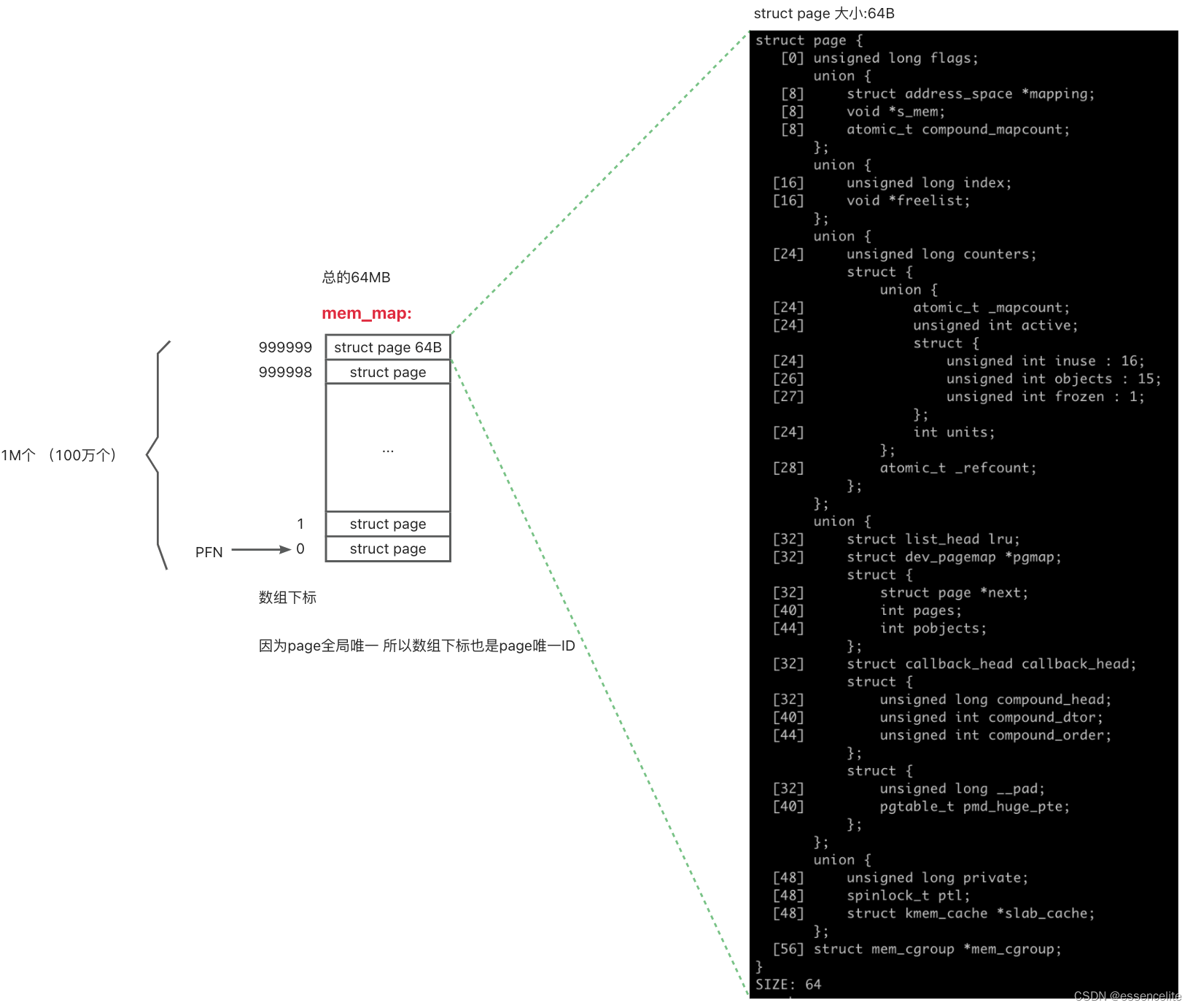

每个page的大小:64B

1M个64B就是64M的mem_map的数组。

PFN到底是什么?

前面把物理内存分成了4K的页,并且用了1M个元素的mem_map管理这100万个页表。

然后每个页就是一个页帧 page frame。

再看PFN全称是什么 page frame number。

所以PFN其实就是这个mem_map的帧序号,或者说index,或者说数组的下标。

为什么用PFN来唯一表示页帧?因为系统所有内存都在mem_map中,所以每一个页帧就有一个唯一id,就是这个PFN,相当于page在mem_map中的身份证。

再看PFN和struct page是什么关系?

根据上面的数据可以得到page全局唯一,所以数组下标也是page唯一ID,所以某个PFN就是它对应的某个struct page在mem_map中的数组下标,通过PFN就能找到这个page的描述符,就能操作这个page

进一步延伸:PFN和struct page如何相互转换?

知道了PFN、mem_map、struct page之间的关系,就能够灵活运用。而且在系统中基本用PFN进行传递struct page,比直接传递struct page的指针(4字节)方便一些(一个int值4字节,并且不需要包含struct page定义)。所以PFN经常用到。

而且PFN比struct page还天生带了一些属性,因为PFN是代表的顺序存储的属性,二struct page只是离散的某个节点。那么在表示多个page尤其是连续性的时候,不用知道struct page大小就能访问周边的page。而且能够用pfn之间关系快速算出page数量,这一点尤其是在DMA场景很有用。

既然PFN和struct page都能唯一表达某个page,那么如何相互转化?

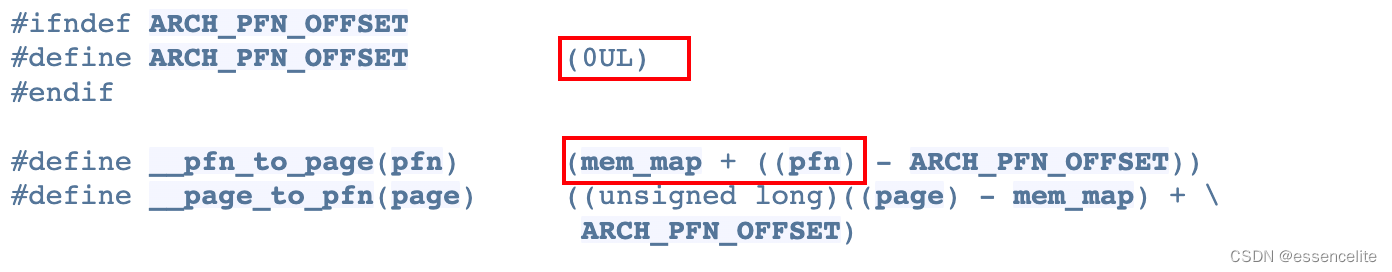

系统提供了两个接口:

page_to_pfn(page)

pfn_to_page(pfn)

memory_model.h - include/asm-generic/memory_model.h - Linux source code (v6.4.8) - Bootlin

可以看到 pfn到page 就是用mem_map直接加上pfn。

反之,如果要根据page计算pfn,也是用mem_map这个基础值进行转换

综述

综述,物理页表的PFN到底是什么?PFN与struct page有什么关系?

物理页表的PFN是某个物理页面的全局唯一描述符struct page的序号,也是在mem_map中的下标。

PFN就是它对应的某个struct page在mem_map中的数组下标。也是页表的全局唯一ID。并且在上层应用找物理地址的一种描述。

本文解析了Linux内核中内存条的组织结构,介绍了内存节点(node)、zone、free_area和页表的关系,重点讲解了mem_map的作用以及PFN(PageFrameNumber)作为物理页表的唯一标识,阐述了PFN与structpage之间的映射关系及其在系统中的优势。

本文解析了Linux内核中内存条的组织结构,介绍了内存节点(node)、zone、free_area和页表的关系,重点讲解了mem_map的作用以及PFN(PageFrameNumber)作为物理页表的唯一标识,阐述了PFN与structpage之间的映射关系及其在系统中的优势。

1235

1235

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?