1.系统概述

1.1 操作系统的基本概念

在信息化时代,软件是计算机系统的灵魂,而作为软件核心的操作系统,已与现代计算机系统密不可分、融为一体。

计算机系统自下而上大致分为四个部分:

- 硬件

- 操作系统

- 应用程序

- 用户

操作系统管理各种计算机硬件,为应用程序提供基础,并且充当计算机硬件与用户之间的中介。

硬件提供基础的计算资源。

应用程序规定按何种方式使用这些资源。

操作系统控制和协调各用户的应用程序对硬件的分配与使用。

综上,操作系统是指控制和管理整个计算机系统的硬件与软件资源,合理地组织、调度计算机工作与资源的分配,进而为用户和其他软件提供方便接口与环境的程序集合。操作系统是计算机系统中最基本的系统软件。

1.1.2 操作系统的特征

-

并发(Concurrence)

两个或多个事件在同一时间间隔内发生。

在多道程序环境下,在内存中同时装有若干道程序,以便当运行某道程序时,利用其I/O操作而暂停执行时的CPU空挡时间,再调度另一道程序运行,从而实现多道程序交替运行,使CPU保持忙碌状态。 -

共享(Sharing)

即资源共享,系统重的资源可供内存中多个并发执行的进程共同使用。资源共享可分为互斥共享和同时访问两种方式。- 互斥共享方式

一段时间内仅准一个进程访问的资源称为临界资源。

如栈,变量都属于临界资源, - 同时访问方式

- 互斥共享方式

-

虚拟(Virtual)

一个物理上的实体变为若干逻辑上的对应物。

并发处理多道程序分配一个cpu,感觉上使每个终端用户感觉专门有一个CPU为自己服务。 -

异步(Asynchronism)

多道程序环境允许多个程序并发执行,但由于资源有限,进程的执行并不是一贯到底的,而是走走停停。这就是进程的异步性。

1.1.3 操作系统的目标与功能

操作系统应具备以下几方面的功能:

- 处理机管理

处理机的分配和运行都是以进程(或线程)为单位。 - 存储器管理

- 设备管理

- 文件管理

- 向用户提供接口

- 扩充机器

终终终终--------------------------------

硬件结构

1.CPU是如何执行程序的?

冯诺依曼模型

定义计算机及基本机构五个部分:

-

运算器

-

控制器

-

存储器

-

输入设备

-

输出设备

运算器、控制器是在中央处理器里的,存储器就我们常见的内存,输入输出设备则是计算机外接的设备

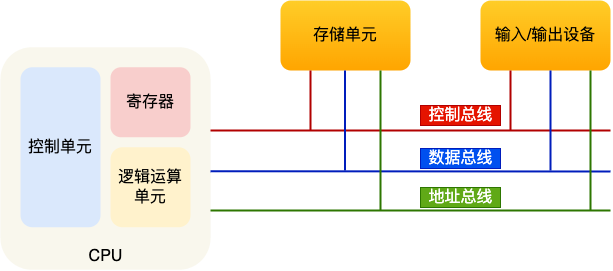

存储单元和输入输出设备要与中央处理器打交道的话,离不开总线。所以,它们之间的关系如下图:

内存

存储数据基本单位是字节(byte),1字节等于8比特。

每一个字节都对应一个内存地址。内存的地址是从 0 开始编号的,然后自增排列,最后一个地址为内存总字节数 - 1

中央处理器(CPU)

32 位和 64 位 CPU 最主要区别在于一次能计算多少字节数据:

- 32 位 CPU 一次可以计算 4 个字节;

- 64 位 CPU 一次可以计算 8 个字节;

这里的32位和64位称为CPU的位宽,代表的是CPU一次可以计算的数据量。

之所以 CPU 要这样设计,是为了能计算更大的数值。如8位CPU,只能计算0~255间的数值。

CPU内部的常见组件

- 控制单元:负责控制CPU工作

- 逻辑运算单元:负责计算

- 寄存器:主要用于存储计算时的数据,分为多个种类。

- 通用寄存器:用来存放需要进行运算的数据

- 程序计数器:用来存储CPU要执行下一条指令所在的内存地址。

- 指令计算器:用来存放当前正在执行的指令

总线

总线用于CPU和内存以及其他设备之间的通信,总线可分为:

- 地址总线,用于指定CPU将要操作的内存地址

- 数据总线,用于读写内存的数据

- 控制总线,用于发送和接受信号

CPU读写内存一般顺序

- 首先通过地址总线来指定内存的地址

- 然后通过控制总线控制是读或写命令

- 最后通过数据总线来传输数据

输入、输出设备

输入设备向计算机输入数据,计算机经过计算后,把数据输出给输出设备。期间,如果输入设备是键盘,按下按键时是需要和CPU进行交互的,这是就需要用到控制总线了。

线路位宽与CPU位宽

在计算小于32位的数字时,32位计算机和64为计算机并没有什么区别。

只有计算超过32位的数才能体现64位计算机的优点。

程序执行过程

- CPU读取程序计数器的值,然后在CPU的控制单元操作地址总线指定需要方位的内存地址,接着通知内存设备准备数据,数据准备好后通过数据总线将指令数据传给CPU,CPU收到内存传来的数据后,将这个指令数据存入到指令寄存器。

- 程序计数器的值自增,表示指向下一条指令。这个自增的大小,由CPU的位宽决定,32为CPU需4个字节的地址,所以自增4.

- CPU分析指令寄存器中的指令,确定指令的类型和参数,如果计算类型的指令,就把指令交给逻辑运算单元运算;如果是存储类型的指令,则交给控制单元执行。

CPU的指令周期:

CPU从程序计数器读取指令、到执行、再到下一条指令的过程。

指令

指令周期:

-

CPU 通过程序计数器读取对应内存地址的指令,这个部分称为 Fetch(取得指令);

-

CPU 对指令进行解码,这个部分称为 Decode(指令译码);

-

CPU 执行指令,这个部分称为 Execution(执行指令);

-

CPU 将计算结果存回寄存器或者将寄存器的值存入内存,这个部分称为 Store(数据回写);

指令的类型:

- 数据传输类型

- 运算类型

- 跳转类型

- 信号类型

- 闲置类型

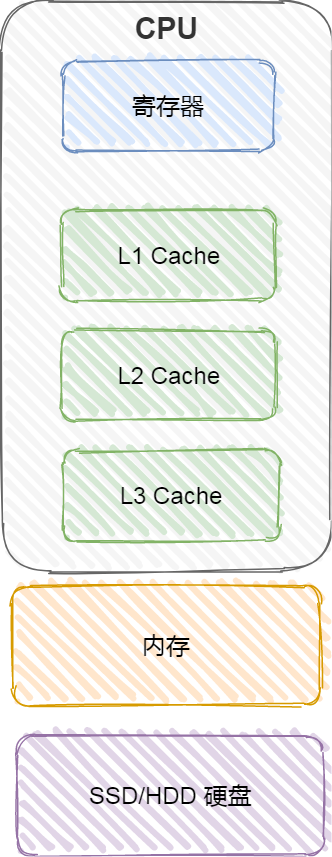

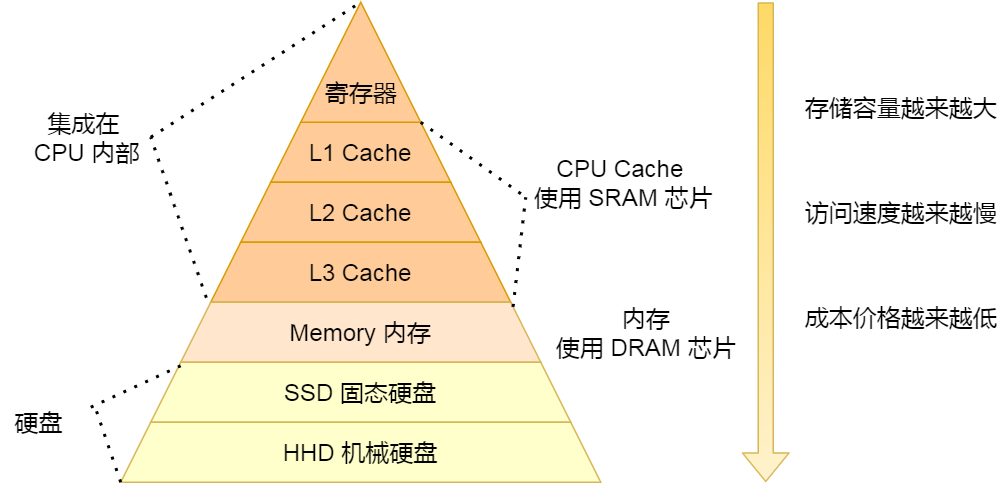

存储器

存储器的层次结构

CPU Cache(CPU高速缓存)通常会分为L1,L2,L3三层。

其中 L1 Cache 通常分成「数据缓存」和「指令缓存」,L1 是距离 CPU 最近的,因此它比 L2、L3 的读写速度都快、存储空间都小。

存储器通常分为这么几个级别:

寄存器

最靠近 CPU 的控制单元和逻辑计算单元的存储器

CPU Cache

CPU Cache用的是一种叫 SRAM(Static Random Access Memory,静态随机存储器)。

L1和L2每个CPU核心都有,L3高速缓存通常是多个CPU核心公用的。

内存

内存用的芯片和 CPU Cache 有所不同,它使用的是一种叫作 DRAM (Dynamic Random Access Memory,动态随机存取存储器) 的芯片。

SSD/HDD 硬盘

SSD(Solid-state disk) 就是我们常说的固体硬盘。

当然还有一种传统硬盘,机械硬盘(Hard Disk Drive, HDD),它是通过物理读写的方式来访问数据的。访问速度非常慢。

存储器的层次关系

CPU并不直接和每一种存储器直接打交道,而是每一种存储器设备只和它相邻的存储器设备打交道。

CPU需要访问内存某个数据时,也是先找寄存器,寄存器没有再找L1.以此类推。

3.如何写出让CPU跑的更快的代码

因为CPU和内存的读取性能随技术发展越来越大,所以引入CPU Cache作为过渡优化读取速度。

CPU Cache是一块一块从内存读取数据的,成为Cache Line(混存块)。

为了区别不同的内存块,在对应的CPU Cache Line中我们还会存储一个组标记(Tag)。这个组标记信息外,CPU Cache Line还有两个信息:

- 从内存加载过来的实际存放数据

- 有效位,用来标记对应的CPU Cache Line中的数据是否有效。

CPU从CPU Cache读取数据时,并不是直接读整个数据块,而是读CPU需要的一个数据片段,这样的数据统称为一个字(Word)。那怎么在对应的 CPU Cache Line 中数据块中找到所需的字呢?答案是,需要一个偏移量(Offset)。

因此,一个内存的访问地址,包括组标记、CPU Cache Line 索引、偏移量这三种信息

而对于 CPU Cache 里的数据结构,则是由索引 + 有效位 + 组标记 + 数据块组成。

如何写出让CPU跑的更快的代码

更多的数据能从CPU Cache找到而不是找内存。

访问的数据在CPU Cache中的话,意味着缓存命中。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?