1、说明

阿里的平头哥在github上开源了riscv项目-wujian100_open。本文是使用vivado对该项目进行综合。

本文介绍方法,没有按开源项目的readme所说的synplify综合网表的方式,而是全程采用vavido新建项目进行的综合。

主要问题是:1、 头文件属性;2、约束;3、其它小问题。

2、过程

工具采用win10下的vavido2018.2;代码采用2019.10.22日晚github上版本。

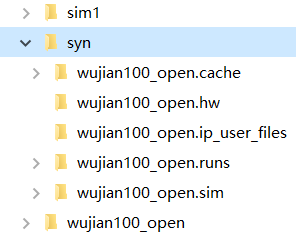

- 建立目录workarea(名字任意),目录下:git下载的wujian100_open、syn、sim1目录同级,如下:

- 在syn下新建xilinx的项目,选择对应器件(fpga目录的tcl文件里器件类型是对的,xdc里的封装说错了。型号应该是:xc7a200tfbg484-2)。

- add source,选择目录直接加最简单,加xdc。注意问题:语法有显示错的4个文件,编译项目也会报错。通过vivado的界面,把这几个文件的属性改为verilog head type。按一般设计规范,这几个v文件,应该采用vh后缀。

- 再次编译,xdc里报错:

[Place 30-574] Poor placement for routing between an IO pin and BUFG. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this

本文介绍了如何使用Vivado 2018.2对平头哥开源的RISC-V项目wujian100_open进行综合。在过程中,遇到了头文件属性、约束和小问题,如vivado界面中语法错误的文件属性设置、xdc报错及未约束的管脚问题。通过调整文件属性、修改xdc约束和解除注释,成功完成了综合,并得到资源使用情况。

本文介绍了如何使用Vivado 2018.2对平头哥开源的RISC-V项目wujian100_open进行综合。在过程中,遇到了头文件属性、约束和小问题,如vivado界面中语法错误的文件属性设置、xdc报错及未约束的管脚问题。通过调整文件属性、修改xdc约束和解除注释,成功完成了综合,并得到资源使用情况。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2421

2421

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?