理想ADC-DAC Verilog-A模型仿真——动态性能仿真

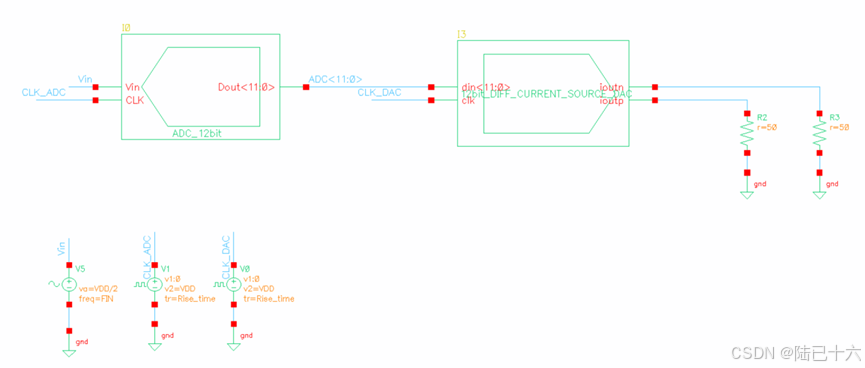

1.电路原理图

2.仿真调试设置

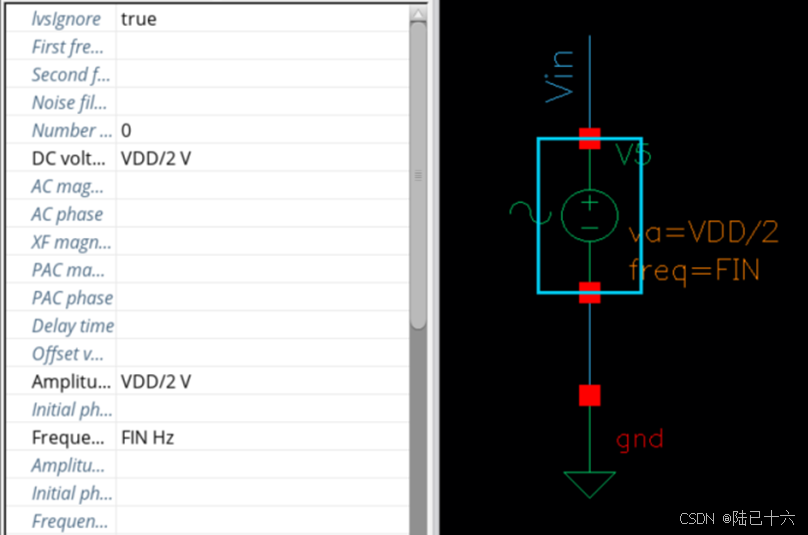

1) 输入信号V5设置如下:

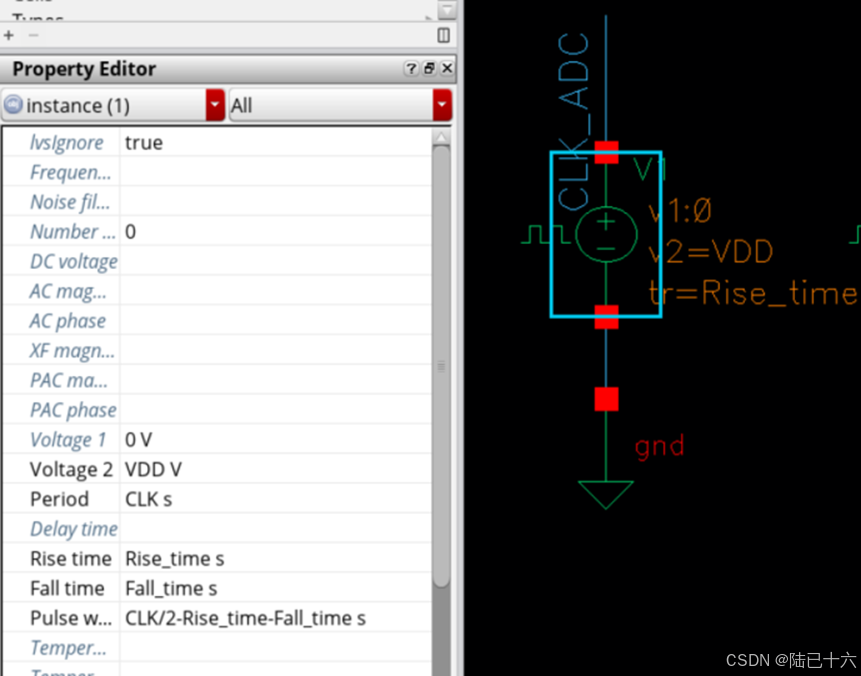

2) ADC参考时钟设置如下:

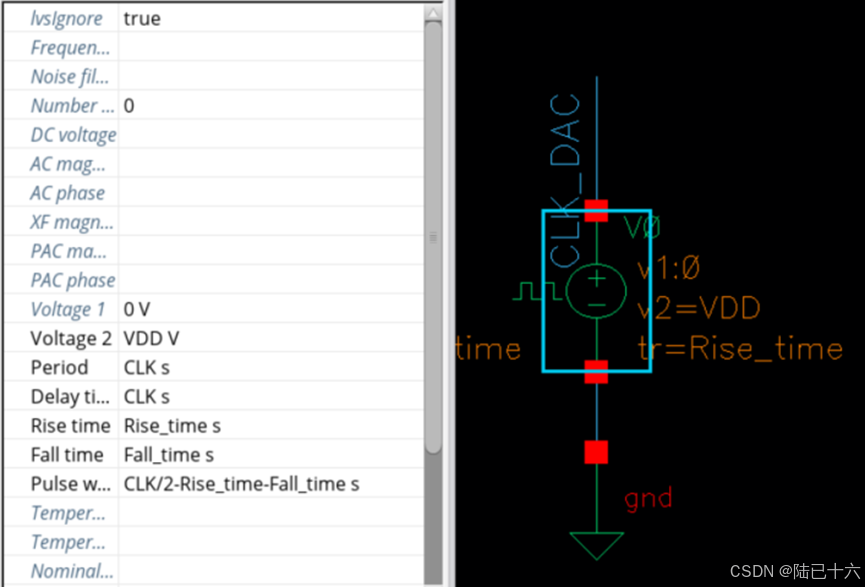

3) DAC参考时钟设置如下:

4) 12bit ADC Verilog-A Code

// ADC_12bit

`include "discipline.h"

`include "constants.h"

`define NUM_ADC_BITS 12

module a2d_ideal (Vin, CLK, Dout);

input Vin, CLK;

electrical Vin, CLK;

output [`NUM_ADC_BITS-1:0] Dout;

electrical [`NUM_ADC_BITS-1:0] Dout;

parameter real VDD = 1.2;

parameter real GND = 0;

parameter real one = 1.2;

parameter real zero = 0.0;

parameter real vth = VDD/2;

parameter real slack = 10.0p from (0:inf);

parameter real trise = 10p from (0:inf);

parameter real tfall = 10p from (0:inf);

parameter real tconv = 10p from [0:inf);

parameter integer traceflag = 0;

real sample, vref, lsb, voffset;

real vd[0:`NUM_ADC_BITS-1];

integer ii, binvalue;

analog begin

@(initial_step or initial_step("dc", "ac", "tran", "xf")) begin

vref = (VDD

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2168

2168

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?