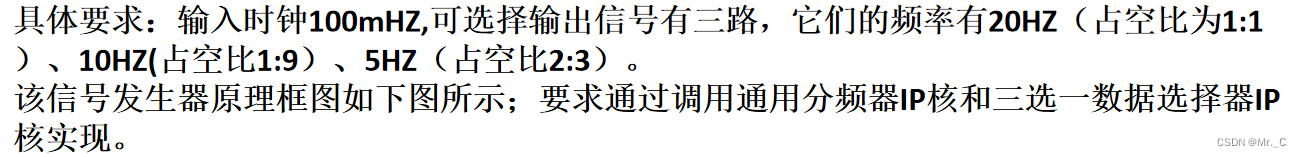

EDA IP核及综合系统设计:

运用IP核的相关知识,由计数器设计可选的多时钟信号发生器。通过分频器分频产生20HZ、10HZ、5HZ的频率,并通过三选一选择器选择一个频率进行输出。选择端可通过两个拨码开关进行选择。

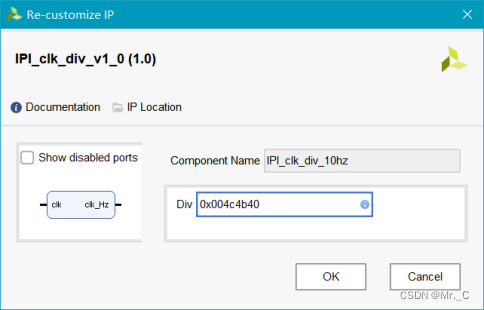

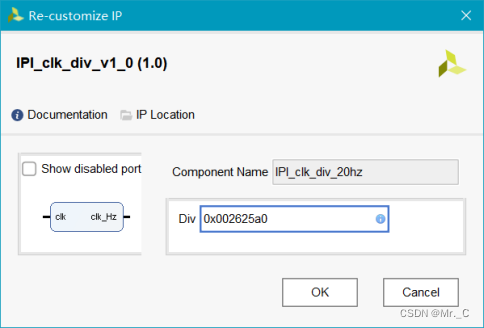

(1)分频IP核

`timescale 1ns / 1ps

module IPI_clk_div(

input clk,

output reg clk_Hz

);

integer clk_cnt; //计数器的值

parameter[31:0] div=32'd10000000; //分频值

always @(posedge clk)

begin

if(clk_cnt>=div)//判断计数器的值是否计数到div

begin

clk_cnt <= 1'b0;

clk_Hz <= ~clk_Hz;end //如果计数到div,计数器的值清零,同时clk_Hz的电平翻转一次,即分频后频率100MHz/div/2

else

clk_cnt <= clk_cnt + 1'b1;//计数没有到div,计数值加1

end

endmodule

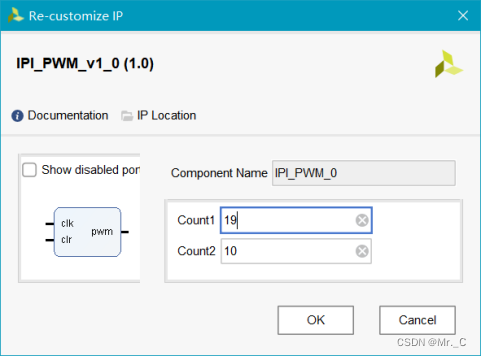

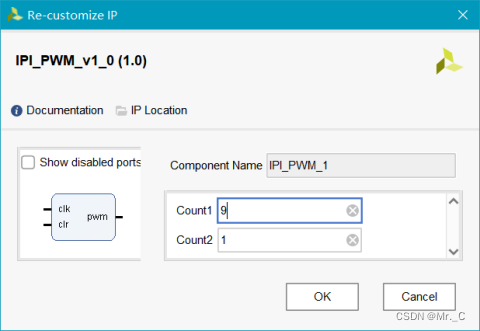

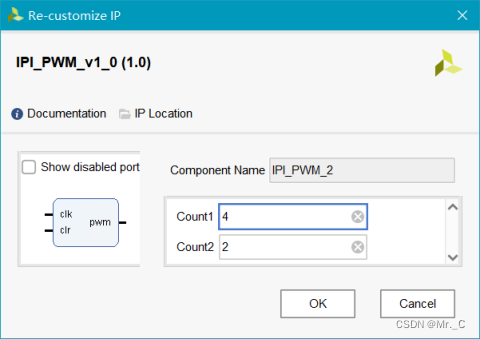

(2)调整频率占空比IP核

`timescale 1ns / 1ps

module IPI_PWM(

input wire clk,

input wire clr,

output reg pwm

);

reg[4:0] count;

parameter count1 =19;

parameter count2 =10;

always @(posedge clk or posedge clr)

if(clr == 1)

count <= 0;

else if(count == count1)

count <= 0;

else

count <= count + 1;

always @(*)

if(count < count2)

pwm <= 1;

else

pwm <= 0;

endmodule

(3)三选一数据选择器IP核

`timescale 1ns / 1ps

module IPI_data_selecter( x,clk_20hz,clk_10hz,clk_5hz,y);

input[1:0] x;

input clk_20hz;

input clk_10hz;

input clk_5hz;

output reg y;

always@(*)

case(x)

2'b00:y<=clk_20hz;

2'b01:y<=clk_10hz;

2'b10:y<=clk_5hz;

endcase

endmodule

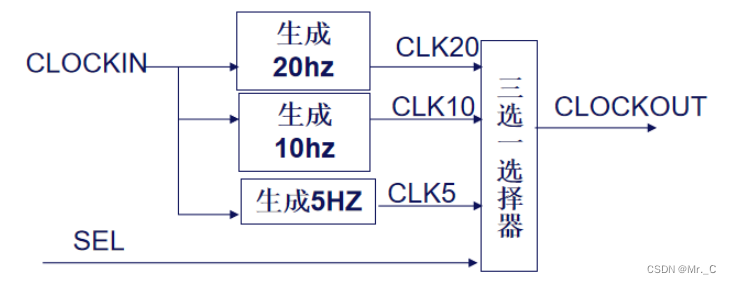

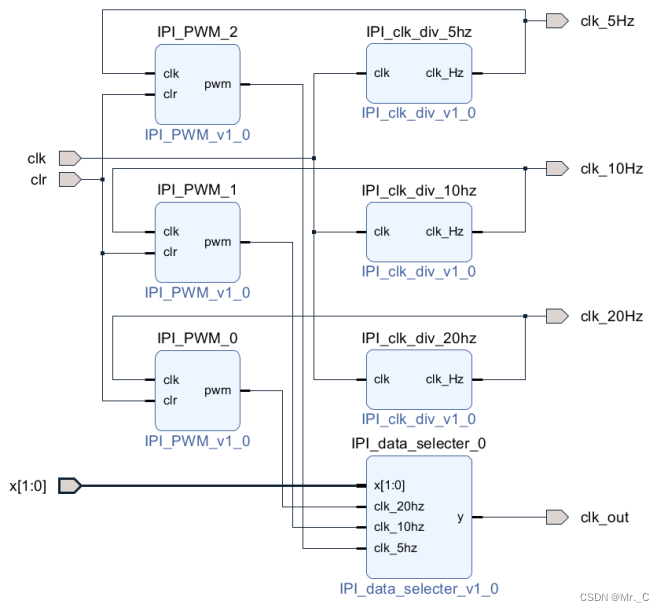

原理图:

原理图及IP核说明:

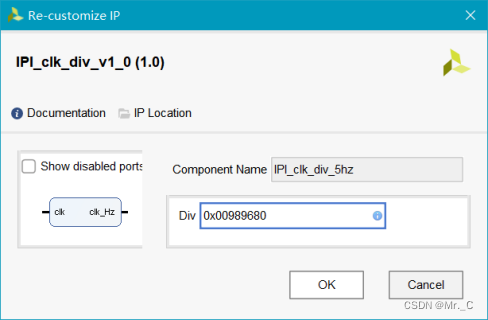

分频IP核把分频计数值div定义为了parameter变量,所以分频为不同频率只需要改变div的值即可。

同样,调整频率占空比IP核定义了两个parameter变量,分别为count1和count2,当需要不同的占空比时只需要改变它们的值即可。

EDA IP核设计实例

EDA IP核设计实例

本文介绍了使用IP核设计实现多时钟信号发生器的过程。包括分频器产生20HZ、10HZ、5HZ频率的分频IP核,调整频率占空比IP核以及用于选择输出频率的三选一数据选择器IP核。通过拨码开关进行频率选择。

本文介绍了使用IP核设计实现多时钟信号发生器的过程。包括分频器产生20HZ、10HZ、5HZ频率的分频IP核,调整频率占空比IP核以及用于选择输出频率的三选一数据选择器IP核。通过拨码开关进行频率选择。

738

738

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?