一、在电赛开始的前一天中午,突然得知2021电赛电赛推迟至8月11号至14号,现在晚上又通知变成了择期,比赛时间遥遥无期

既然如此那就再继续拼搏吧,顺便也分享一下备赛以来对msp432的学习

二、前情提示,本文适用于msp432库函数开发使用者,且已具备msp432环境(我使用的是keil),已下载SDK包,并有simeplink例程。若需要这些资源的,可以在评论区回复,我看见了会及时发送的!

三、今天要分享的是使用msp432库函数输出多路pwm,用以控制基础的电机转动。

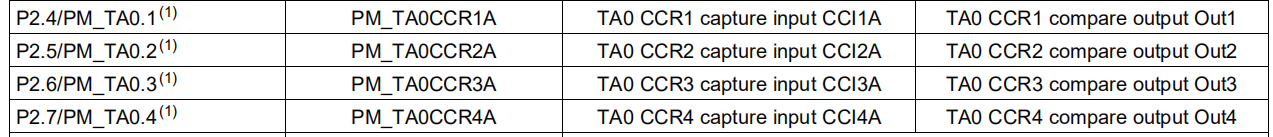

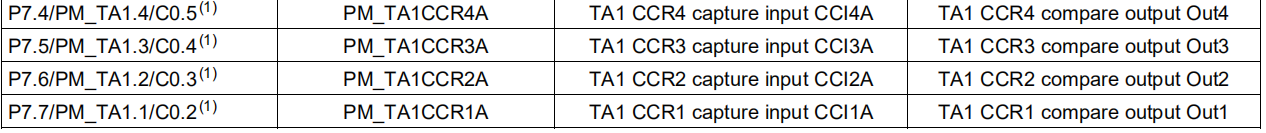

1)所用到的引脚 P7.4~P7.7 、P2.4~P2.7共八路提供选择

2)查看数据手册

由手册可以知道,定时器TA0,寄存器CCR0~CCR4对应P2.4 - P2.7

定时器TA1,寄存器CCR0~CCR4对应P7.4 - P7.7

3)输出PWM初始化

/* Timer_A Compare Configuration Parameter (PWM1) */

Timer_A_PWMConfig compareConfig_PWM1 =

{

TIMER_A_CLOCKSOURCE_SMCLK,

TIMER_A_CLOCKSOURCE_DIVIDER_10,

6000, //占空比设总值

TIMER_A_CAPTURECOMPARE_REGISTER_1, // Use CCR1 7.7

TIMER_A_OUTPUTMODE_RESET_SET, // Toggle output but

0//初始占空比设值 // Duty Cycle

};

1.默认时钟源SMCLK,但可在主函数提前设置DCO时钟源,实现主频48MHZ;

2.TIMER_A_CLOCKSOURCE_DIVIDER_10,预分频系数设置为10;

3. 6000,占空比设总值

4. TIMER_A_CAPTURECOMPARE_REGISTER_1 使用寄存器CCR1

5. 默认翻转电平

6. 0,初始占空比设值

4)设置引脚输出PWM

/* Setting P7.7 and P7.4 and peripheral outputs for CCR */

MAP_GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_P7,GPIO_PIN6 + GPIO_PIN7 + GPIO_PIN4 + GPIO_PIN5,

GPIO_PRIMARY_MODULE_FUNCTION);

/* Setting P2.7 and P2.4 and peripheral outputs for CCR */

MAP_GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_P2,GPIO_PIN6 + GPIO_PIN7 + GPIO_PIN4 + GPIO_PIN5,

GPIO_PRIMARY_MODULE_FUNCTION);

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM1); //7.7 ~ 7.4

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM2);

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM3);

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM4);

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM5); //2.4 ~ 2.7

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM6);

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM7);

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM8);

5)设置自己需要的占空比大小(基准为6000)

compareConfig_PWM1.dutyCycle = 600;

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM1);

compareConfig_PWM2.dutyCycle = 1200;

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM2);

compareConfig_PWM3.dutyCycle = 1800;

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM3);

compareConfig_PWM4.dutyCycle = 2400;

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM4);

compareConfig_PWM5.dutyCycle = 3000;

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM5);

compareConfig_PWM6.dutyCycle = 3600;

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM6);

compareConfig_PWM7.dutyCycle = 4200;

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM7);

compareConfig_PWM8.dutyCycle = 4800;

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM8);

如第一句占空比大小为600 / 6000 = 0.1即10%大小的占空比

6)设置MSP432时钟源最高主频48MHZ

MAP_PCM_setPowerState(PCM_AM_LDO_VCORE1);

MAP_CS_setDCOCenteredFrequency(CS_DCO_FREQUENCY_48);

总体的代码如下

//***************************************************************************************

// Pursuit of excellence

// Description; Multifunctional integration file.

// ACLK = n/a, MCLK = SMCLK = default DCO

//

// Header: My integration Library

// File Name: ADC project

// Author: Mr. Wang Yin

// Date: July 31, 2021

// place: Chengdu University of information engineering 5402

//***************************************************************************************

#include "pwm.h"

/* Timer_A Compare Configuration Parameter (PWM1) */

Timer_A_PWMConfig compareConfig_PWM1 =

{

TIMER_A_CLOCKSOURCE_SMCLK,

TIMER_A_CLOCKSOURCE_DIVIDER_10,

6000, //占空比设总值

TIMER_A_CAPTURECOMPARE_REGISTER_1, // Use CCR1 7.7

TIMER_A_OUTPUTMODE_RESET_SET, // Toggle output but

0//初始占空比设值 // Duty Cycle

};

/* Timer_A Compare Configuration Parameter (PWM2) */

Timer_A_PWMConfig compareConfig_PWM2 =

{

TIMER_A_CLOCKSOURCE_SMCLK,

TIMER_A_CLOCKSOURCE_DIVIDER_10,

6000, //占空比设总值

TIMER_A_CAPTURECOMPARE_REGISTER_2, // Use CCR2 7.6

TIMER_A_OUTPUTMODE_RESET_SET, // Toggle output but

0//初始占空比设值 // Duty Cycle

};

Timer_A_PWMConfig compareConfig_PWM3 =

{

TIMER_A_CLOCKSOURCE_SMCLK,

TIMER_A_CLOCKSOURCE_DIVIDER_10,

6000, //占空比设总值

TIMER_A_CAPTURECOMPARE_REGISTER_3, // Use CCR3 7.5

TIMER_A_OUTPUTMODE_RESET_SET, // Toggle output but

0//初始占空比设值 // Duty Cycle

};

Timer_A_PWMConfig compareConfig_PWM4 =

{

TIMER_A_CLOCKSOURCE_SMCLK,

TIMER_A_CLOCKSOURCE_DIVIDER_10,

6000, //占空比设总值

TIMER_A_CAPTURECOMPARE_REGISTER_4, // Use CCR4 7.4

TIMER_A_OUTPUTMODE_RESET_SET, // Toggle output but

0//初始占空比设值 // Duty Cycle

};

//TA0

Timer_A_PWMConfig compareConfig_PWM5 =

{

TIMER_A_CLOCKSOURCE_SMCLK,

TIMER_A_CLOCKSOURCE_DIVIDER_64,

15000, //占空比设总值

TIMER_A_CAPTURECOMPARE_REGISTER_1, // Use CCR1 2.4

TIMER_A_OUTPUTMODE_RESET_SET, // Toggle output but

0//初始占空比设值 // Duty Cycle

};

Timer_A_PWMConfig compareConfig_PWM6 =

{

TIMER_A_CLOCKSOURCE_SMCLK,

TIMER_A_CLOCKSOURCE_DIVIDER_1,

6000, //占空比设总值

TIMER_A_CAPTURECOMPARE_REGISTER_2, // Use CCR1 2.5

TIMER_A_OUTPUTMODE_RESET_SET, // Toggle output but

0//初始占空比设值 // Duty Cycle

};

Timer_A_PWMConfig compareConfig_PWM7 =

{

TIMER_A_CLOCKSOURCE_SMCLK,

TIMER_A_CLOCKSOURCE_DIVIDER_1,

6000, //占空比设总值

TIMER_A_CAPTURECOMPARE_REGISTER_3, // Use CCR1 2.6

TIMER_A_OUTPUTMODE_RESET_SET, // Toggle output but

0//初始占空比设值 // Duty Cycle

};

Timer_A_PWMConfig compareConfig_PWM8 =

{

TIMER_A_CLOCKSOURCE_SMCLK,

TIMER_A_CLOCKSOURCE_DIVIDER_1,

6000, //占空比设总值

TIMER_A_CAPTURECOMPARE_REGISTER_4, // Use CCR1 2.7

TIMER_A_OUTPUTMODE_RESET_SET, // Toggle output but

0//初始占空比设值 // Duty Cycle

};

/* Setting P7.7 and P7.4 and peripheral outputs for CCR */

MAP_GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_P7,GPIO_PIN6 + GPIO_PIN7 + GPIO_PIN4 + GPIO_PIN5, GPIO_PRIMARY_MODULE_FUNCTION);

/* Setting P2.7 and P2.4 and peripheral outputs for CCR */

MAP_GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_P2,GPIO_PIN6 + GPIO_PIN7 + GPIO_PIN4 + GPIO_PIN5, GPIO_PRIMARY_MODULE_FUNCTION);

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM1); //7.7 ~ 7.4

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM2);

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM3);

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM4);

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM5); //2.4 ~ 2.7

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM6);

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM7);

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM8);

compareConfig_PWM1.dutyCycle = 600;

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM1);

compareConfig_PWM2.dutyCycle = 1200;

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM2);

compareConfig_PWM3.dutyCycle = 1800;

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM3);

compareConfig_PWM4.dutyCycle = 2400;

MAP_Timer_A_generatePWM(TIMER_A1_BASE, &compareConfig_PWM4);

compareConfig_PWM5.dutyCycle = 3000;

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM5);

compareConfig_PWM6.dutyCycle = 3600;

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM6);

compareConfig_PWM7.dutyCycle = 4200;

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM7);

compareConfig_PWM8.dutyCycle = 4800;

MAP_Timer_A_generatePWM(TIMER_A0_BASE, &compareConfig_PWM8);

通过以上步骤就可以输出多路PWM了,已通过逻辑分析仪测试可用。

最后由于自己也是新学,能力有限,存在问题的地方请大家在评论区指出,谢谢!

下载库函数包 :https://download.youkuaiyun.com/download/cubejava/20692262

本文介绍如何使用MSP432的库函数实现多路PWM输出,包括配置定时器、设置引脚输出及调整占空比等关键步骤,并提供了完整的代码示例。

本文介绍如何使用MSP432的库函数实现多路PWM输出,包括配置定时器、设置引脚输出及调整占空比等关键步骤,并提供了完整的代码示例。

5331

5331

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?