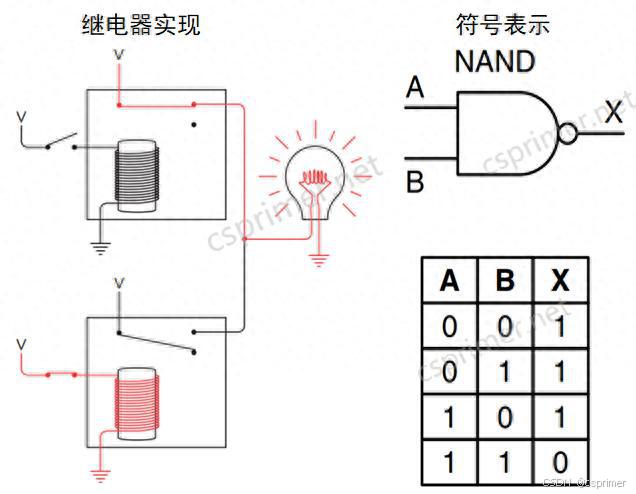

这一节来介绍一下基本门电路的实现,首先看一下最基本的与非门。

与非门特性是跟与门相反,与门是当A B输入为1的时候输出为1其他情况输出为0,而与非门正好相反,当A B输入为1的时候输出为0其他情况输出为1。

我们可以使用继电器来实现,如下图,当左边的两个开关闭合的时候,相当于A B输入为1,两个弹片都被拉下来,那么灯泡这边输出的是0,灯会变灭,其他A B的输入情况总有一个弹片没有被拉下来,那么这时候电源跟输出导通,输出的就是1,灯亮。

也可以使用晶体管来实现,如下图,它由两个NMOS管串联跟两个PMOS管并联构成,NMOS管是当gate输入高电压的时候导通,PMOS管是当gate输入低电压的时候导通,

这两个NMOS管它的源极是接地输入的是0,这两个PMOS管它的源极是接电源的所以输入的是1,右边Y是输出。(不清楚晶体管特性可以看上一篇文章:计算机系统概述)

我们来推导一下,当A B都为1的时候那么两个NMOS管是导通的,所以它们的输出就跟接地是一样,输出的是0,然后当A B为1的时候,两个PMOS管是没有导通的,所以它们的输出对最终的输出Y就不会产生影响,那么输出就是0。

其他情况就是当A B其中一个为0的时候,那么这两个PMOS管总有一个是导通的,那么Y输出的就是1,然后当A B其中一个为0的时候,那么这两个NMOS管总有一个是不导通的,所以它们的输出就不是通的,那么对最终的输出Y就不会产生影响,所以输出

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1628

1628

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?