简单来说,这个过程主要分为三步:导入数据准备、约束规则设置、执行布线。

由于DEF和LEF文件通常与集成电路(IC)设计或复杂封装相关,在PCB级别的Allegro中直接使用它们并不像在IC设计工具中那样标准。Allegro更常见的是处理.brd文件、网表(netlist)和库文件(.dra, .psm, .pad)。因此,你可能需要先将LEF/DEF转换为Allegro能识别的格式,或者这些文件是用于描述一个大型宏模块(如FPGA、ASIC)的物理信息,你需要将其作为一个整体导入到PCB设计中。

以下是具体的操作步骤和细节:

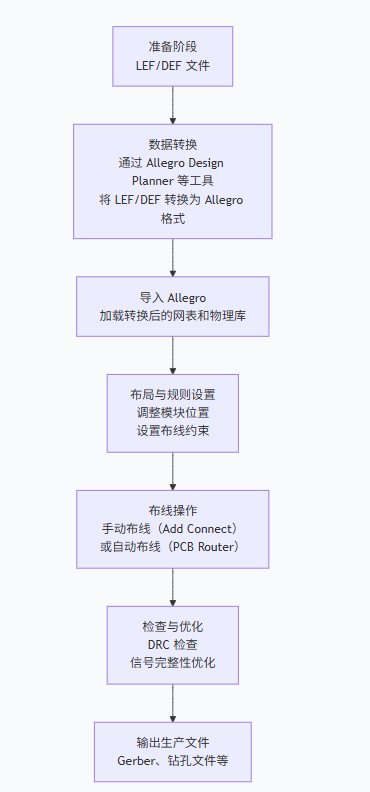

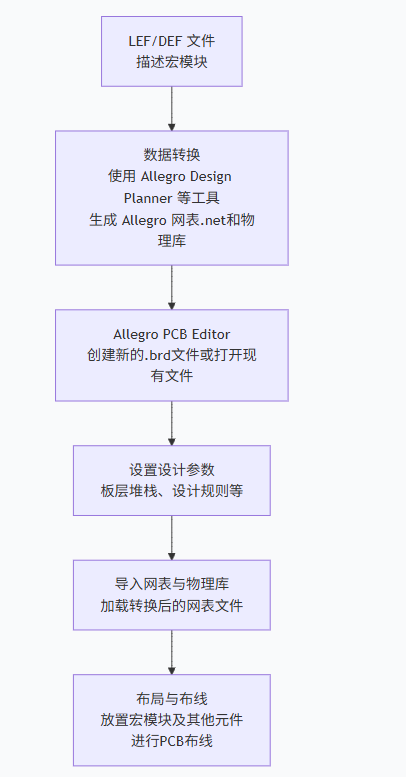

流程概述

LEF(Library Exchange Format)和DEF(Design Exchange Format)文件通常用于描述集成电路的物理布局和布线信息。在Cadence Allegro中,直接使用纯粹的LEF/DEF文件来完成PCB布线并不是其典型工作流程(Allegro更侧重于.brd文件和处理网表、封装库)。因此,通常需要一个转换或导入过程,将LEF/DEF文件的信息转换为Allegro能够识别和操作的格式(如常见的.brd文件、网表、封装库文件.dra、.psm、.pad等)。

下面的流程图概述了可能的工作流程,特别是当你的LEF/DEF文件描述了一个大型宏模块(如FPGA、ASIC)的情况:

📝 详细操作步骤

第一步:数据准备与转换(关键步骤)

由于Allegro PCB Editor不能直接读取原始的LEF/DEF文件,你需要将它们转换成Allegro能识别的格式,通常是生成Allegro的网表文件和物理库文件。

-

理解文件用途:

-

LEF文件:包含工艺信息(tech LEF)和标准单元/宏模块的物理抽象信息(cell LEF),如金属层定义、引脚位置、障碍物等。

-

DEF文件:包含设计的物理实现信息,如芯片面积、单元放置、引脚位置、网络连接以及初始的布线信息等。

-

-

转换数据(具体方法可能因Allegro版本和设计环境而异):

-

通常需要使用Cadence工具链中的其他工具(如Allegro Design Planner、Virtuoso Layout Suite的LEF/DEF工具)来进行转换。

-

转换的目的是从LEF/DEF文件中提取出Allegro PCB布线所需的网表和物理封装信息。

-

这个转换过程可能会生成Allegro格式的网表文件(如

.net)以及元件的物理封装文件(.dra,.psm)。

-

第二步:在Allegro中导入并设置

-

启动Allegro PCB Editor:打开你已经安装好的Allegro软件。

-

创建新项目或打开现有项目:如果你还没有板子文件(.brd),可能需要创建一个新的板子文件(File -> New...)。

-

设置设计参数:

-

进入

Setup->Design Parameters。在Design标签页下,设置合适的绘图单位(Units)、图纸大小(Size)等。 -

进入

Setup->Cross-section设置正确的层叠结构(Layer Stack-up),这与你的LEF文件中的工艺信息相关。

-

-

加载转换后的网表和物理库:

-

指定库路径:在导入网表之前,需要确保Allegro知道到哪里去找转换后生成的物理库文件(.dra, .psm, .pad)。

-

进入

Setup->User Preferences。 -

在左侧路径中找到

Paths->Library。 -

在右侧设置

devpath,padpath, 和psmpath,指向存放你库文件的目录。

-

-

导入网表:

-

进入

File->Import->Logic... -

在打开的 "Import Logic" 对话框中,选择 "Cadence" 标签页(如果你的网表是Allegro格式)。

-

在 "Import netlist" 栏中,指定你转换后生成的网表文件。

-

确保 "Place design parts" 选项通常建议勾选,以便在导入网表后允许摆放元件。

-

点击 "Import Cadence" 按钮执行导入操作。

-

-

第三步:布局与布线

-

元件布局 (Placement):

-

导入网表后,元件会出现在板框外。使用

Place->Manually命令将元件移动到板框内并进行合理布局。 -

对于从DEF文件中导入的已布局信息,元件可能会直接出现在其定义的位置上。

-

-

布线规则设置 (Constraints Setup):

-

布线前,强烈建议先设置设计规则。进入

Setup->Constraints->Constraint Manager(或者老版本中的Electrical->Set Standard Values)。 -

在约束管理器中,你可以设置各种规则,例如:

-

线宽规则 (Physical Rule Set):定义不同网络(如电源、地、信号)的线宽。

-

间距规则 (Spacing Rule Set):定义不同网络、不同层之间的最小间距。

-

高速规则:如差分对、等长线、延迟约束等(如果你的设计涉及高速信号)。

-

-

-

进行布线 (Routing):

-

手动布线:

-

点击工具栏上的

Add Connect图标(或选择Route->Connect命令)开始手动布线。 -

在

Options面板中设置当前层、线宽、过孔类型等参数。 -

单击开始布线,移动鼠标,单击放置线段,双击或右键选择

Add Via换层,最后连接到目标引脚单击完成。

-

-

自动布线:

-

Allegro提供了功能强大的自动布线器 Allegro PCB Router。

-

通常需要在PCB Editor中导出设计文件(.dsn)给PCB Router使用:

File->Export->Router。 -

在PCB Router中,可以设置详细的布线策略,然后运行

Route Automatic进行自动布线。 -

完成自动布线后,将结果导回PCB Editor。

-

-

第四步:检查与输出

-

设计规则检查 (DRC Check):

-

布线完成后,务必进行设计规则检查。进入

Tools->Quick Reports或使用约束管理器检查是否有违反规则(DRC错误)的地方。 -

确保所有错误都被解决或豁免(Waive)。

-

-

光绘文件输出 (Gerber Output):

-

所有设计完成后,需要生成光绘文件用于PCB制造。

-

进入

Manufacture->Artwork。 -

在 "Film Control" 标签页中设置各层的光绘参数。

-

点击 "Create Artwork" 生成Gerber文件。

-

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?