4 原理图后期处理

4.1 DRC检查

按照前面的方法把原理图剩下的部分绘制完成后需要仔细检查,这一般通过自查和组织评审来完成。通常在人工检查之前可以由软件来完成初步的检查,可以发现一些比较基础的错误,比如输出管脚连接了输出管脚(通常应该连接到输入管脚)。检查的步骤如下:

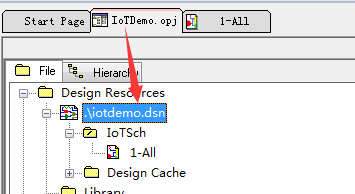

首先切换到项目所在的标签页,然后点击要检查的DSN。

接下来依次选择Tools->Design roules check...菜单

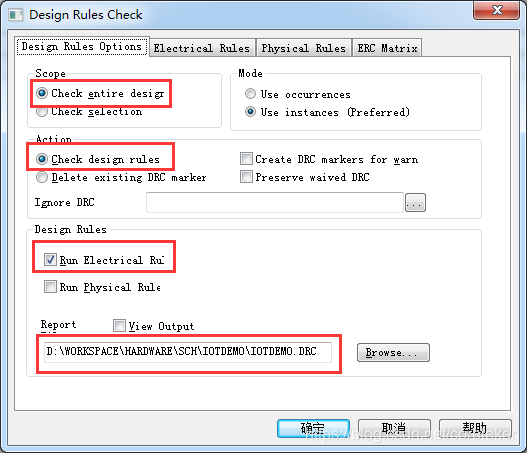

在弹出的对话框中选择ERC Matrix标签,设置规则。

上图中,Output和Output相连会产生错误,其他以此类推。点击小方块,可改变规则,但通常使用默认规则。

规则设置好之后,点击Design Rules Options标签,进行相应的设置后,点击OK可以进行DRC检查。

检查完成如有警告或错误产生会弹出如

本文详细介绍了嵌入式硬件开发中原理图的后期处理,包括DRC检查、元器件编号、封装属性添加、网表导出、BOM表生成以及打印原理图的步骤和注意事项,确保设计的准确性和一致性。

本文详细介绍了嵌入式硬件开发中原理图的后期处理,包括DRC检查、元器件编号、封装属性添加、网表导出、BOM表生成以及打印原理图的步骤和注意事项,确保设计的准确性和一致性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?