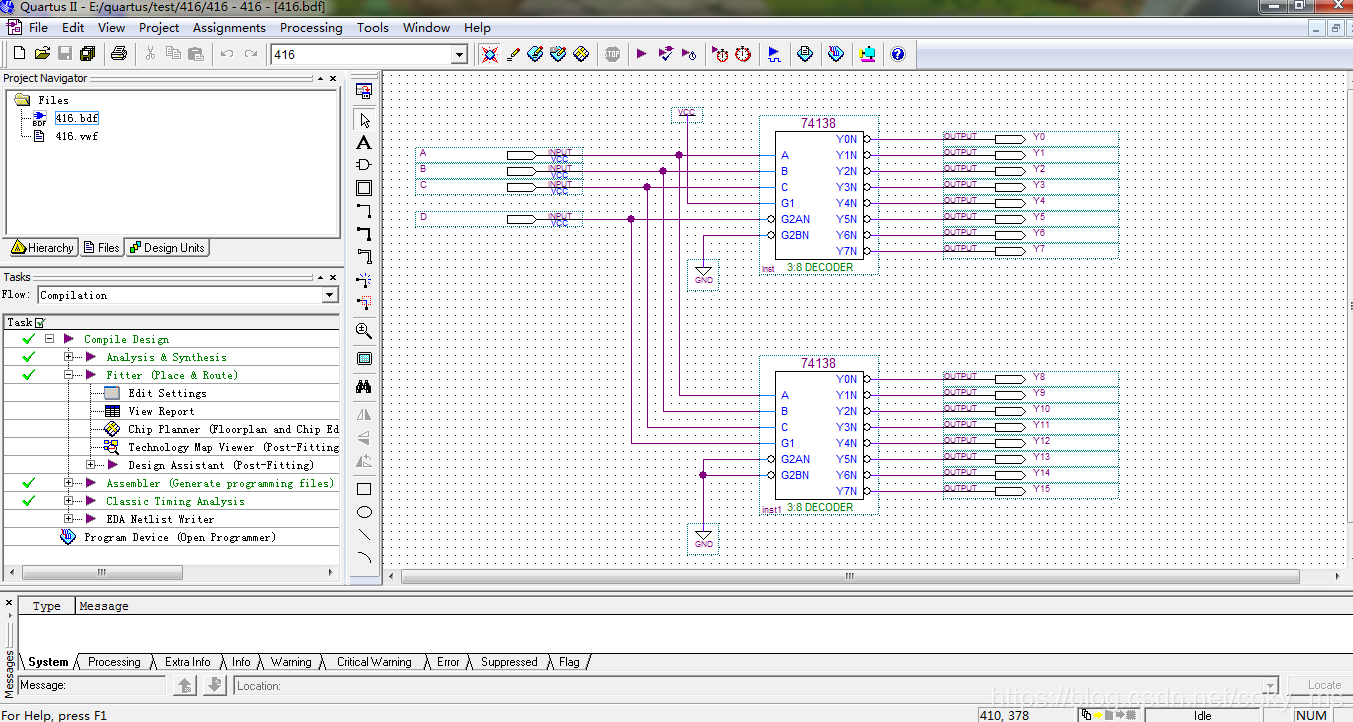

第一次进行博客的编写,任务是在quartus 9.0中进行4-16译码器的拼接,所需要的材料便是两个3-8译码器和一些其他的小零件。通过对数字电路的知识的学习,我们是可以完成这个任务的。

第一步是进行文件的建立。

运行quartus软件,建立BDF文件,然后进行两个74138译码器的拼接。可以通过双击绘图界面进行电路元件的添加,并添加各种管脚(名字自定义)使得电路连接通顺。如下图所示:

然后进行电路的编译,检查是否有问题。

第二步进行仿真文件的建立,file中打开进行VWF文件的建立,如下图所示

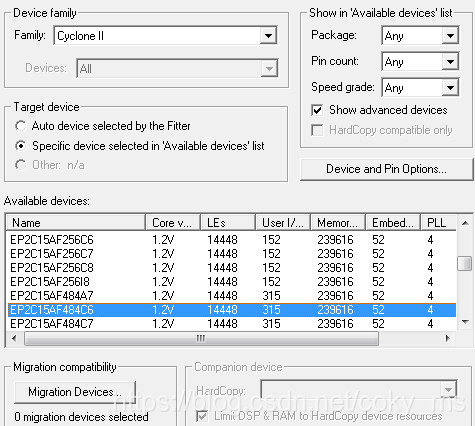

其中仿真设备的选择上,我选择的是如图所示的设备

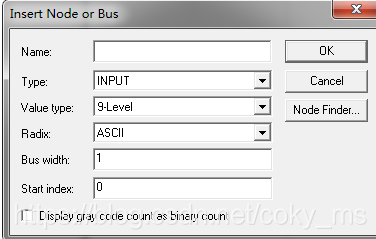

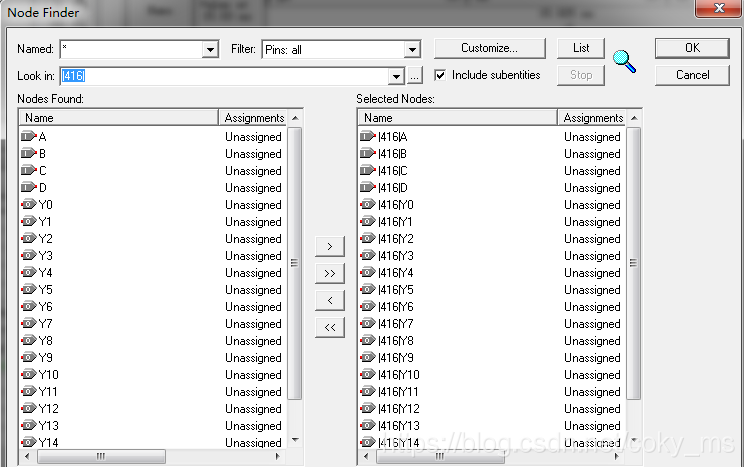

然后进行管脚的插入,通过对左方空白页右键insert,然后进行插入

然后是管脚的导入,如下图

最后就是进行仿真波形的设置,如下图

74138译码器拼接4-16译码器

最新推荐文章于 2024-07-16 09:56:36 发布

这篇博客介绍了如何在Quartus 9.0环境中通过组合两个74138译码器实现4-16译码器的设计过程。内容包括建立BDF文件、电路拼接、编译检查、仿真文件创建、选择仿真设备、插入和导入管脚以及设置和运行仿真波形。

这篇博客介绍了如何在Quartus 9.0环境中通过组合两个74138译码器实现4-16译码器的设计过程。内容包括建立BDF文件、电路拼接、编译检查、仿真文件创建、选择仿真设备、插入和导入管脚以及设置和运行仿真波形。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8268

8268

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?