#include <iostream>

using namespace std;

int main(){

int a = 5;

int b = 5 | 48;

cout<<b<<endl;

}

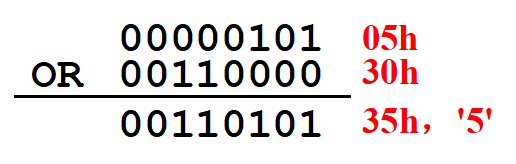

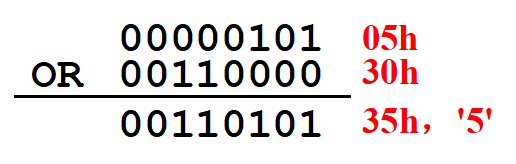

本文展示了一个使用C++进行位运算的简单示例,主要介绍了如何使用按位或运算符来修改整型变量的值。

本文展示了一个使用C++进行位运算的简单示例,主要介绍了如何使用按位或运算符来修改整型变量的值。

#include <iostream>

using namespace std;

int main(){

int a = 5;

int b = 5 | 48;

cout<<b<<endl;

}

1281

1281

8474

8474

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?