:

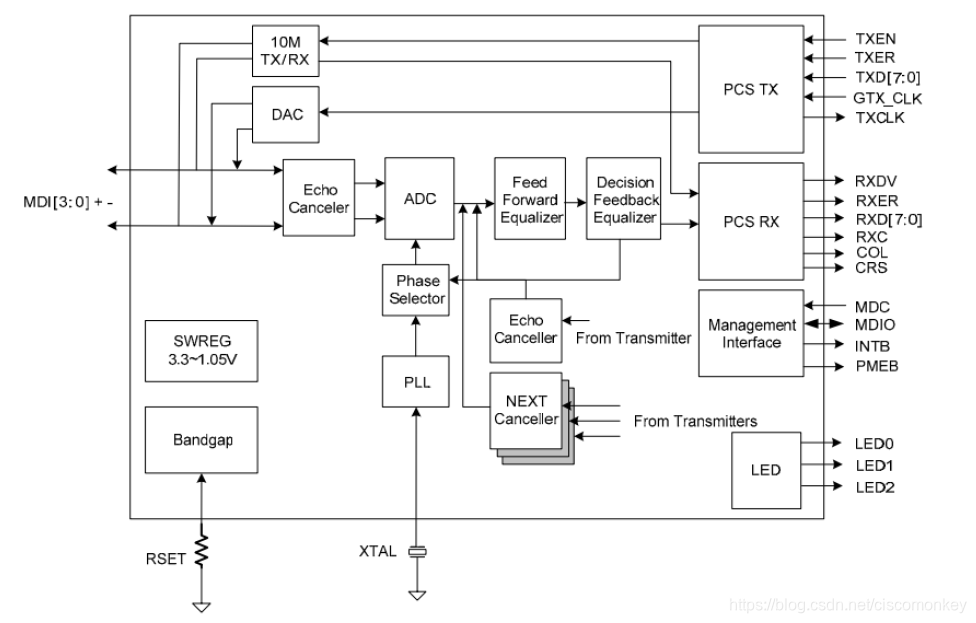

该芯片主要由三部分组成:

发送端物理编码子层(PCS TX)、接收端物理编码子层(PCS RX)和配置接口(management interface) 。PCS RX主要是用来接收外部模拟信号,并将接收到的模拟信号进行处理,如魔术转换、交叉检测及自动校正、极性校正、自适应均衡、串扰消除、回声消除等,最终将处理好的数字信号传输给FPGA。management interface就是用来配置或读取PHY芯片内部的寄存器。

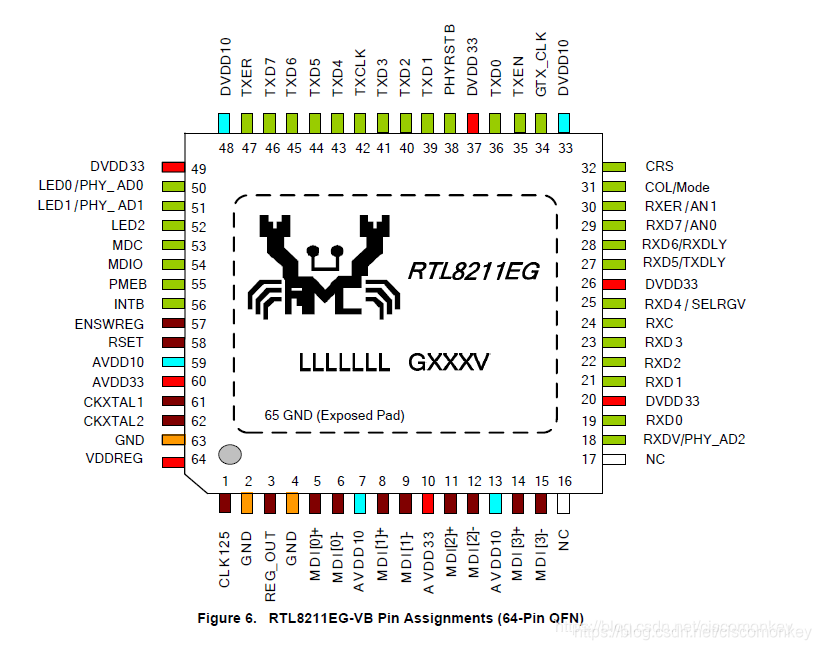

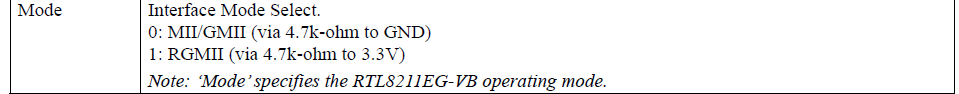

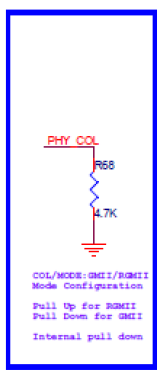

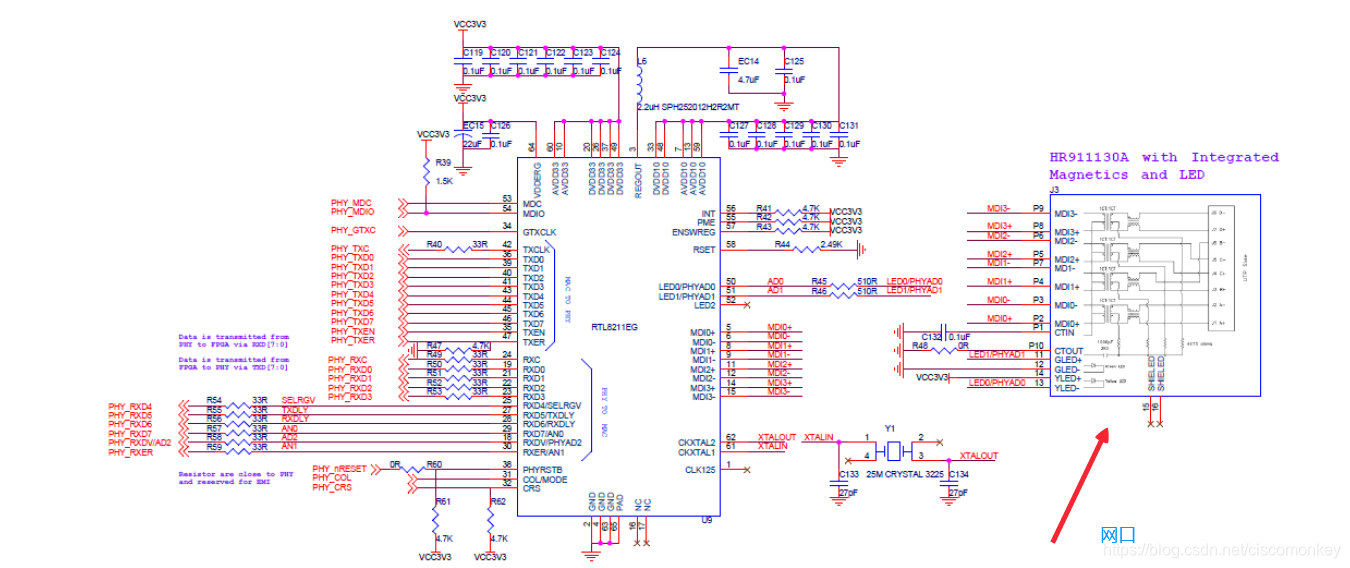

RTL8211EG芯片的管脚,由于RTL8211EG芯片有两种接口方式:RGMII和GMII

上述图片来自于某家FPGA机构gao石,我发现又tm有错。发送/接收 口描述错了

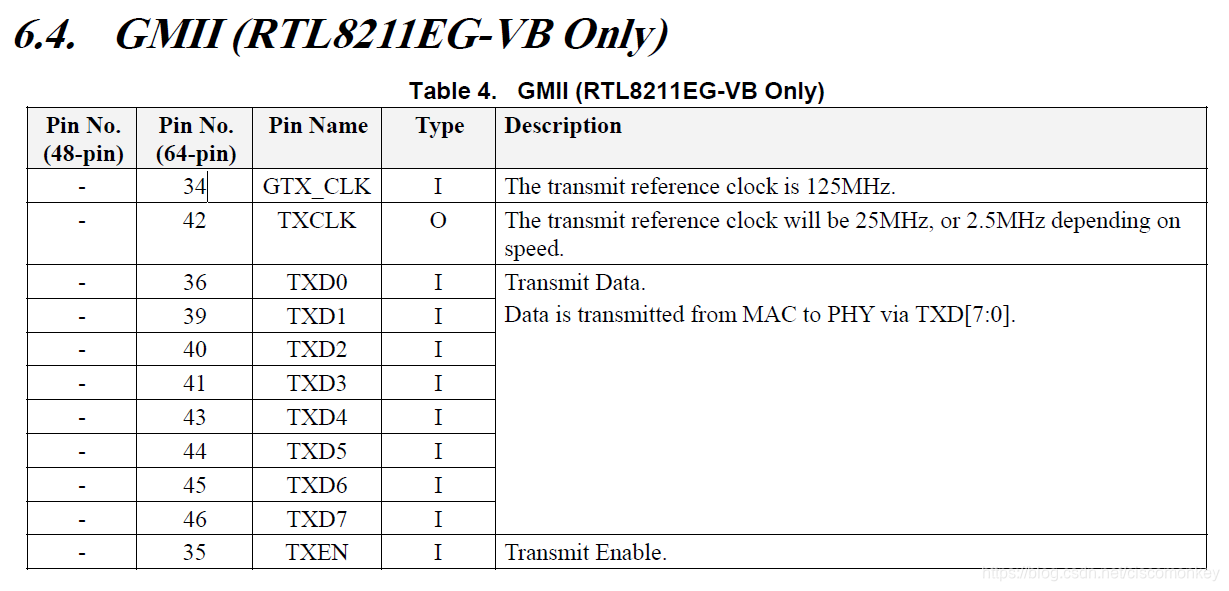

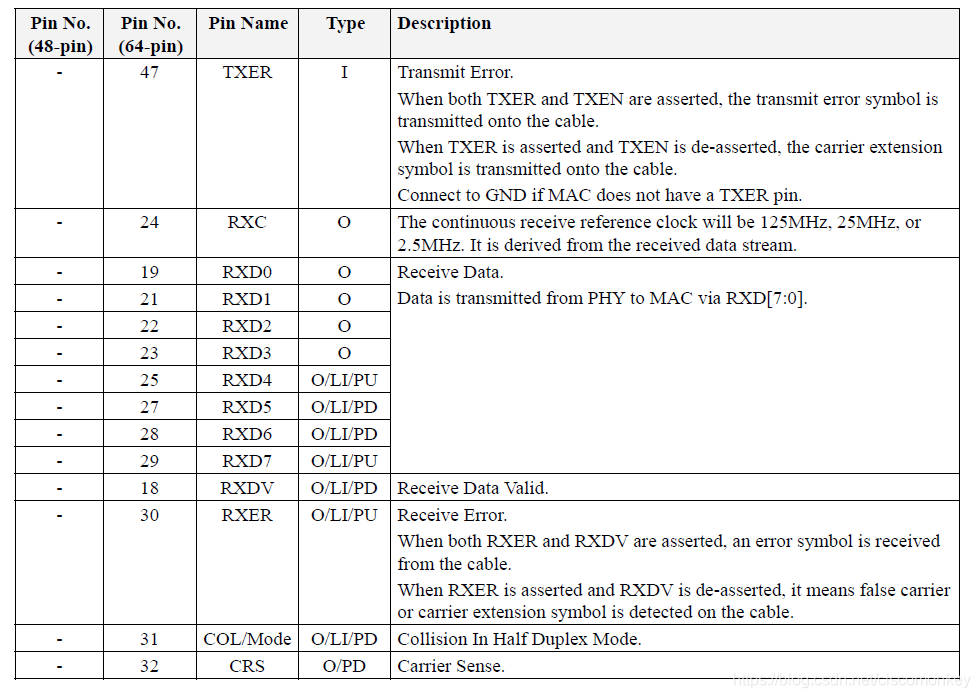

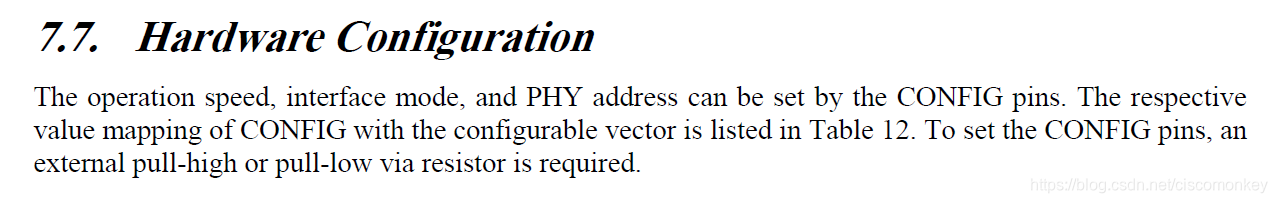

以下来自于官方的datasheet:

下图说明了这款PHY芯片的管脚分配,在GMII模式下。每个管脚的意义。

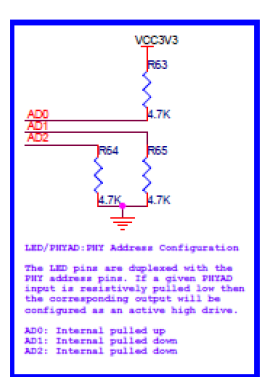

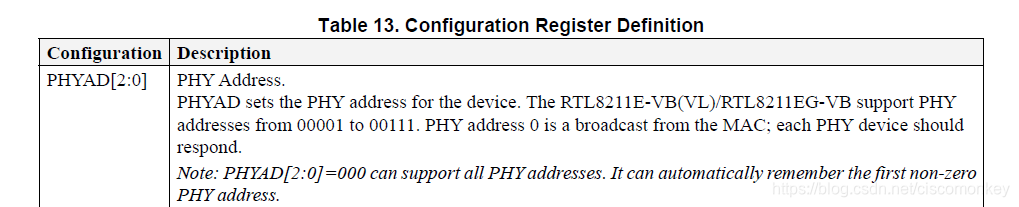

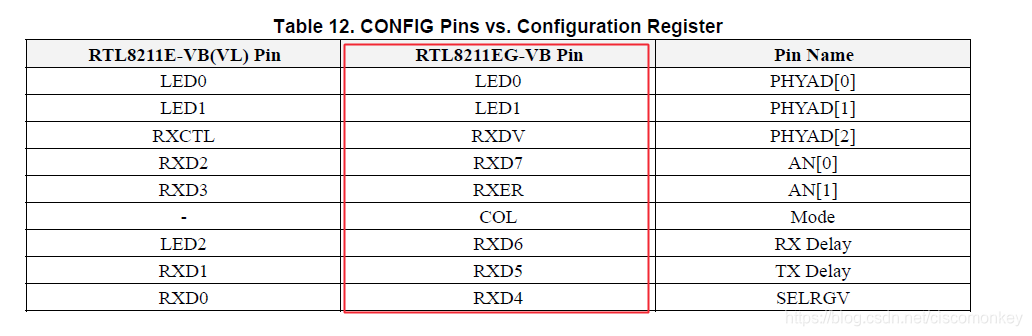

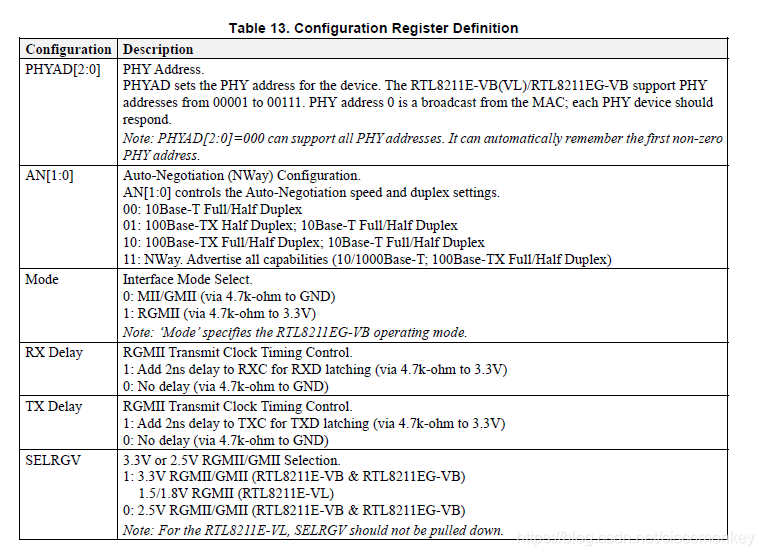

某石的原理图,将PHYAD0上拉=1,PHYAD1下拉=0,PHYAD2下拉=0 倘若三个PHY全是0,那么说明这是来自MAC的一个广播,所有的PHY芯片都必须回应。

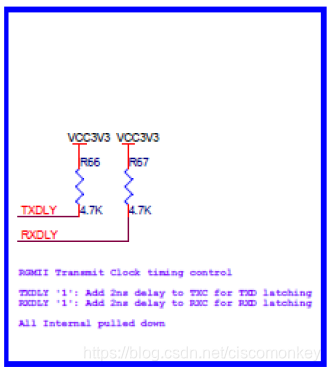

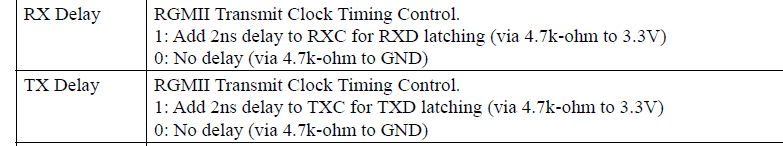

下面来看RX—Delay管脚

RX—Delay和TX-Delay引脚都为上拉状态,则表示在RGMII接口的传输时序中为了给TXD和RXD引脚锁存而给TXC和RXC引脚延时2ns

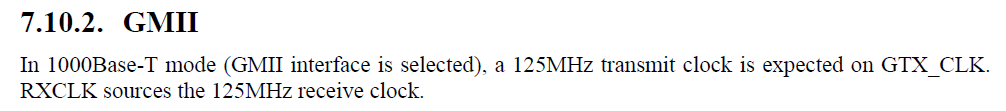

PHY-COL管脚接地,所以为GMII模式。PHY-COL为下拉状态,则芯片通过GMII接口完成与MAC层之间的数据传输。

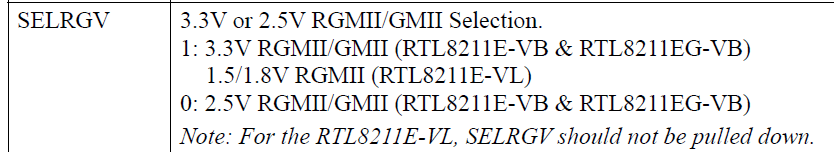

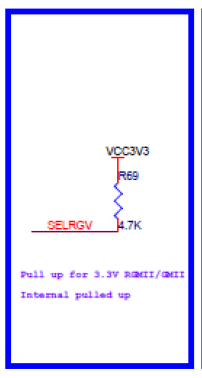

SELRGV引脚为上拉状态,则表示GMII接口为3.3V的电压标准。

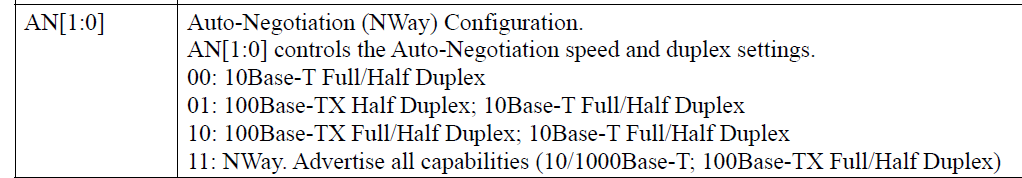

AN0和AN1引脚都为上拉状态,则表示配置为自动协商模式,支持10/1000Base-T,100Base-TX 全/半双工模式。

’—

‘-------------------

所以,由于我们使用FPGA完全代替了MAC芯片,所以FPGA的管脚直接与RTL8211EG芯片内部的PCS TX和PCS RX接口相连,RTL8211EG芯片的MDI【3:0】引脚与以太网变压器接口HR911130相连,完成以太网数据包的发送与接收。

’--------------------------------------------------------------------------

总结下:

本文深入解析RTL8211EG芯片结构与工作原理,包括发送端物理编码子层(PCSTX)、接收端物理编码子层(PCSRX)及配置接口(managementinterface)的功能。阐述了其在RGMII和GMII两种接口方式下的管脚分配与作用,以及FPGA如何替代MAC芯片与其交互。

本文深入解析RTL8211EG芯片结构与工作原理,包括发送端物理编码子层(PCSTX)、接收端物理编码子层(PCSRX)及配置接口(managementinterface)的功能。阐述了其在RGMII和GMII两种接口方式下的管脚分配与作用,以及FPGA如何替代MAC芯片与其交互。

2943

2943

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?