最近在做一个阻抗心率的项目,原理是利用人体的阻抗,随着血液的循环,会呈现一定的规律性变化,变化过程中会有0.5ohm左右的变化。但是在项目过程中遇到信噪比差的问题。在这里对问题的思路定位做一个总结和知识点的整理。

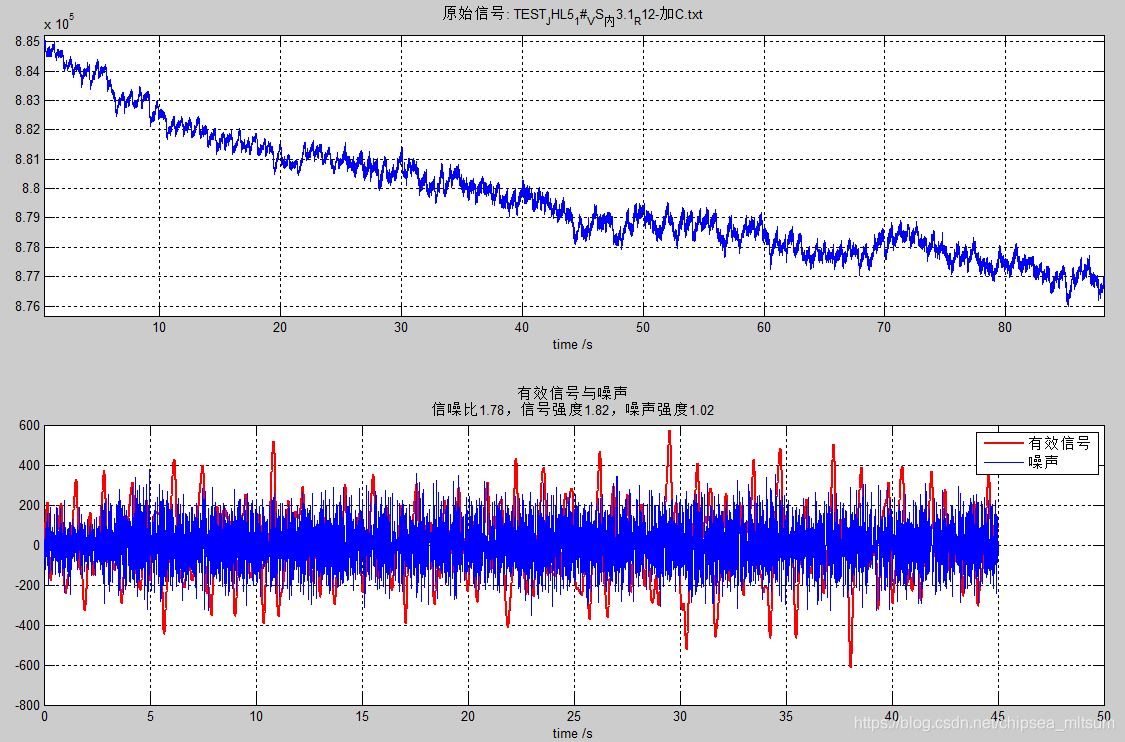

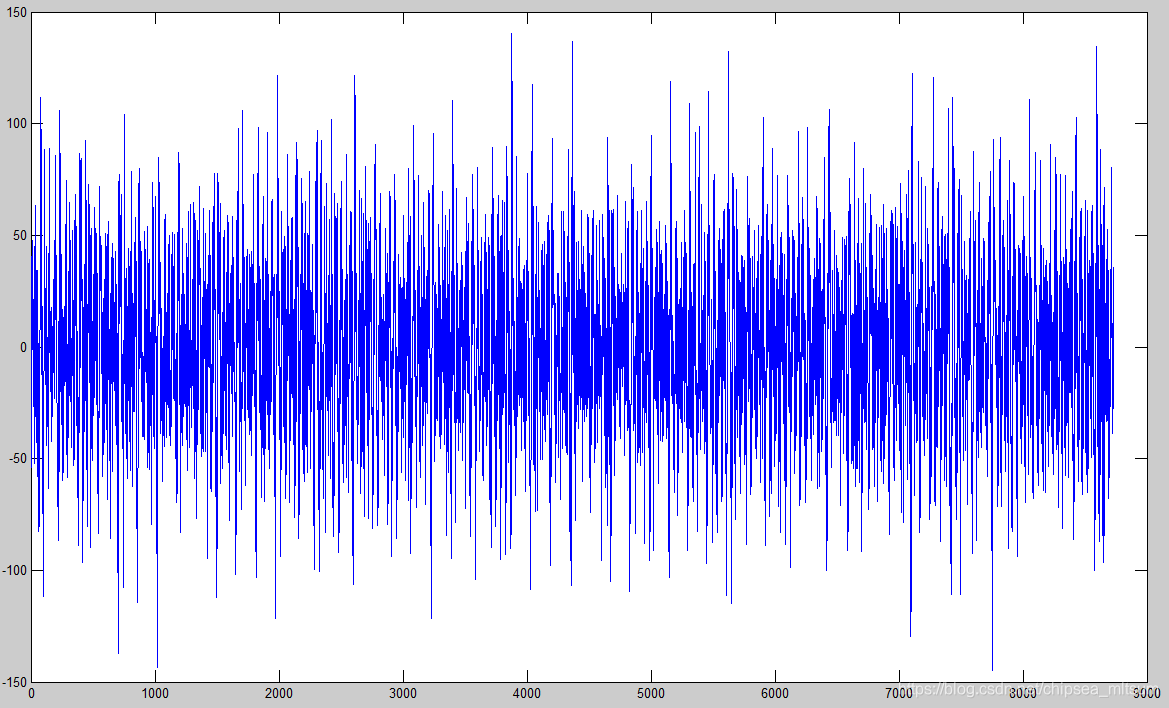

现象如下:

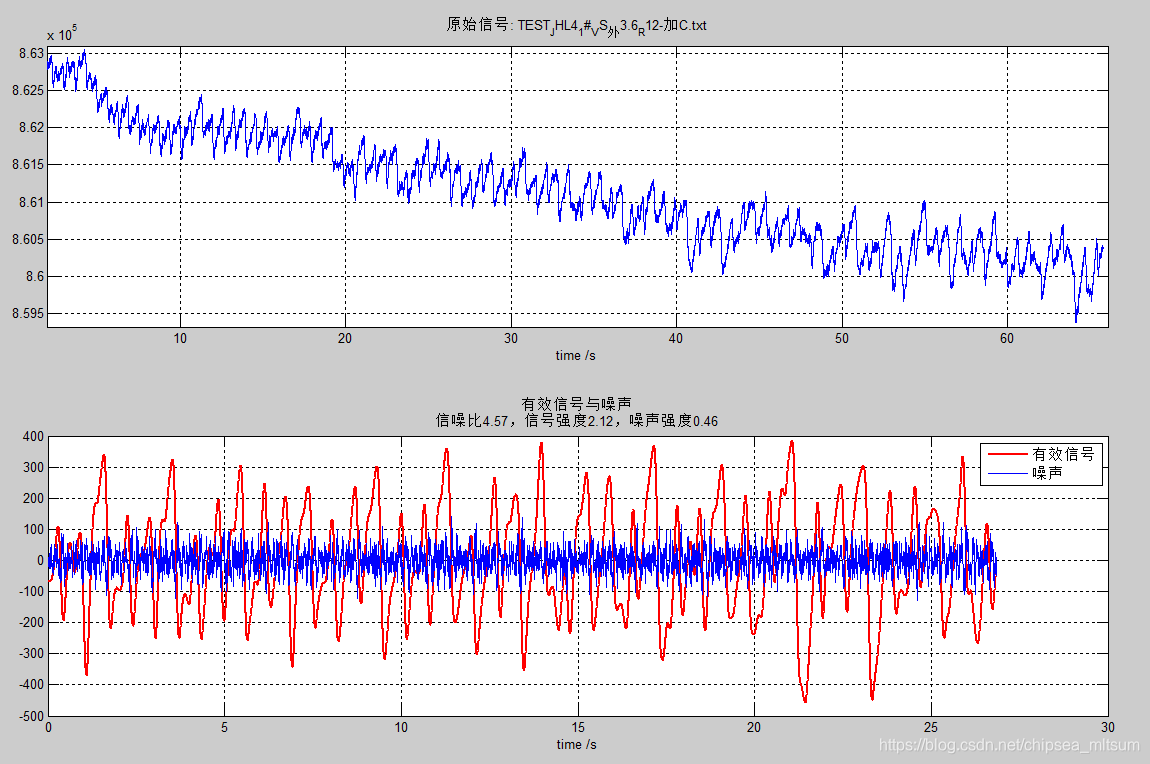

正常信号示意图:

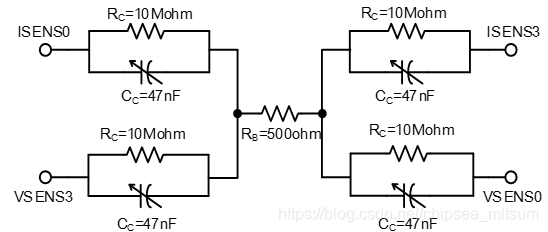

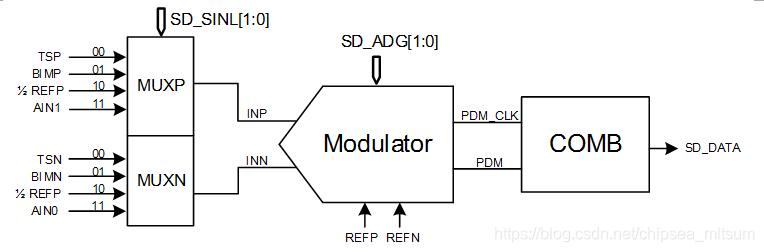

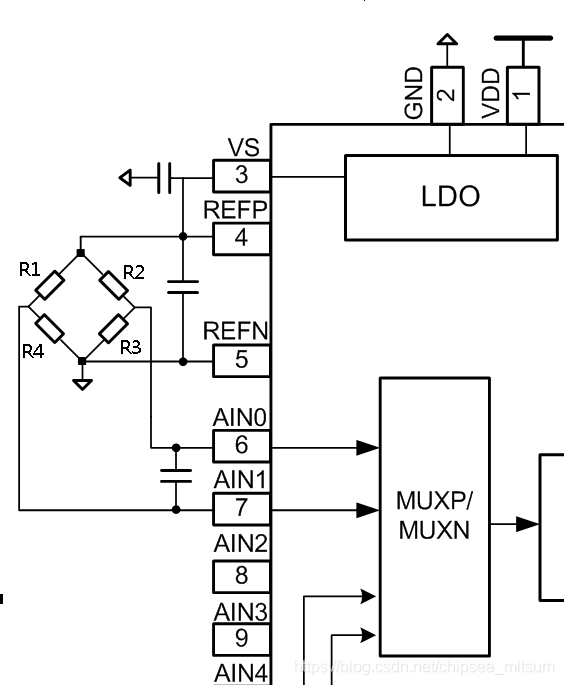

测量原理如下:

原因分析:

已经确认了测量芯片的软件配置和硬件电路配置。但是信噪比仍然差。因此分析可能是VS的原因。因为VS未经过Trimming, 发现烧录程序后,实测的VS和软件配置的VS值相差较大,比如软件配置VS=3.0V,但实测可能到2.8V或者3.4V。因此怀疑是VS的原因。

实验确认:

现象1: 使用PCBA的LDO直接供电VS,发现外部电源测得的VS信噪比较内部电源好很多;

现象2: 使用外部电源DC直接供电VS,发现外部电源测得的VS信噪比较内部电源好很多;

理论支撑1:

A:如何区分ADC的相对测量和绝对测量,为什么说称重是相对测量,而阻抗测量是绝对测量?

称重时电路为一个惠斯通电桥:

AIN0=R4/(R1+R4)*VS AIN1=R3/(R1+R3)*VS

AIN0-AIN1=[R4/(R1+R4) -R3/(R1+R3)]*VS -ADC输入的电压大小;

ADC=(AIN0-AIN1)/VS*7FFFFF(24bit) - 电压大小转换为AD值;

综上得:ADC=[R4/(R1+R4) -R3/(R1+R3)]*7FFFFF(24bit) -约去了VS,因此称重时和VS本身的电源质量无关,此为相对测量。

而在测量阻抗(绝对测量)时将人体等效为一个阻容网络,让一路电流流过该网络产生一个和网络阻抗成正比的压降,通过ADC检测该压降可换算成阻容网络的阻抗(校准线性时,校准电阻的AD值是根据VS计算出来的,因此根据K值计算阻抗时也相当于参考了VS)因此为相对测量。

理论支撑2:分析电路噪声的思维框架是什么?如何评估噪声量?如何对噪声进行频谱分析?

电路中的噪声大致可分为内部噪声和外部噪声两种。

外部噪声:

电源噪声:

例如心率信号测量时,采用纹波较差的电源供电就影响测量信号,使得信号测量的信噪比变差。

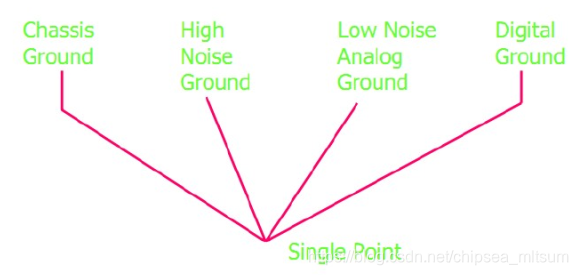

地噪声:

例如心率信号测量时,采用如果直接用非隔离串口来进行测量,或者在测量时,笔记本或者PC连接市电,就会从GND端 引入纹波,导致信号信噪比变低。

值得一提的是,实际电路中,任何两点的电位都不可能完全相等,电流流经地线,会产生电位差。因此地连接也推荐星型

连接。或者模拟地和数字地单点连接。

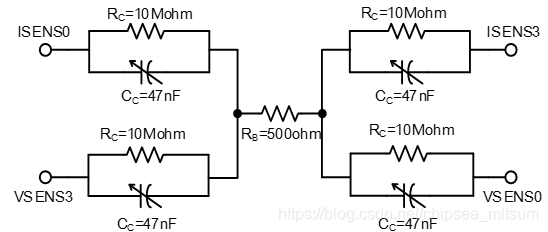

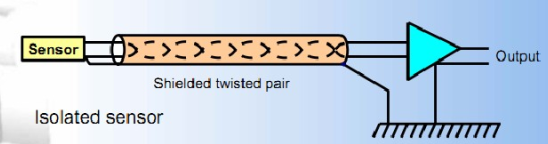

射频噪声:

例如之前在五所做的芯片的射频分析,为什么需要用法拉第箱做屏蔽?就是因为不想引入射频干扰。再例如传感器进行测 量时为什么不推荐引线太长?原因其一就是因为担心引入射频干扰。一般的做法是在输入端滤波,屏蔽或者采用双绞线方式。

还有的就是为什么WIFI模组,BLE模组很多都会用铁壳屏蔽,也是为了屏蔽RF干扰。

内部噪声:

内部噪声来源于信号链中的电路元件。比如电阻,传感器,ADC,IC中各模块。

以电阻为例:电阻在工作时存在本身属性决定的热噪声,以及电流流过产生的噪声。

再比如,本案例中,IC内部的ADC和BIM模块本身会存在噪声,这些噪声同样会影响信号的信噪比。

如何评估噪声量?

单位:uVPP

峰峰值噪声:指的是波峰到波谷之间的距离。

有效值噪声:也称为均方根噪声,其运用的是一段时间内的所有噪声点,因此比较精确。

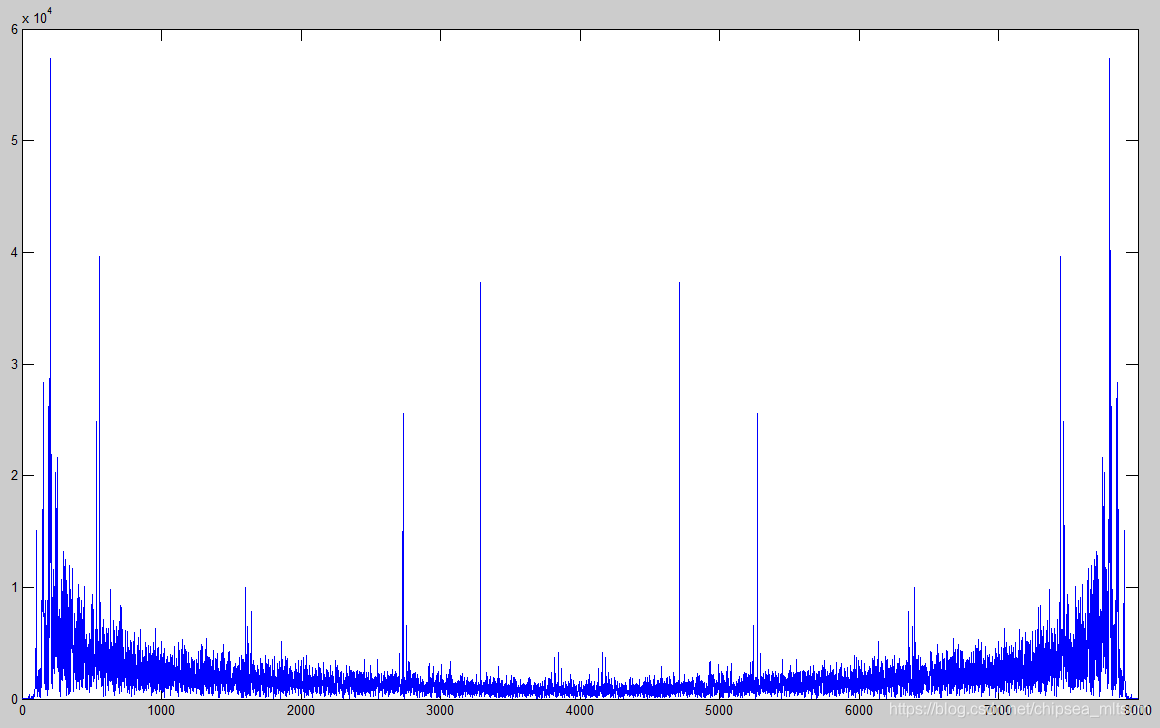

如何进行噪声的频谱分析? 以MATLAB为例:

信号的噪声分量为noise_S:

Fast Tourier transform:

// Fast Fourier transform

noise_S_fft=fft(noise_S,8000);

noise_S_fft_abs=abs(noise_S_fft); // FFT return the result is complex number a+bi, so abs() it.

plot(noise_S_fft_abs);

/*********************************************

Y = fft(x) returns the discrete Fourier transform (DFT) of vector x, computed with a

fast Fourier transform (FFT) algorithm.

Y = fft(X,n) returns the n-point DFT. fft(X) is equivalent to fft(X, n) where n is the

size of X in the first nonsingleton dimension. If the length of X is less than n, X is

padded with trailing zeros to length n. If the length of X is greater than n, the

sequence X is truncated. When X is a matrix, the length of the columns are adjusted in the same manner.

*********************************************/

result is :

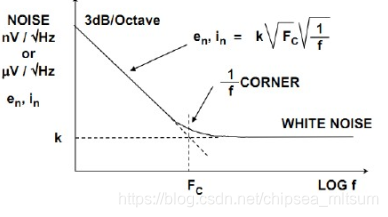

噪声谱密度:

高频下的噪声为白噪声(其频谱密度不会随着频率变化而变化)。但在低频下,噪声频谱密度会以3db/倍频上升,密度在此区域和频率成反比,因此这种噪声也成为1/f噪声。

理论支撑3:

进行电源LDO或者VS的滤波时,滤波电容的选取对信号的实际影响效果如何?请给出理论支撑和实际论证?

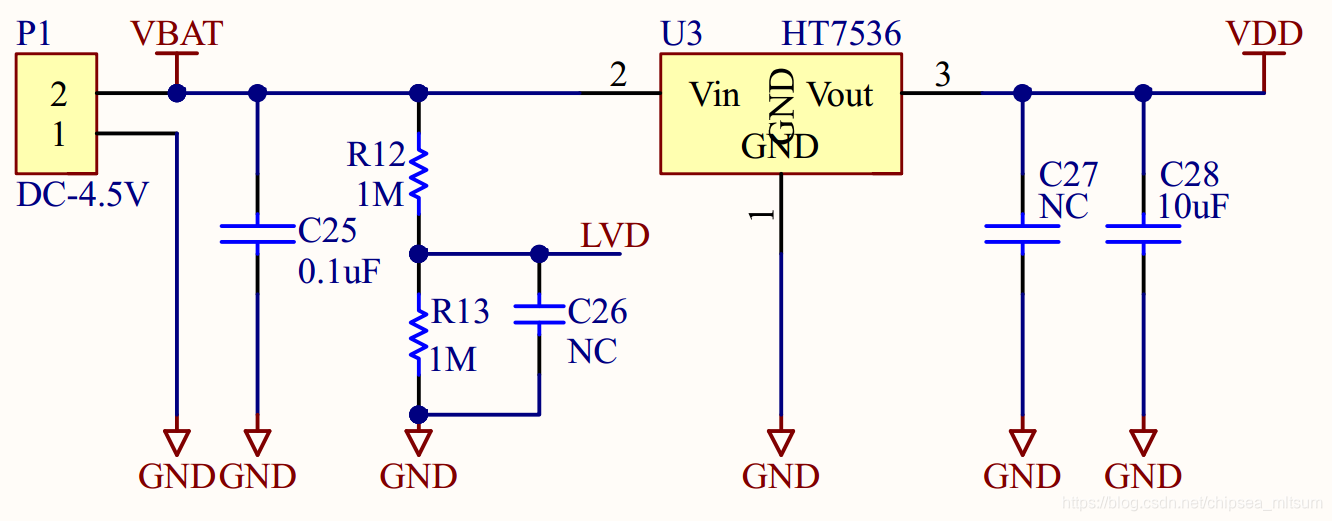

A: 举一个例子,如下图为进行电源滤波的一个实例。LDO出来采用了一个10uF的电容做滤波。

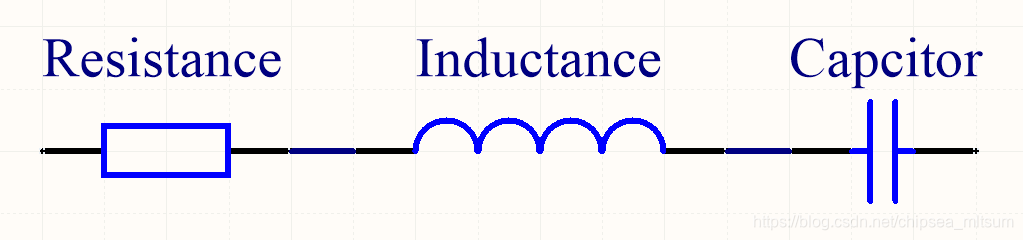

实质上, 电容由于自身的构造,材料等因素,电容的模型可以等效为:ESR(等效串联电阻)串联一个ESL(等效串联电感),再串联一个电容。会自带一个谐振频率点。在这个谐振频率点时,电容的容抗=电容的感抗,同时容抗最低。

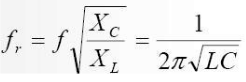

谐振频率计算公式:

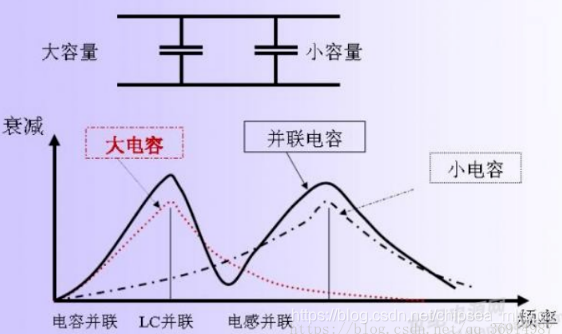

如下图:

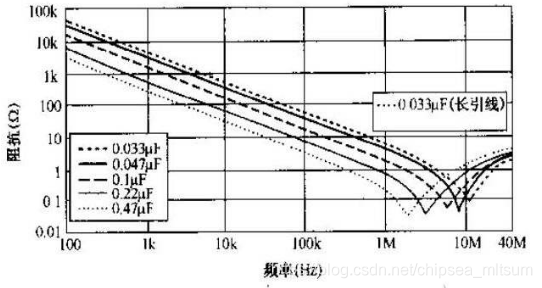

电容的容量和谐振频率成反比,容量越大,谐振频率越低。当外部作用于电容的频率高于谐振频率时,电容呈现感性,当外部作用于电容的频率低于其谐振频率时,电容呈现容性。

因此如上电路中,为了滤除电源中的低频纹波,需要一个较大的电容,在低频时呈现高阻抗。但此时滤波电路对于高频干扰滤除效果较差,应该采取什么措施呢?

如上电路图,在LDO出来时,加了一个NC电容,为的就是并联一个小电容,滤除高频干扰。而未指定具体值的原因是为了方便调整。

当一个大电容,并联一个小电容搭配时,频率-阻抗图如下:

多电容并联的原理也是一样的。

结论:高频干扰用小电容,在高频段呈现高阻抗,低频干扰用大电容,在低频段呈现高阻抗。

理论支撑4:

磁珠对信号的影响如何?请给出理论支撑和实际论证?

磁珠是电容、电感、电阻的复合体,相当于三者的并联,主要场合是对某个频段的抑制,相对于电感+电容的组合来说,磁珠作用于高频,一般是>100MHz,且在高频段的电阻特性为主要特征,所以不但可以过滤噪音,还可以通过电阻来消耗噪音(非电阻的滤波器,理论上只是导走噪音,而不是损耗噪音)。

本文针对阻抗心率项目中遇到的信噪比差问题,深入分析了内外部噪声源及其影响,探讨了电源质量和滤波技术对信号质量的作用,提出了通过优化电源管理和电路设计提高测量精度的方法。

本文针对阻抗心率项目中遇到的信噪比差问题,深入分析了内外部噪声源及其影响,探讨了电源质量和滤波技术对信号质量的作用,提出了通过优化电源管理和电路设计提高测量精度的方法。

823

823

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?