Signal Tab使用指南

1.简介

Fpga调试有两个工具,一种是Modelsim,另一种是SignalTab。Modelsim是仿真软件,是用软件来模拟fpga的时序信号,以此来观察fpga各个变量的信号变化过程。这种是软件模拟出来的,也是理想化的情况。常用于下板子之前测试代码是否正常运行。SignalTab是需要把代码下载到开发板,然后fpga在运行的时候,实时捕获到每个变量对应于真实器件的信号。SignalTab使用fpga内部的逻辑资源和RAM资源,使用时只需将一根JTAG接口的下载电缆连接到开发板,数据通过JTAG接口从FPGA传送回Quartus。使用Quartus开发项目,先使用Modelsim测试代码编译是否正确,和每个变量的结果是否符合预期。完成仿真之后,再把代码下载到开发板,然后用SignalTab采集fpga真实运行时的信号变化,最终以SignalTab的结果为准。

2.配置SignalTab

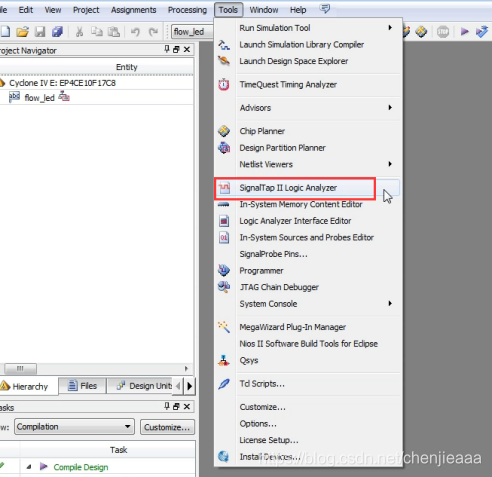

(1)打开SignalTab界面

按照下图方式打开界面

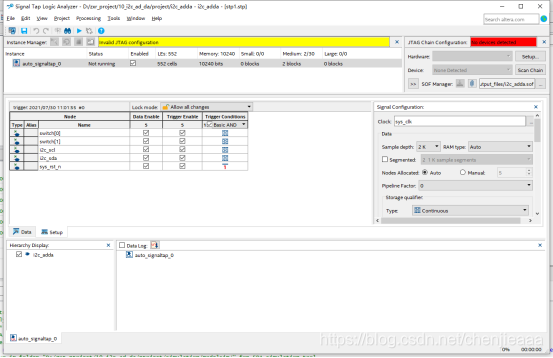

(2)增加需要捕获的信号

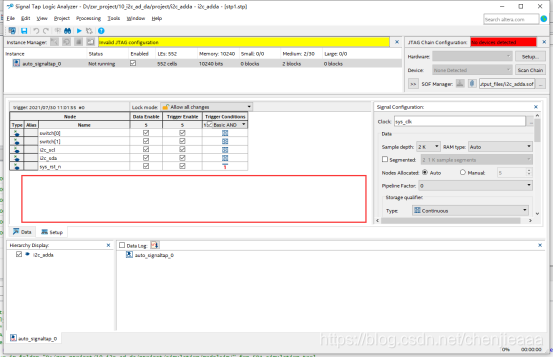

下图中,在空白处双击即可打开信号(变量)列表:

在Filter下拉框处选择Signal Tab: pre-synthesis,然后点击List按钮,这样就可以在下面左边框里看到所有的变量了:

本文详细介绍了如何使用SignalTab进行FPGA信号配置、捕获时钟和变量,从Modelsim仿真到实际开发板调试的全过程,包括步骤、配置细节和信号调试技巧。

本文详细介绍了如何使用SignalTab进行FPGA信号配置、捕获时钟和变量,从Modelsim仿真到实际开发板调试的全过程,包括步骤、配置细节和信号调试技巧。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5039

5039

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?