在实验室环境中使用 Vivado Logic Analyzer

Vivado Logic Analyzer 功能已集成到 Vivado IDE 和 Vivado Lab Edition 中。要使用 Vivado Logic Analyzer 功能对实验

室环境内的目标开发板上运行的设计进行调试,需执行以下 3 项操作:

• 在实验室机器上安装并运行 Vivado Lab Edition。如需了解更多详情,请参阅本用户指南的 Vivadoo Lab Edition 部

分。

• 在实验室机器上安装并运行完整版 Vivado IDE。

• 在远程实验室机器上安装最新版 Vivado Design Suite 或 Vivado Hardware Server (Standalone),并在本地机器上使

用 Vivado Logic Analyzer 功能连接至 Vivado Hardware Server (hw_server) 的远程实例。

相关信息

Vivado Lab Edition

连接到实验室机器上运行的远程 hw_server

如果您可通过网络连接至实验室机器,那么也可以通过连接至该远程实验室机器上运行的硬件服务器 (Hardware

Server) 来连接到目标开发板。以下提供了使用 Vivado 逻辑分析器功能来连接到实验室机器上运行的 Vivado Hardware

Server(Windows 平台上的 hw_server.bat 或 Linux 平台上的 hw_server)的步骤:

1. 在实验室机器上安装最新版本的 Vivado Design Suite 或 Vivado Hardware Server (Standalone)。

重要提示!您无需在实验室机器上安装完整的 Vivado Design Suite 或 Vivado Lab Edition 同样可使用远程

硬件服务器功能。但如果您想要在实验室机器上使用 Vivado 硬件管理器功能(例如,Vivado Logic

Analyzer 或 Vivado Serial I/O Analyzer),则需在实验室机器上安装 Vivado Lab Edition。并且也无需任何

软件许可证,即可运行硬件服务器、Vivado Design Suite 硬件管理器中的任意功能以及 Vivado Lab

Edition。

2. 在远程实验室机器上启动 hw_server 应用。假定您已将 Vivado Hardware Server (Standalone) 安装至默认位置,并

且您的实验室机器为 64 位 Windows 机器,请运行以下命令行:

C:\Xilinx\VivadoHWSRV\vivado_release.version\bin\hw_server.bat

3. 在除实验室机器以外的其它机器上以 GUI 模式启动 Vivado IDE。

4. 遵循“连接至硬件目标并执行器件编程”章节中的步骤,建立与已连接到实验室机器的目标开发板的连接。但请勿

连接到 localhost 上运行的 Vivado CSE 服务器,而应改用实验室机器的主机名。

5. 遵循“设置 VIO 核以执行测量”章节及其后续章节中的步骤,以对硬件内的设计进行调试。

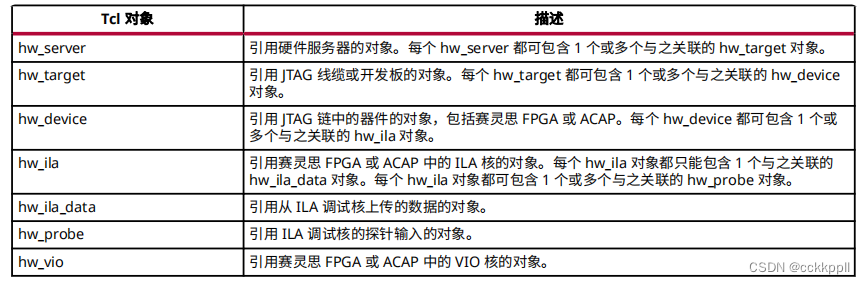

硬件管理器 Tcl 对象和命令的描述

您可使用 Tcl 命令与所测试的硬件进行交互。硬件可组织为一组分层式第一类 Tcl 对象(请参阅下表)。

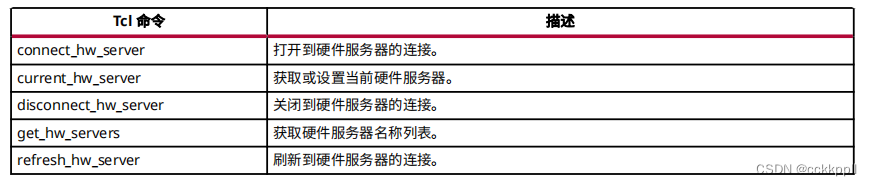

hw_server Tcl 命令的描述

下表包含用于与硬件服务器进行交互的所有 Tcl 命令的描述。

hw_target Tcl 命令的描述

下表包含用于与硬件目标进行交互的所有 Tcl 命令的描述。

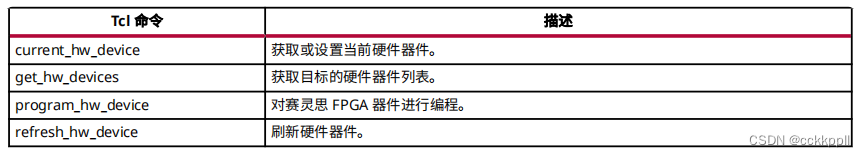

hw_device Tcl 命令的描述

下表包含 hw_device Tcl 命令的描述。

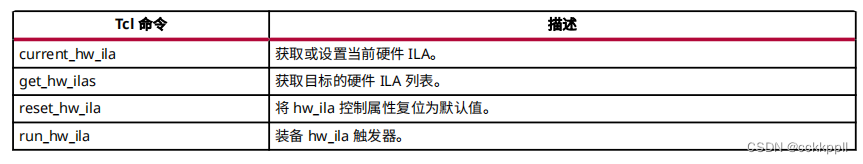

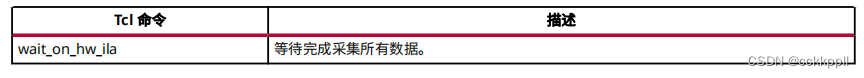

hw_ila Tcl 命令的描述

下表包含 hw_ila Tcl 命令的描述。

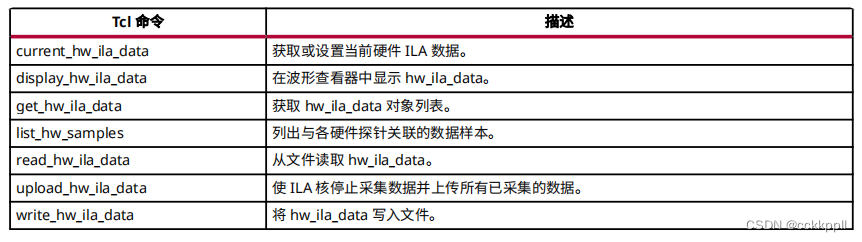

hw_ila_data Tcl 命令的描述

下表包含 hw_ila_data Tcl 命令的描述。

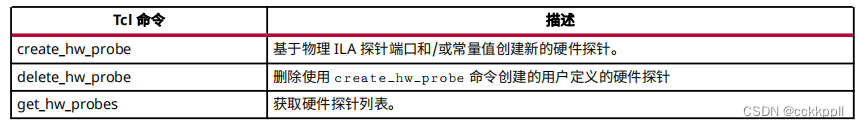

hw_probe Tcl 命令的描述

下表包含用于与采集的 ILA 数据进行交互的所有 Tcl 命令的描述。

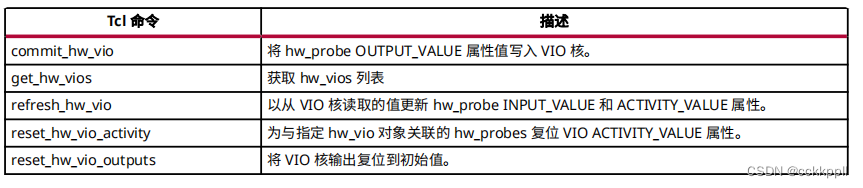

hw_vio Tcl 命令的描述

下表包含用于与 VIO 核进行交互的所有 Tcl 命令的描述。

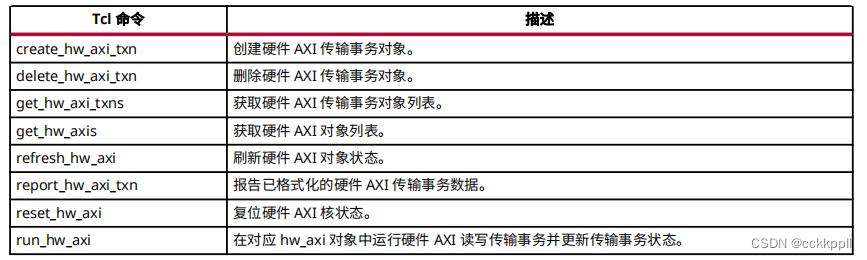

hw_axi 和 hw_axi_txn Tcl 命令的描述

下表包含用于与 JTAG-to-AXI Master 核进行交互的所有 Tcl 命令的描述。

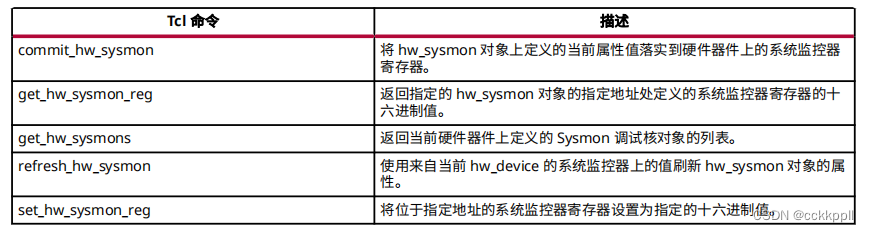

hw_sysmon Tcl 命令描述

下表包含与系统监控器核进行交互的所有 Tcl 命令的描述。

本文详细介绍了如何在实验室环境中使用VivadoLogicAnalyzer对设计进行调试,包括安装VivadoLabEdition和完整版IDE,以及通过VivadoHardwareServer进行远程连接的步骤。还涉及了Tcl命令在硬件管理和调试中的作用。

本文详细介绍了如何在实验室环境中使用VivadoLogicAnalyzer对设计进行调试,包括安装VivadoLabEdition和完整版IDE,以及通过VivadoHardwareServer进行远程连接的步骤。还涉及了Tcl命令在硬件管理和调试中的作用。

2479

2479

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?