适用于

7

系列、

UltraScale

和

UltraScale+ FPGA

和

MPSoC

的回读和验证

为

7

系列器件生成已加密文件和已经过身份验证的文件

注释

:

如需获取其它信息

,

请参阅《使用加密确保

7

系列

FPGA

比特流的安全》

(

XAPP1239

)

。

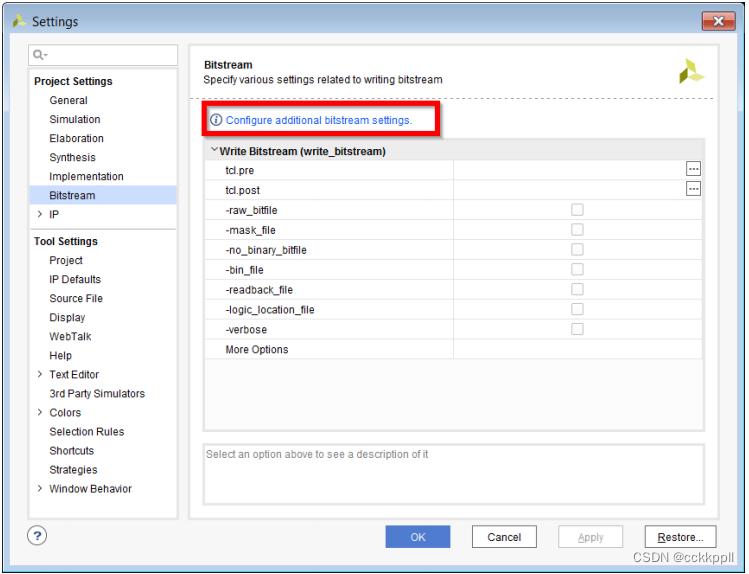

要生成加密比特流

,

请在

Vivado IDE

中打开已实现的设计。在主工具栏中

,

依次选择“

Flow

” → “

Bitstream Settings”

,

这样会显示“设置

(Settings)

”对话框。在此对话框顶部单击“

Configure Additional Bitstream Settings”。

这样会显示“编辑器件属性

(Edit Device Properties)

”对话框。选择左侧窗格中的“

Encryption

”。

在“编辑器件属性

(Edit Device Properties)

”对话框中

,

指定加密和密钥设置

:

• 加密设置

(Encryption Settings)

○

“

Enable Bitstream Encryption

”可设置为“

YES

”。

○

“

Select location of encryption key

”可设置为“

BBRAM

”或“

EFUSE

”。

-

密钥位置将嵌入加密比特流中。

-

当加密比特流下载至器件后

,

它会指令

FPGA

使用已加载到

BBR

或

eFUSE

密钥寄存器中的密钥来对加密的 比特流进行解密。

• 密钥设置

(Key Settings)

○

指定

HMAC

身份验证密钥和密码分组链接

(CBC)

起始值。

-

如果不指定这些值

,

则

本文详细介绍了如何在VivadoIDE中为7系列和UltraScale+/FPGA/MPSoC设备生成加密和身份验证过的比特流,涉及加密设置、密钥配置以及如何在设计中应用这些设置以确保安全。

本文详细介绍了如何在VivadoIDE中为7系列和UltraScale+/FPGA/MPSoC设备生成加密和身份验证过的比特流,涉及加密设置、密钥配置以及如何在设计中应用这些设置以确保安全。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?