在Verilog的建模中,时间尺度和延迟是非常重要的概念,设置好时间尺度和延迟,可以充分模拟逻辑电路发生的各种情况和事件发生的时间点,来评估数字IC设计的各种要求,达到充分评估和仿真的作用。注意延迟语句是不可综合的,只是用来数据建模或仿真。

1. 时间尺度

语法格式: `timescale 10ns/1ns

用关键字 `timescale标识,后面跟时间刻度,如:10ns/1ns,其中10ns表示基本时间刻度,就是每10ns作为一个刻度。1ns是精度,一般在仿真软件中的最小刻度。不同的仿真工具的精度不同,在modelsim中一般时间刻度为1ps,与`timescale 10 ns/1 ps的1 ps的设置是等效的。

例:在testbench 中时钟的建模:

`timescale 1ns/1ps //时间刻度为1 ns

module top_sim

(

);

reg CLK;

initial

begin

CLK = 1'b0;

#5;

forever

#5 CLK = ~CLK; //duty cycle 50%, period 10 ns; Frequency 100Mhz;

end

endmodule

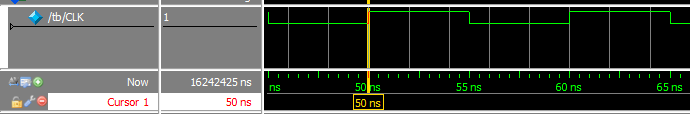

Modelsim 波形

`timescale 1ns/1ps //时间刻度为1 ns

本文详细介绍了Verilog中的时间尺度和延迟概念,时间尺度用于设置仿真精度,例如`timescale 10ns/1ns`。延迟则涉及连续赋值和寄存器赋值的延时类型,如普通赋值时延、隐式延时和内部/外部延迟。通过设置延迟,可以准确模拟逻辑电路中事件发生的时间点,确保仿真效果。

本文详细介绍了Verilog中的时间尺度和延迟概念,时间尺度用于设置仿真精度,例如`timescale 10ns/1ns`。延迟则涉及连续赋值和寄存器赋值的延时类型,如普通赋值时延、隐式延时和内部/外部延迟。通过设置延迟,可以准确模拟逻辑电路中事件发生的时间点,确保仿真效果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?