北邮22信通一枚~

跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章

持续关注作者 迎接数电实验学习~

获取更多文章,请访问专栏:

目录

一.代码部分

1.1 reg_74LS374.v

module reg_74LS374

(

input [7:0] D_in,

input clk,

output reg [7:0] D_out

);

always @ (posedge clk)

begin D_out <=D_in; end

endmodule1.2 reg_LS374_tb.v

`timescale 1ns/1ps

module reg_74LS374_tb();

reg clk;

reg [7:0] D_in;

wire [7:0] D_out;

initial begin

repeat(20) begin

clk=1'b0;#200;

clk=1'b1;#200;

end

$stop;

end

initial begin

repeat(2) begin

D_in=8'b0000_0001;#250;

D_in=8'b0000_0010;#250;

D_in=8'b0000_0100;#250;

D_in=8'b0000_1000;#250;

D_in=8'b0001_0000;#250;

D_in=8'b0010_0000;#250;

D_in=8'b0100_0000;#250;

D_in=8'b10000_0000;#250;

end

$stop;

end

reg_74LS374 reg_1

(

.clk(clk),

.D_in(D_in),

.D_out(D_out)

);

endmodule

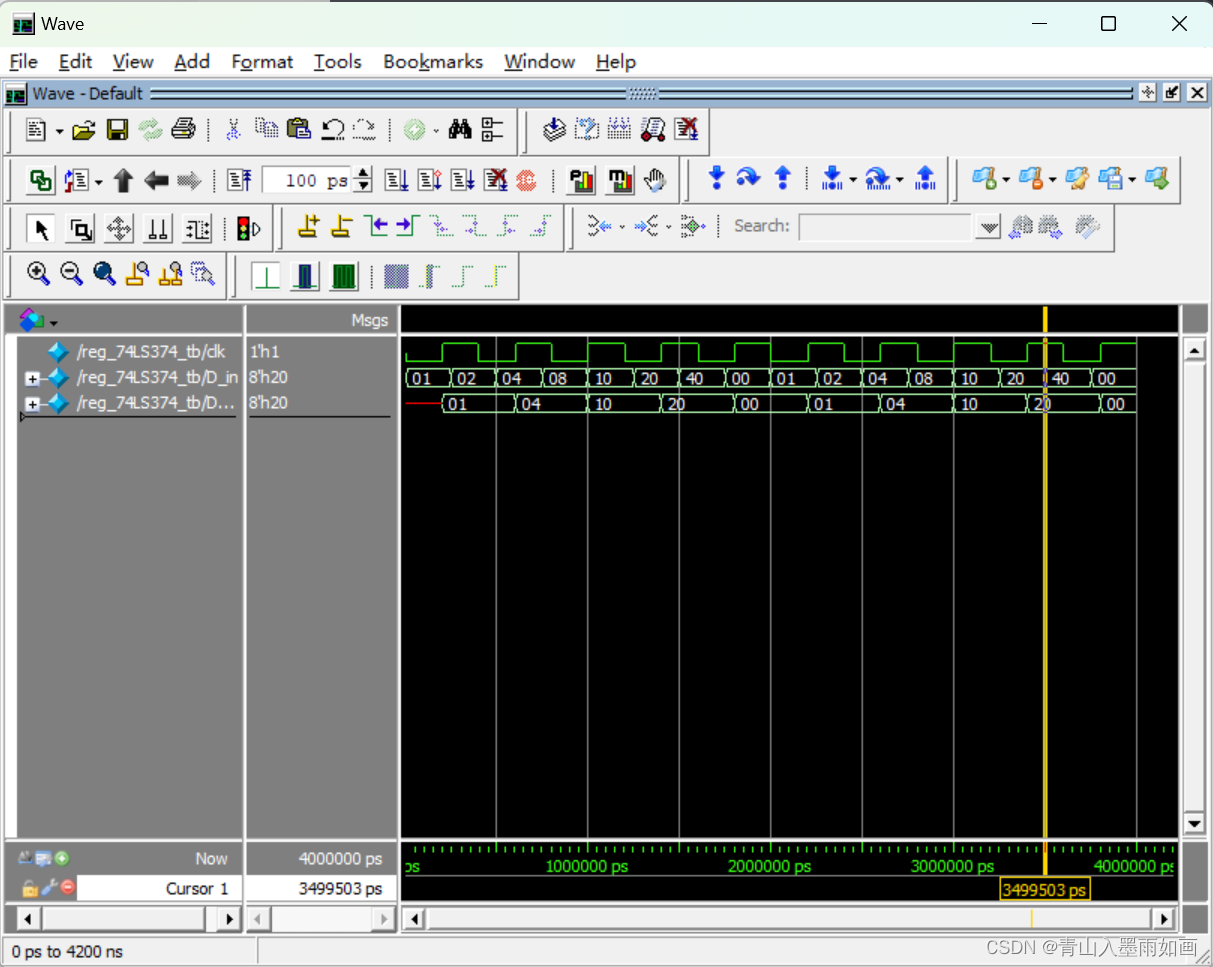

二.仿真测试效果

北邮信通院数字系统设计:74LS374电路实现与仿真

北邮信通院数字系统设计:74LS374电路实现与仿真

这篇文章介绍了北京邮电大学通信学院学生关于数字系统设计中74LS374集成电路的Verilog代码实现和相关仿真测试过程,展示了时序逻辑电路的工作原理和实验步骤。

这篇文章介绍了北京邮电大学通信学院学生关于数字系统设计中74LS374集成电路的Verilog代码实现和相关仿真测试过程,展示了时序逻辑电路的工作原理和实验步骤。

第九周实验(4)实现寄存器74LS374&spm=1001.2101.3001.5002&articleId=134418587&d=1&t=3&u=acb151d1e2a4443280c7cc66b714577e)

6994

6994

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?