北邮22信通一枚~

跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章

持续关注作者 迎接数电实验学习~

获取更多文章,请访问专栏:

目录

一.代码部分

1.1 JK.v

module JK

(

input clk,

input J,

input K,

input set,

input reset,

output reg q

);

always @(negedge clk or negedge reset or negedge set)

begin

if(!reset) //异步清零

begin

q<=1'b0;

end

else if(!set) //异步置1

begin

q<=1'b1;

end

else

begin

case({J,K})

2'b00:q<=q;

2'b01:q<=0;

2'b10:q<=1;

2'b11:q<=~q;

endcase

end

end

endmodule1.2 JK_tb.v

`timescale 1ns/1ps

module JK_tb;

reg clk;

reg J;

reg K;

reg set;

reg reset;

wire q;

JK dut(

.clk(clk),

.J(J),

.K(K),

.set(set),

.reset(reset),

.q(q)

);

initial begin

clk = 0;

J = 0;

K = 0;

set = 0;

reset = 0;

#100 reset = 1;

#100 reset = 0;

#100 set = 1;

#100 set = 0;

#100 J = 1;

#100 K = 1;

#100 J = 0;

#100 K = 1;

#100 J = 1;

#100 K = 0;

#100 J = 0;

#100 K = 0;

#100 $stop;

end

always #50 clk = ~clk;

endmodule

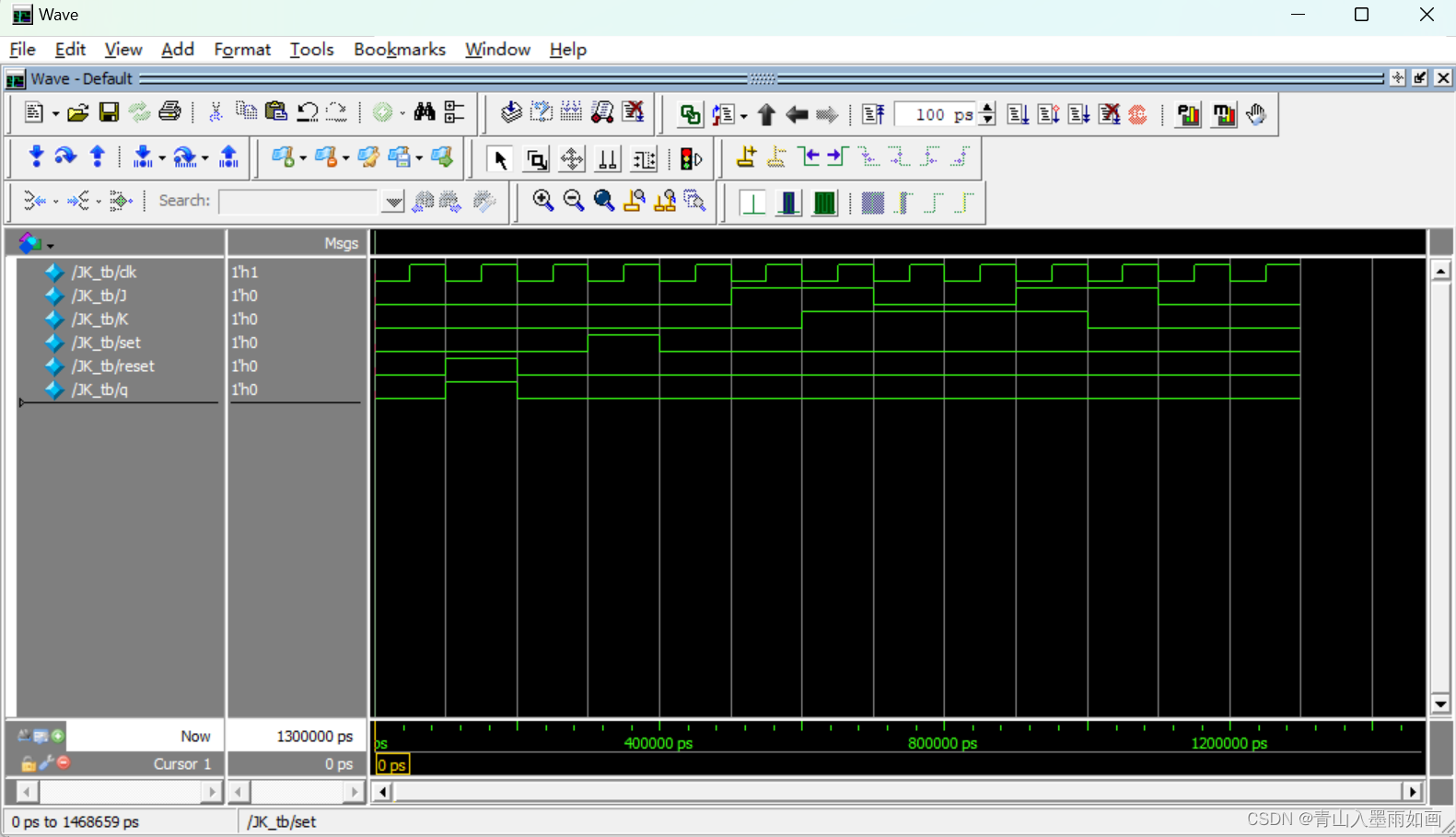

二.仿真结果

文章分享了北京邮电大学信息通信学院的数字系统设计课程中,关于JK触发器的Verilog代码实现以及相应的测试bench。内容包括JK.v模块和JK_tb.v测试bench,展示了触发器的工作原理和实验过程。

文章分享了北京邮电大学信息通信学院的数字系统设计课程中,关于JK触发器的Verilog代码实现以及相应的测试bench。内容包括JK.v模块和JK_tb.v测试bench,展示了触发器的工作原理和实验过程。

1238

1238

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?